| Atom Feed | View unanswered posts | View active topics |

It is currently 26 Apr 2024 01:57 |

|

All times are UTC - 8 hours [ DST ] |

Самодельный процессор nedoRISC-0 (NEDONAND)

Moderator: Shaos

|

|

Page 8 of 13 |

[ 193 posts ] | Go to page Previous 1 ... 5, 6, 7, 8, 9, 10, 11 ... 13 Next |

| Previous topic | Next topic |

Самодельный процессор nedoRISC-0 (NEDONAND)

| Author | Message | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

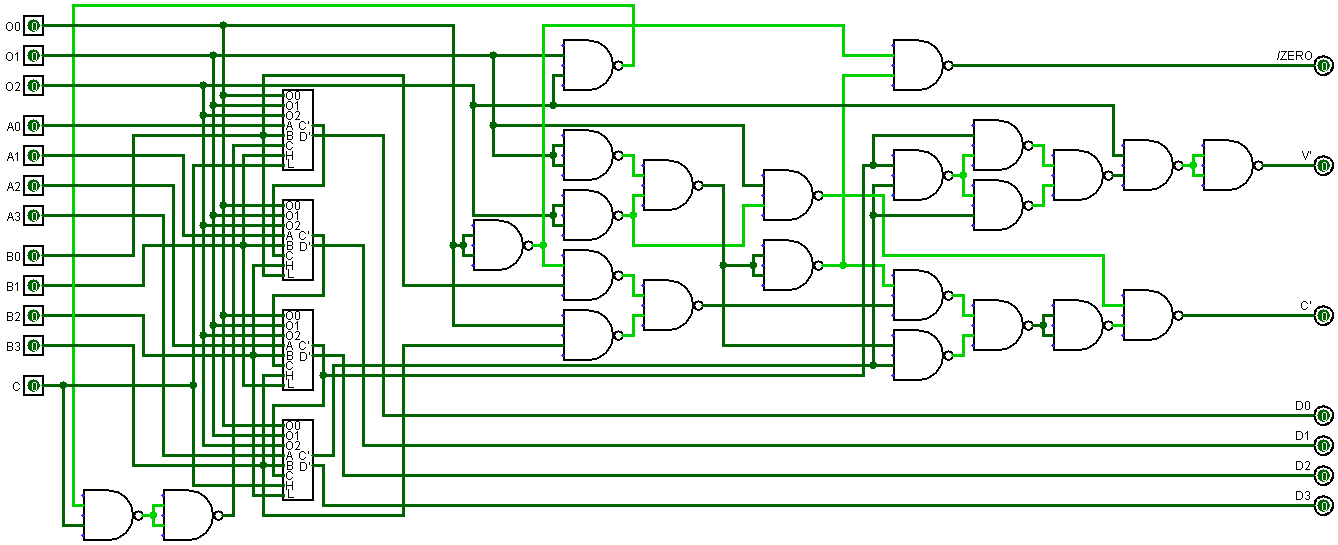

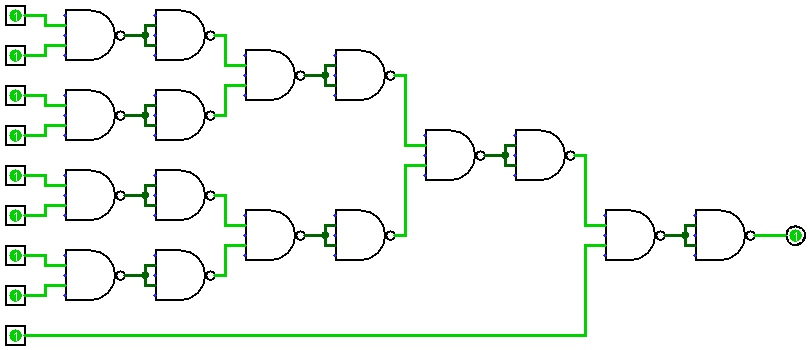

Девятая плата NEDONAND-9, которая есть 9-входовый гейт И - в nedonand.circ он называется and9:

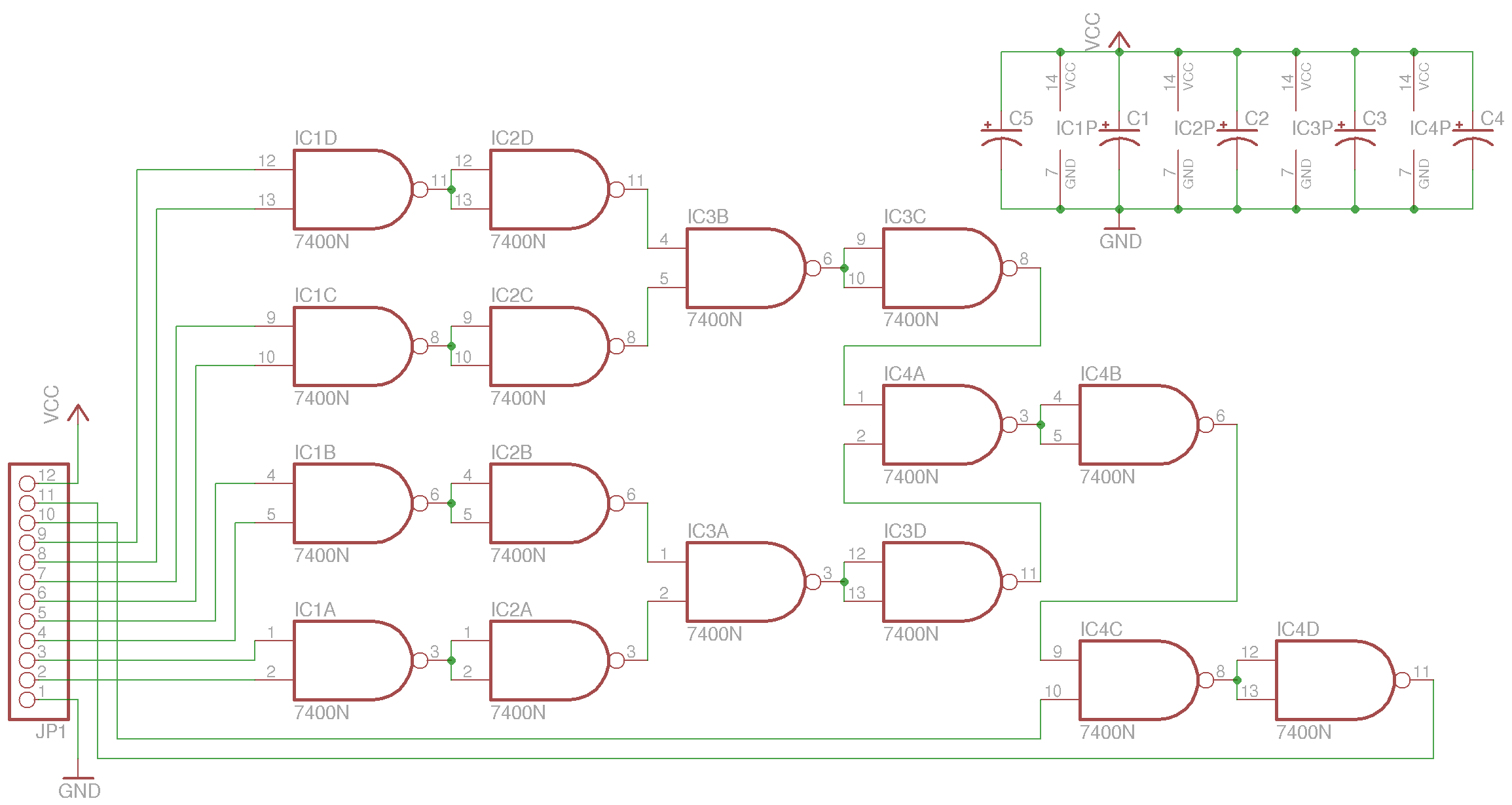

Сейчас это самая маленькая плата NEDONAND, состоящая всего из 4 микросхем 74F00:  Авторазведёнка:  Уже заказана на OSHPark:  Распиновка:

|

|||||||||||||||||||||||||||

| 27 Feb 2016 22:56 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Интерес на хакадее постепенно спадает:

|

|||||||||||||||||||||||||||

| 28 Feb 2016 05:44 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Ну что - все запланированные платки разведены и заказаны. Теперь надо решить как строить первую ступень конвейера дальше: 1) развести мамку в gEDA и заказать настоящую печатку (если что не так - резать проводники)? 2) построить на бредбордовых макетках (т.к. оно скорее всего будет меняться в будущем)? 3) собрать мамку накруткой (wire-wrap)? Пошаговый план до конца 2016 года пока такой: - сначала первая ступень конвейера c 16-байтовым ПЗУ на диодах и 7-сегментные индикаторы подцепленные к регистрам A,B,C,D,E (как в симуляции Logisim); - далее добавить память до 128 байт (тоже на диодах) и RET/RST+SAEFF/SANFF; - потом приделать вторую ступень конвейера с ALU (сначала в Logisim, потом вживую) и немного ОЗУ (подменив F=~F и F=G); - подключить РФ2 с 2К ПЗУ команд и ОЗУ до 64Кб на основе которого можно будет приделать вывод на TV или VGA. Параллельно можно потихоньку писать GPL-ный ассемблер и эмулятор (онлайн?)... |

|||||||||||||||||||||||||||

| 28 Feb 2016 08:12 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

2) построить на бредбордовых макетках (т.к. оно скорее всего будет меняться в будущем)

Даже я проникся, что это удобно и купил себе уже три, хотя после первой за 750 р они у нас последовательно стали 950 р и 1150 р. Но - реально удобно... _________________ iLavr |

|||||||||||||||||||||||||||

| 28 Feb 2016 08:27 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

с бредбордами всё хорошо, пока собираемое достаточно простое - с некоторого момента начинается такая путаница в проводах, что обратно восстановить схему по пучкам практически невозможно... |

|||||||||||||||||||||||||||

| 28 Feb 2016 08:45 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Ну так рисуй, чего собираешь на бредборде. По накруткам и по резаной-паяной плате восстановить схему ничуть не легче, на мой взгляд... _________________ iLavr |

|||||||||||||||||||||||||||

| 28 Feb 2016 08:54 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Ну тут играет роль тот момент, что поправить (или испортить) очень просто - переткнул провод и всё, а таже накрутка подразумевает предварительную работу с рисованием схемы, отмечанием галочкой проводков которые уже кинул и т.д. Хотя наверное да - намудрить можно с любым способом... |

|||||||||||||||||||||||||||

| 28 Feb 2016 09:06 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Ну да... особенно, если кидаешь шину. Тут только отмечать проводки на рисунке. И всё-равно бывает, можно сбиться, сдвинуться на один, что замечаешь в конце, и это особо обидно... _________________ iLavr |

|||||||||||||||||||||||||||

| 28 Feb 2016 10:41 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Может особо не мудрствовать и подцепить 2 такие платки параллельно, сделав 8-битный АЛУ? Тут даже в младшую половинку как минимум одну микросхемку можно не впаивать (IC4, которая флаг V формирует т.к. нас интересует V только из старшей половинки), т.е. 8-битное АЛУ займёт не 2*29=58 корпусов, а 57 и самая длительная задержка, вызванная последовательным распостранением переноса через 8 двоичных разрядов, не должна быть дольше 400 нс, а это вполне соотносится со скоростью вычитки из РФ2. Вообще, наверное всё равно можно прикинуть схемку обвязки 4-битного АЛУ, чтоб он обрабатывал 8-битные данные, и если окажется, что она тяжелее 28 микросхем, то наверное так и сделаю - поставлю два 4-битных АЛУ параллельно... |

|||||||||||||||||||||||||||

| 28 Feb 2016 13:36 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

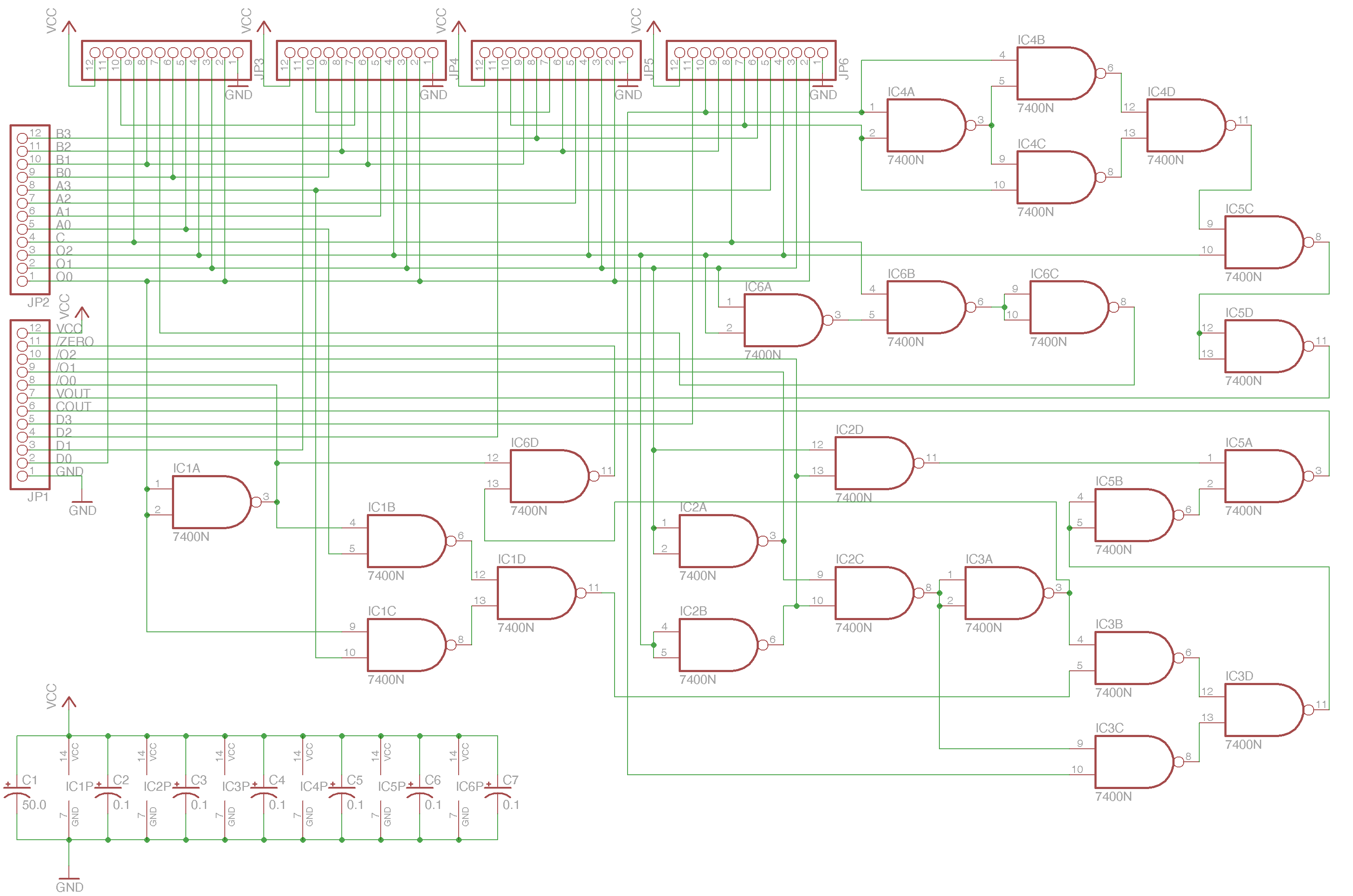

Видимо "slow ALU" небудет (во всяком случае пока), т.е. "fast ALU" уже достаточно медленный, чтобы вместить в себя операции сложения и вычитания:

Стробы второй ступени: HALF1 - это подача на вход АЛУ младшего ниббла аргументов (в случае RRC - старшего); ASTO1 - сохранение младшего ниббла аккумулятора (в случае RRC - старшего) и флага H; HALS2 - это подача на вход АЛУ старшего ниббла аргументов (в случае RRC - младшего); ASTO2 - сохранение старшего ниббла аккумулятора (в случае RRC - младшего) и флагов C,V,Z и S. По результатам своей работы первая ступень должна сохранить для второй: - 1 бит признака использования АЛУ (в случае регистровых операций вторая ступень должна простаивать); - 3 бита кода операции АЛУ; - 8 бит (прямых или инверсных) второго аргумента (регистр или часть инструкции). Половинки регистра A всегда будут читаться или писаться как есть - т.е. если следом за A=A+1 идет скажем инструкция G=A, то в результате G получит не A+1, а старшие 4 бита из старого значения A и младшие 4 бита из нового (т.е. неправильное значение в случае переноса из младшего ниббла в старший)... P.S. Блин, в случае операций сдвига (RRC/RLC) "второй аргумент" это "первый аргумент" т.е. первым аргументом не всегда является аккумулятор как я предполагал - придётся резать плату NEDONAND-4 либо переставлять аргументы логикой, зависящей от кода операции... P.P.S. Решил в результате переделать плату NEDONAND-4 и перезаказать... |

|||||||||||||||||||||||||||

| 29 Feb 2016 21:49 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Поправил, слегка расширив функционал - теперь надо переделать и перезаказать платку NEDONAND-4... |

|||||||||||||||||||||||||||

| 01 Mar 2016 00:26 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

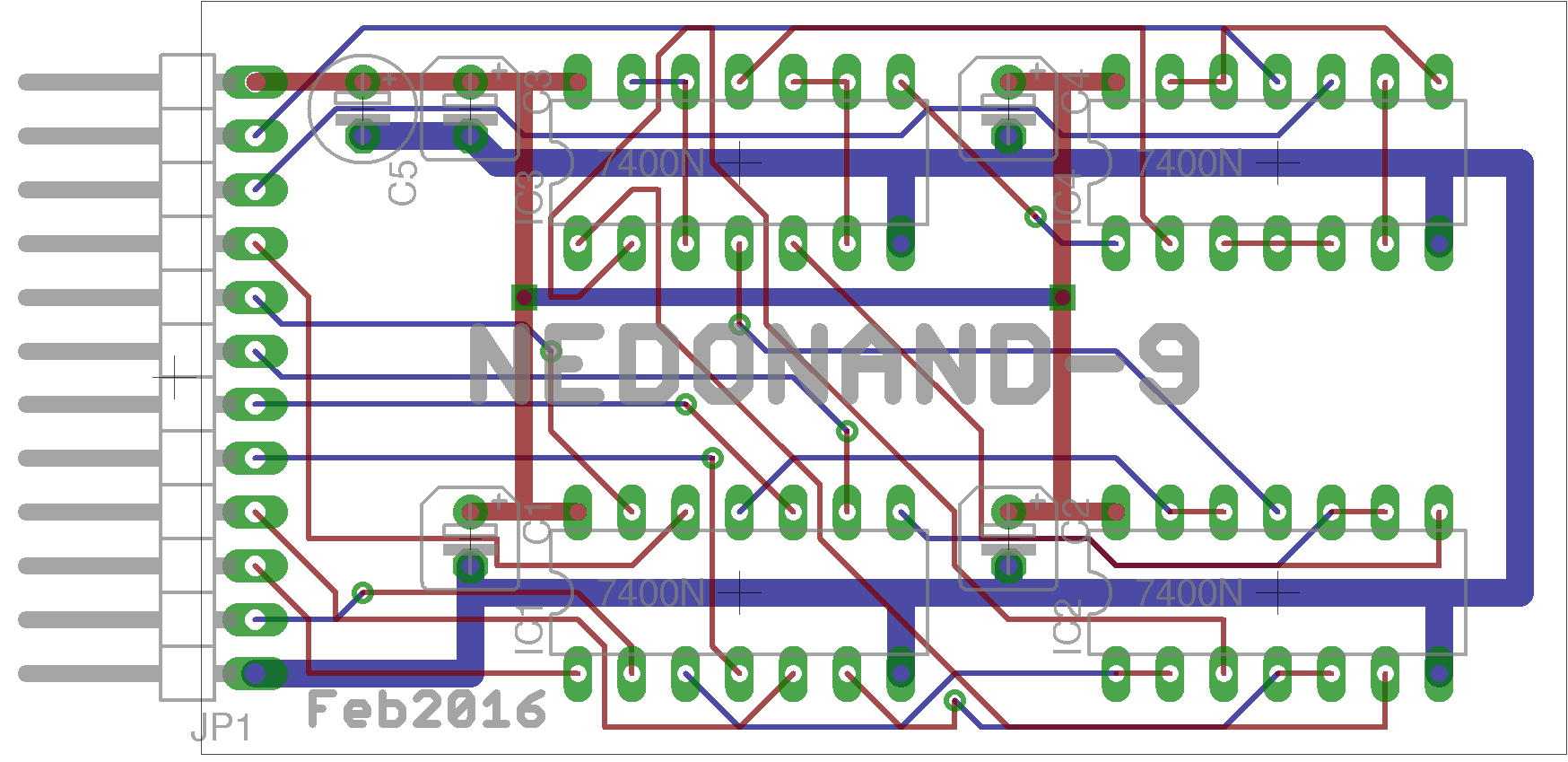

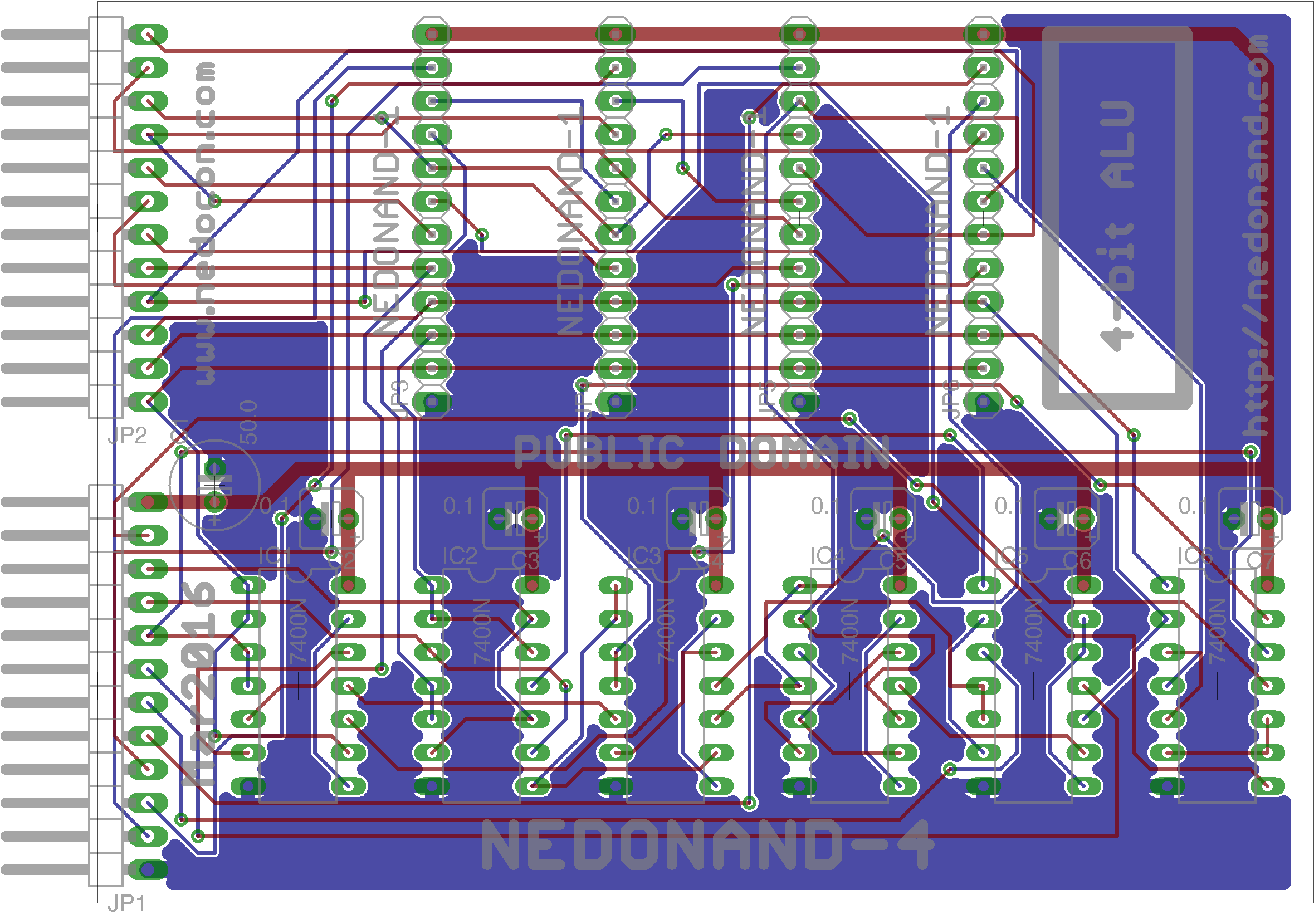

По-быстрому переделал NEDONAND-4 (см. eagle-nedonand.zip):

Развёл автороутером (всё кроме цепей питания, которые нарисовал вручную):  И перезаказал:  Распиновка:

|

|||||||||||||||||||||||||||

| 01 Mar 2016 01:58 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Вот пример инкремента регистровой пары DE:

8 циклов, причём только 2 из них используют вторую ступень конвейера, а в остальные 6 (NOP-ы могут быть заменены на другие более полезные команды, не задевающие аккумулятор) АЛУ может быть задействовано для чего-нибудь ещё. Чуть раньше я думал, что пока АЛУ простаивает, то можно аппаратно организовать копирование спрайтов в видеопамяти через АЛУ, делая XOR. Потом я предположил, что было бы неплохо делать какие-то многотактовые вычисления паралелльно с основной программой - например умножение. А сегодня мне в голову пришла мысль, что одно и то же АЛУ могут разделять 2, а то и 3 процессора! Эдакий недо-гипер-трединг получается P.S. По идее второй и третий процы могут быть проще - не иметь RET/RST и SAEFF/SANFF и скажем ограничиваться 256 байт памяти программ - т.е. получаются некие микрокодовые сопроцессоры для несложных задач (типа того же копирования српайтов в видеопамять или вычисления умножений/делений)... |

|||||||||||||||||||||||||||

| 01 Mar 2016 18:23 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Но многокоровность наверное надо отложить на потом, а так получилось бы весело - первая кора получает АЛУ всегда, вторая - только когда АЛУ не занят первой, а третья - только когда АЛУ не занят ни первой, ни второй корами - т.е. третья кора будет пропускать больше циклов и работать меньше всех, именно поэтому туда надо выносить какие-то второстепенные циклические задачи как-то заполнение видеопамяти, отрисовка спрайтов, вычисление умножений и делений и т.д.

|

|||||||||||||||||||||||||||

| 02 Mar 2016 05:47 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Тем не менее со дня на день должны прийти три "неправильные" платки NEDONAND-4, заказанные мной ранее, на которых всё же можно потестить большинство функционала АЛУ (разве что придётся тестировать сдвиги через входы A, а не через B, ну и флаг C задавать для всех операций сложения 1xxx). Потестить можно например путём подсоединения к этой NEDONAND-4 (с воткнутыми в неё четырьмя NEDONAND-3) платы с пиком nedoCPU-16, используемой в качестве тестового прибора, задающего входные воздействия и анализирующего выходы на правильность и скорость срабатывания (придётся немножко плату подковырять, подрезав несколько дорожек и бросив несколько проводков):

|

|||||||||||||||||||||||||||

| 02 Mar 2016 15:01 |

|

|||||||||||||||||||||||||||

|

|

Page 8 of 13 |

[ 193 posts ] | Go to page Previous 1 ... 5, 6, 7, 8, 9, 10, 11 ... 13 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 118 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |