| Atom Feed | View unanswered posts | View active topics |

It is currently 24 Apr 2024 04:24 |

|

All times are UTC - 8 hours [ DST ] |

Микрокодовое ядро на ПЗУ (nedoPC-27)

Moderator: Shaos

|

|

Page 2 of 3 |

[ 31 posts ] | Go to page Previous 1, 2, 3 Next |

| Previous topic | Next topic |

Микрокодовое ядро на ПЗУ (nedoPC-27)

| Author | Message | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Devil

Joined: 26 May 2003 06:57 Posts: 860 |

Для начала, попробуй написать процедуры сложения и вычитания 32-разрядных чисел. Конечно, можно табличкой сделать, но если складывать байты, то получится таблица на 65536 значений, а ещё и перенос нужно учитывать. Можно и побитно складывать, но тогда нужны команды работы с битами. А если нет инкремента/декремента и номер бита указывается прямо в команде, то представляю, насколько длинная будет эта процедура... |

||||||||||||||||||||||||||||||||||||

| 15 Sep 2010 23:30 |

|

||||||||||||||||||||||||||||||||||||

|

Devil

Joined: 26 May 2003 06:57 Posts: 860 |

По сути, твой процессор будет эмулятором обычной логики, и сумматор получится такой-же огромный, как и на обычной логике.

|

||||||||||||||||||||||||||||||||||||

| 15 Sep 2010 23:34 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

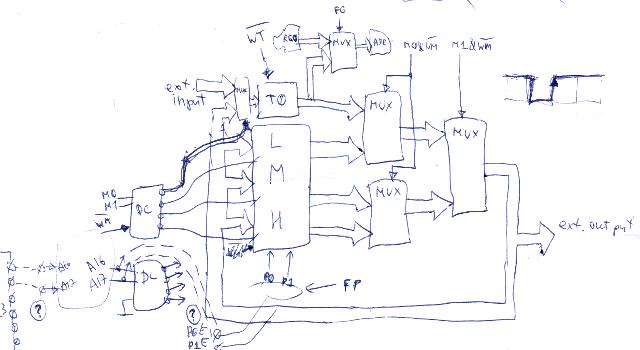

На то она и базовая конфигурация, чтобы быть неоптимальной

По сути железяки - в базовой конфигурации мы имеем 4 ПЗУ-хи, к выходам которых подключены 4 8-битных регистра - RM0, RM1, RM2 и RM3. Первые два - адрес следующей микрокоманды, RM2 - 8 битов управления (M0,M1,/WM,/WT,P0,P1,FP,FG), RM3 - 8 бит идущих на внешний разъём. Также есть регистр общего назначения RT0 и оперативная память, состоящая из 4 24-битных регистров, 8-битные части которых могут быть записаны значением из RT0, также как и RT0 может быть записан значением из любой 8-битной части этой памяти. Всего получается, что у нас имеется 13 однобайтных регистров для хранения данных. По умолчанию мы имеем следующие входы: - 8 внешних сигналов, которые могут идти на 8-битиный регистр RT0 (в базовой конфигурации можно перемычками подсоединить к RM3); - 2 внешних сигнала, которые могут выбирать какой из 24-битных регистров подключен к выходу оперативной памяти (если FP=1); - 2 сигнала, сохраняемых для следующего такта. И выходы: - 24 сигнала, которые выводят значения из выбранного 24-битного регистра оперативной памяти (может быть использовано как адрес внешней памяти); - 8 сигналов, которые просто выводят внутреннюю шину данных наружу (сюда может быть подано значение с любого из 13 однобайтных регистров девайса); - 2 сигнала, сохранённых на предыдущем такте; - 4 сигнала выбора, дешифрованных из предыдущих двух (половинка дешифратора всё равно оставалась - так я её решил заюзать). Описание битов управления: биты 0 и 1 - сигналы M0 и M1, управляющие тем, какой из трёх 8-битных частей выбранного 24-битного регистра используется на чтение или запись (M0=0 M1=0 является специальным случаем, при котором RT0 запитывается от внешнего входа данных); бит 2 - сигнал /WM, сигнализирующий о том, что оперативная память должна быть записана значением из RT0 по окончанию текущего такта (не для случая, когда M0=0 и M1=0); бит 3 - сигнал /WT, сигнализирующий о том, что регистр RT0 должен быть записан значением с внутренней шины данных либо со внешнего входа данных (источник управляется сигналами M0 и M1) по окончанию текущего такта; биты 4 и 5 - сигналы P0 и P1, управляющие тем, какой из 24-битных регистров подключен к выходам оперативной памяти (если FP=0); бит 6 - сигнал FP, управляющий тем, какие два сигнала P0/P1 используются для выбора 24-битного регистра из четырёх - внутренние (0) или внешние (1); бит 7 - сигнал FG, управляющий тем, откуда должен браться младший байт адреса следующей микрокоманды - из регистра RM0 (0) или из регистра RT0 (1). |

||||||||||||||||||||||||||||||||||||

| 16 Sep 2010 06:43 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Я вот думаю - стОит ли цеплять ПЗУ ?

Все "самогонные" компьютерщики пишут, что ПЗУ обычно зело тормозит по скорости. Может на дешифраторах и диодах микрокод забить ? |

||||||||||||||||||||||||||||||||||||

| 21 Sep 2010 06:54 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

И "перепрограммировать" его перепайкой диодов? Я для начала более цивилизованным путём пойду... |

||||||||||||||||||||||||||||||||||||

| 21 Sep 2010 19:42 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

Базовая конфигурация может: - читать извне 1 байт и записывать его в регистр RT0; - записывать 1 байт в RT0 из любого из 12 регистров; - записывать 1 байт из RT0 в любой из 12 регистров; - передавать управление на адрес, младший байт которого берётся из RT0; - выдавать 3 байта от любой тройки регистров из четырёх в соответствии с внешней или внутренней парой битов управления страницами (P0 и P1) как одно 24-битное слово, которое можно использовать как адрес для внешней памяти. P.S. Прицепив регистр RM3 к внешнему входу получим возможность микрокомандой записывать значения в RT0 (а значит и в любой другой регистр). P.P.S. Прицепив 2 сигнала сохранённых на предыдущем такте (это могут быть две кнопки) как внешние P0/P1, мы получим возможность управлять системой даже в базовой конфигурации. Last edited by Shaos on 23 Jun 2011 19:46, edited 4 times in total. |

||||||||||||||||||||||||||||||||||||

| 21 Sep 2010 20:32 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

А пока ты не паяешь - мне кажется пофигу какой путь. У меня в "Электронном_верстаке" ПЗУ не было - я так их и слепил на диодах и DC - у одного "самогонного" мужика видел - он так заменил 2 штуки РФ5, причём - говорит - прямо в панельках, и не паяя, чему я дюже удивился... Чтож у него в панельках "цветник из диодов" был штоль... |

||||||||||||||||||||||||||||||||||||

| 22 Sep 2010 02:41 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

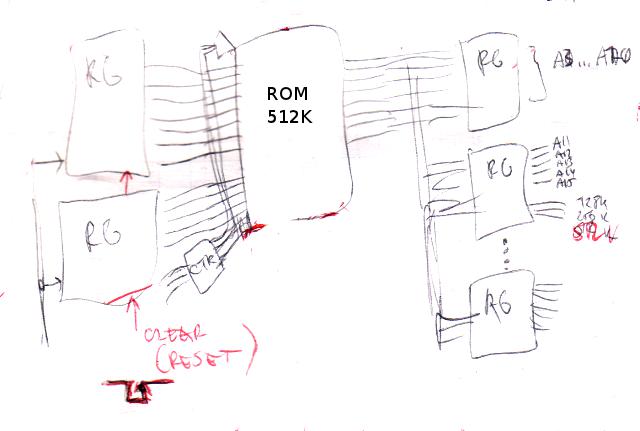

Через 9 месяцев сунул таки тетрадку в сканер, а то уже забывать стал чего собственно хотел... вот первоначальная идея - выходные регистры (8 штук) заполняются байтами микрокода из большого ПЗУ - соответственно каждая микрокоманда занимает 8 тактов:

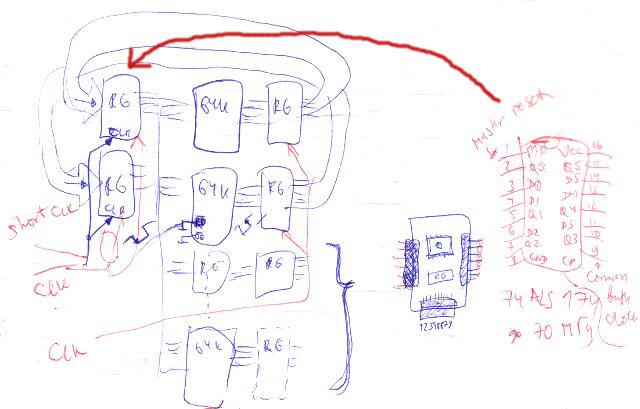

вот второй вариант - микрокод уже разбит на маленькие ПЗУ по 64К - соответственно можем наращивать ширину микрокоманды как угодно:

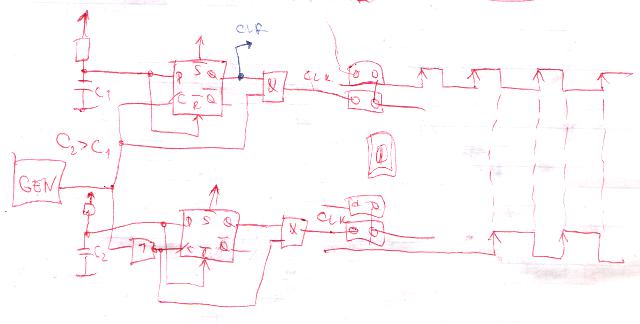

для тактирования входных регистров адреса и выходных регистров микрокоманды используются две тактовые частоты, причём раньше должна появится частота, идущая на выходные регистры:

вот блок-схема файла регистров с данными:

всё-таки думаю начать с первого варианта - там где один ПЗУ из которого байты микрокоманды выдаются последовательно и запоминаются на соответствующих регистрах а дальнейший вариант - всё-таки не с кучей ПЗУ, а с одной большой, из которой при включении микропрограммы заливаются в ряд состоящий из произвольного количества ОЗУ и уже оттуда оно работает |

||||||||||||||||||||||||||||||||||||

| 13 Jun 2011 21:05 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

Вариант нарезки регистров для эмуляции i8080:

M0L0=PC M1L1=SP M2L2=DE M3L3=HL H0=F H1=A H2=B H3=C Внешняя память подключена к выходам M и L P.S. L это когда M1=0 M0=1, M это когда M1=1 M0=0, H это когда M1=1 M0=1. Цифра после буквы задаётся сигналами P0 и P1. |

||||||||||||||||||||||||||||||||||||

| 16 Jun 2011 19:13 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

Вариант нарезки регистров для эмуляции MOS6502:

M0L0=PC M1=0x10 L1=S M2=F L2=A M3L3=XY H0=? H1=? H2=? H3=? Last edited by Shaos on 02 Oct 2012 16:27, edited 1 time in total. |

||||||||||||||||||||||||||||||||||||

| 16 Jun 2011 21:10 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

прикинул, что с минимальным внешним обвесом эту конструкцию можно превратить в эмулятор 8080 - причём АЛУ будет "эмулироваться" прямо в памяти микропрограмм - унарные операции будут выполняться над 8-битными данными, а бинарные (с двумя аргументами) над 4-битными (путём передачи управления на адрес в зависимости от значения в регистре RT0) |

||||||||||||||||||||||||||||||||||||

| 21 Jun 2011 22:03 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

а можно снаружи прицепить 74180-е и 74181-е, т.е. сделать настоящее 8-битное АЛУ - будет быстрее работать... |

||||||||||||||||||||||||||||||||||||

| 23 Jun 2011 19:32 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

Вот например задача для опробования базовой конфигурации: 16-битный счётчик, который считает вперёд, если нажать на первую кнопку, и назад, если на вторую. Индикация светодиодами, подключёнными к шине внешнего адреса - 24 сигнала из которых мы будем смотреть на младшие 16. Счётчик при включении питания обнуляется. Микропрограмма обнуления всех регистров:

Будем использовать регистры H0,H1,H2,H3 как маркеры того, какая кнопка нажата:

Если нажаты обе кнопки, то программа должна будет думать, что нажата только вторая. |

||||||||||||||||||||||||||||||||||||

| 23 Jun 2011 19:52 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

Для единообразия думаю надо убрать инверсные сигналы, чтобы неактивное состояние соответствовало нулю, т.е. биты управления будут следующими: Bit 0: M0 \ Bit 1: M1 - два бита адресующих регистры внутренней памяти (RLx,RMx,RHx) либо RT0 Bit 2: WM - запись содержимого RT0 в память по выбранному адресу M0/M1 Bit 3: WT - запись в регистр RT0 (при M0=0 M1=0 WM=1 происходит запись из внешнего порта) Bit 4: P0 \ Bit 5: P1 - два бита адресующих страницу регистров внутренней памяти Bit 6: FP - сигнал использования внешних P0/P1 вместо внутренних (биты 4 и 5) Bit 7: FG - сигнал записи содержимого RT0 в младший байт адреса следующей команды Теперь можно писать ассемблер этого дела P.S. Вот список возможных микрокодов базовой конфигурации (добавил возможность оперировать ещё одним регистром RT1 в командах с пометкой NEW):

P.S. В будущих версиях можно добавить ещё три внешних порта и заюзать для их чтения команды #YD,#YE,#YF (которые сейчас использовать не рекомендуется). |

||||||||||||||||||||||||||||||||||||

| 02 Oct 2012 13:45 |

|

||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22568 Location: Silicon Valley |

Первая версия схемы (с одним ПЗУ и 8-шаговым тактированием) полностью набросана на бумажке - теперь осталось накидать её в Eagle и заказать платку (на макетке наверное будет тяжеловасто городить прототип)...

|

||||||||||||||||||||||||||||||||||||

| 02 Oct 2012 18:55 |

|

||||||||||||||||||||||||||||||||||||

|

|

Page 2 of 3 |

[ 31 posts ] | Go to page Previous 1, 2, 3 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 32 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |