| Atom Feed | View unanswered posts | View active topics |

It is currently 19 Apr 2024 06:19 |

|

All times are UTC - 8 hours [ DST ] |

а не замутить ли нам недосимулятр?

Moderator: Shaos

|

|

Page 8 of 16 |

[ 235 posts ] | Go to page Previous 1 ... 5, 6, 7, 8, 9, 10, 11 ... 16 Next |

| Previous topic | Next topic |

а не замутить ли нам недосимулятр?

| Author | Message | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

bar, ты приватные сообщения никогда не читаешь?

P.S. я на старой работе лет эдак 14 назад делал симулятор функциональных блоков (по сути схемный ввод абстрактных алгоритмов) и компилятор из графического представления этих блоков в си тоже делал - так что могу на пальцах обрисовать все возможные подводные камни - начиная от путей избегания зацикливания симулирующего алгоритма и кончая автоматической отрисовкой непекрывающихся соединений между компонентами |

|||||||||||||||||||||||||||

| 10 Sep 2012 20:22 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

Это по-моему не требует особых "путей". По одному биту на каждый элемент, значения которых одинаковы перед началом очередной итерации симуляции, и которые инвертируются к концу этой самой итерации.

|

|||||||||||||||||||||||||||

| 10 Sep 2012 20:46 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

Это если надо будет автоматически рисовать соединения между компонентами (не вручную), то я знаю как сделать проще P.S. А в каком порядке будет происходить твоя итерация симуляции? |

|||||||||||||||||||||||||||

| 10 Sep 2012 20:51 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

Короче, если я правильно всё понимаю, порядок обхода не влияет на выбор структур данных. А раз так, то и какая на данном этапе разница? |

|||||||||||||||||||||||||||

| 11 Sep 2012 16:33 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

Порядок обхода влияет на правильность и скорость работы схемы. Во-первых, т.к. у нас во всех соединениях один источник и много приёмников, то логично у входов компонентов указывать к чему они подключаются - к выходам других компонетов либо ко входам схемы, а выходы схемы также внутри себя содержат информацию о том, к чему они подключены. Во-вторых, в произвольном порядке схему исполнять нельзя (будут непредвиденные задержки в распостранении сигнала и вообще неправильная работа) - перед симуляцией соединения надо упорядочить, для чего список всех доступных соединений сортируется так, что в начало списка попадают входы схемы и далее по слоям до выходов. Чтобы исключать зацикливания при сортировке надо ввести ещё один параметр соединения - местоположение приёмника по горизонтали - если приёмник находится левее источника, то это трактуется как обратная связь (задержка в 1 такт на распостранение сигнала) и это соединение при сортировке игнорируется (точнее трактуется как обычный вход схемы).

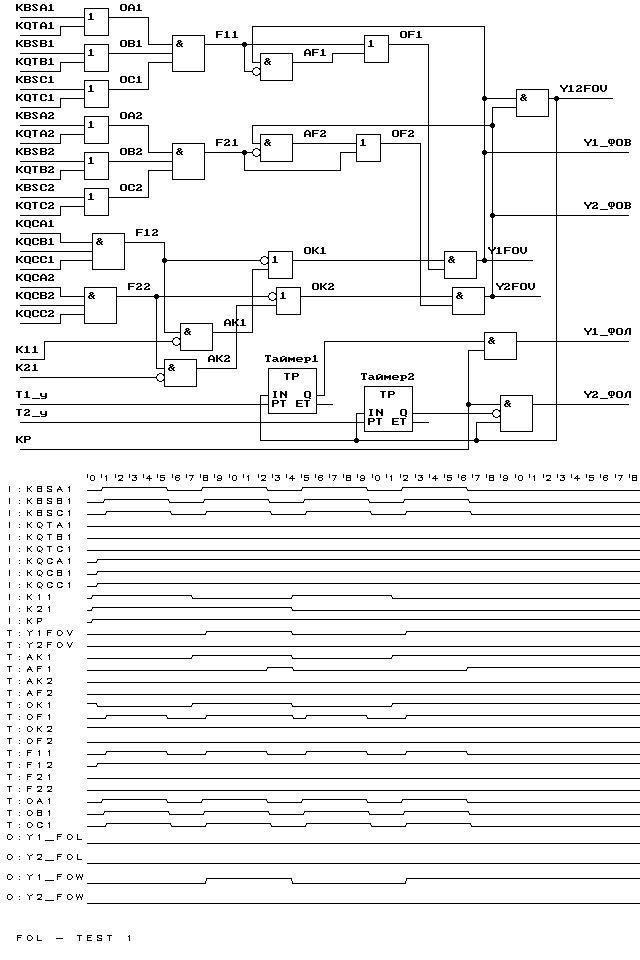

По поводу отрисовки - у каждого компонента входы располагаются слева, а выходы справа. К каждому входу пририсовываем смотрящий влево отрезок длиной, равной порядковому номеру входа - к первому длиной 1, ко второму длиной 2 и т.д. Со входами делаем тоже самое, но отрезки будут смотреть вправо. В результате у нас получается эдакая ёлочка. Теперь очень просто рисовать соединения между нужными цепями - считаем что соединения всегда состоят из трёх сегментов - вертикального, горизонтального и опять вертикального - т.е. это может быть подобие буквы П либо Ц либо нечто среднее - просто перебираем все варианты двигаясь всё дальше и дальше, находя такую отрисовку, при которой соединение не будет перекрывать никаких других компонентов и не будет лежать поверх соединений того же самого направления, причём если окажется, что мы по ходу уже пересеклись с нужной цепью то на ней и останавливаемся, ставя жирную точку в месте соединения. При этом мы добъёмся полностью автоматического соединения компонентов, расставленных вручную - выглядеть это будет примерно так:  При компиляции в C++ это превращалось вот в такой класс с методом step (один шаг симуляции):

Так что у меня был как интерпретатор схемы, так и компилятор Кстати при интерпретации можно было записывать "осциллограммы":  Теперь я хочу соорудить нечто подобное, но на си и опенсорцное |

|||||||||||||||||||||||||||

| 11 Sep 2012 18:05 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

А. Я понял к чему это. Это если состояние выходов элемента -- функция его входов и времени, так? Про время в качестве параметра я не подумал. И почему-то был уверен, что у нас время будет измерятся в количестве итераций симуляции. Ведь для того, чтобы все сигналы появлялись в нужной последовательности, то, при условии что произвольный элемент, в произвольный момент времени, без внешних видимых причин, может вдруг изменить состояние своих выходов... При этом условии, придётся реализовывать (или симулировать) нечто типа "на каждый элемент по real-time thread'у". Просимулировать это вполне возможно, создав очередь "будущих" событий, отсортированную по возрастанию времени до наступления этих событий. М-м-м... Может именно для этого cedar'овский симулятор логики использует очереди событий? Я заглядывал туда, у него там, судя по всему свои события и свои очереди функционирующие вне зависимости от работы очереди gui событий.

Да, у меня в голове крутилось нечто чуть более сложное. Ну да, с туманными перспективами получения лучшего результата, но и более сложное. Пожалуй KISS тут будет кстати. |

|||||||||||||||||||||||||||

| 11 Sep 2012 21:27 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

Неа - как раз время измеряется в количестве итераций симуляции. Функция step схемы перебирает все компоненты, вызывая у них свои функции step. Просто в зависимости от порядка перебора результаты могут различаться или быть вовсе неправильными - например: имеем вход A и 3 выхода - B,C,D. Выход B подключен к входу A через один инвертор I1, выход C подключен к выходу инвертора I1 через инвертор I2, выход D подключен к выходу инвертора I2 через инвертор I3. Предположим, что мы посылаем на вход последовательность 01010101. Вот что выдаст упорядоченная симуляция (считаем, что изначально все выходы обнулены):

А вот что сгенерит неправильная последовательность обхода:

Как видишь результат "симуляции" выглядит совершенно иначе из-за того что у нас имеется трёхступенчатая обратная связь - правильный сигнал доходит до выхода за три такта и если период изменений нашего входного сигнала меньше времени задержки, то могут получатся наложения и неправильная работа симуляции, а если больше - то просто 3-тактовая задержка в распостранении сигнала... Last edited by Shaos on 12 Sep 2012 22:31, edited 1 time in total. |

|||||||||||||||||||||||||||

| 11 Sep 2012 21:46 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

Я может тупой очень... Но чесслово, я долго думал и очень старался. И так и не понял, как эта схема должна выглядеть. То есть во-первых, там по-моему опечатка, наверное так надо(?):

|

|||||||||||||||||||||||||||

| 12 Sep 2012 22:24 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

Ага - поправил Обратная связь получается если эти блоки в неправильном порядке вызывать... |

|||||||||||||||||||||||||||

| 12 Sep 2012 22:32 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

Но я, кажется, понял таки о чём речь.

Все элементы мы раскидываем по непересекающимся множествам -- слоям. Слой #0 состоит из входов. Слой #N состоит из элементов, от которых длина кратчайшего пути до слоя входов равна N. Говоря путь я имею в виду путь в графе, с вершинами -- элементами схемы, и рёбрами-соединениями между элементами. И обход оказывается таким:

|

|||||||||||||||||||||||||||

| 12 Sep 2012 23:09 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

Ну кратчайший путь от любого слоя до входа схемы может составлять 0 если вход схемы подключается к какому-то входу компонента в слое напрямую

P.S. А зачем отдельно выделять такую абстракцию как слои? Просто компоненты упорядочены в списке и при шаге симуляции мы просто идём по списку, вызывая у каждого компонента метод step (причём компоненты внутри себя также могут содержать списки своих внутренних компонентов, у которых тоже дёргается step) |

|||||||||||||||||||||||||||

| 12 Sep 2012 23:24 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

Да, точно. Только не ноль, а один: я входы схемы тоже считаю вершинами графа. Значит не кратчайший, а длиннейший путь. Но без циклов.

|

|||||||||||||||||||||||||||

| 13 Sep 2012 01:10 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

Кстати мой подход с учётом координаты X имеет изъяны - например классическая схема триггера с ходу не заработает - придётся разнести элементы по горизонтали, чтобы обратная связь была только одна, а не две. Так что наверное я возьму на вооружение совет bara - при обходе метить блоки и если пришли к уже отмеченному, то это цикл и его надо разорвать - другой вопрос что надо аккуратнее выбирать место разрыва, чтобы как можно меньше сигналов задерживалось на 1 такт...

|

|||||||||||||||||||||||||||

| 13 Sep 2012 06:37 |

|

|||||||||||||||||||||||||||

|

Senior

Joined: 07 Aug 2006 10:18 Posts: 185 |

У меня мысль-то была примерно такая. Поделить всё множество элементов на три непересекающихся подмножества: 1. обработанные на текущей итерации 2. находящиеся на расстоянии 1 от обработанных 3. все остальные И перенос элемента из 2 в один (как мне казалось) возможен лишь в одной ситуации: если все элементы на расстоянии -1 от данного уже обработаны. (я не знаю, насколько нормально использовать отрицательные расстояния в орграфах, но напрашивается). Дык вот неверно это. В случае если мы пытаемся обработать rs-триггер нам придётся помечать один из И-НЕ как помеченный, несмотря на то, что его состояние зависит от ещё не помеченного второго И-НЕ. То есть мои пометки, не являются решением проблему обратной связи. Что наводит на вопрос целесообразности этих самых меток. Тут как раз нужно то самое понятие "уровня", то есть расстояния от входов. Если элемент зависим от другого элемента, то это будет считаться достаточно причиной не обрабатывать его в данный момент, лишь при условии, что элемент-зависимость находится от входов на расстоянии строго меньшем, нежели расстояние данного элемента от входа. Нужен именно твой подход, только вместо "координаты X", надо использовать расстояние в графе. Которое вычислять единожды перед началом симуляции. Допустим организовав обход графа "в ширину". Этот обход в ширину можно было бы использовать и для собственно итерации, но я не вижу хорошего способа реализовать is_nearer_to_scheme_input(ELEMENT a, ELEMENT b). Конечно можно заменить один бит на один трит, и метить "насовсем" пройденные элементы значением 1, совсем не пройденные значением -1, и иметь множество помеченное значением нуль -- это элементы находящиеся на текущем уровне. Но для этого, по факту, придётся в каждый элемент заглядывать дважды. Один раз, чтобы пометить нулём, второй раз, чтобы вызывать его метод step и пометить единичкой. Вероятно при этом не удастся найти способа обойтись без предварительного обхода всех элеменотв с развешиванием на них метки -1. Хотя не, можно, просто на чётных итерациях надо будет помножать эти значения на -1. |

|||||||||||||||||||||||||||

| 13 Sep 2012 18:03 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22543 Location: Silicon Valley |

По-моему ты черезчур усложняешь...

Кстати в случае триггера оба элемента будут равноправны - и от входов они будут на одинаковом "расстоянии" - как быть в этом случае? P.S. В случае использования координаты X триггер с двумя И-НЕ, расположенных друг на другом будет просто самовозбуждаться, превращаясь в генератор... |

|||||||||||||||||||||||||||

| 13 Sep 2012 19:03 |

|

|||||||||||||||||||||||||||

|

|

Page 8 of 16 |

[ 235 posts ] | Go to page Previous 1 ... 5, 6, 7, 8, 9, 10, 11 ... 16 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 50 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |