| Atom Feed | View unanswered posts | View active topics |

It is currently 28 Apr 2024 05:23 |

|

All times are UTC - 8 hours [ DST ] |

самодельный многозадачный процессор

Moderator: Shaos

|

|

Page 2 of 5 |

[ 68 posts ] | Go to page Previous 1, 2, 3, 4, 5 Next |

| Previous topic | Next topic |

самодельный многозадачный процессор

| Author | Message | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Writer

Joined: 27 Feb 2014 05:15 Posts: 23 Location: 93.123.183.154 |

если использовать основное АЛУ (да ещё и 1 битное или с последовательным переносом) то.... 32-128 тактов на вычисление реального адреса....

придется мудрить со специальным, но 32-битный сумматор считающий, если по максимуму, [адрес начала сегмента]+[начало блока данных внутри сегмента]+[индекс]+[сравнение с адресом конца сегмента] ну и может ещё что, пока в голову не приходит вообщем это похоже будет очень долго ____________________________________________________ можно немного схитрить, объявить внешнюю шину адреса 24бит и сделать сегментирование по границам 256 байт (минус последних 8 бит), тогда складывать придется только 16бит при использовании микросхемы 555ИМ6 (SN74LS283) получится 24нс * 4 = 96нс по времени должно укладываться в 1 такт на 10МГц хм... может что и выйдет |

||||||||||||||||||

| 21 Mar 2014 04:02 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Не-е, я это рисовать не буду, мне Z80 достаточно

|

||||||||||||||||||

| 21 Mar 2014 07:14 |

|

||||||||||||||||||

|

Writer

Joined: 27 Feb 2014 05:15 Posts: 23 Location: 93.123.183.154 |

никаких сегментов в памяти, вернее там они конечно будут, но для вычисления адресов будут специальные системные регистры (пока 2 шт) с адресами сегментов программы и данных в протезусе нет чипа 74182, печаль |

||||||||||||||||||

| 22 Mar 2014 00:15 |

|

||||||||||||||||||

|

Banned Joined: 04 Jan 2013 10:09 Posts: 397 Location: 95.24.178.158 |

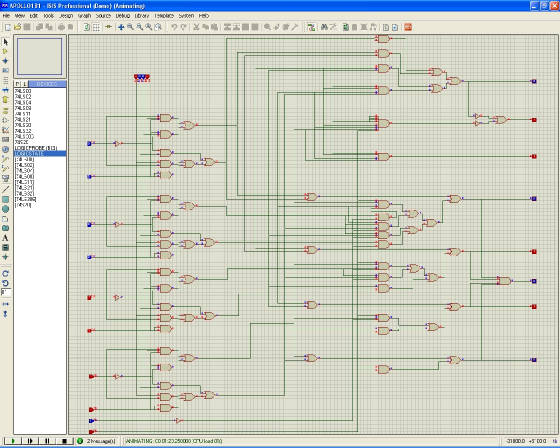

74181 - тоже не было, но можно выйти из положения с помощью "подсхемы", как вот этот итальянский автор Gianluca G.  |

||||||||||||||||||

| 22 Mar 2014 05:01 |

|

||||||||||||||||||

|

Writer

Joined: 27 Feb 2014 05:15 Posts: 23 Location: 93.123.183.154 |

можно и подсхему нарисовать, только она будет симулироваться не как отдельный чип со своими характеристиками, а как набор рассыпной логики и, например, тайминги я уже просимулировать не смогу

в справочнике время срабатывания написано покаскадно, и непонятно какое время пройдет от получения команды до выхода полного результата у комплекта 4хИП3+ИП4 |

||||||||||||||||||

| 23 Mar 2014 21:24 |

|

||||||||||||||||||

|

Banned Joined: 04 Jan 2013 10:09 Posts: 397 Location: 95.24.178.158 |

А почему нет? В протезусе они выставляются какие нужны, хоть нулевые поставьте. |

||||||||||||||||||

| 24 Mar 2014 06:11 |

|

||||||||||||||||||

|

Writer

Joined: 27 Feb 2014 05:15 Posts: 23 Location: 93.123.183.154 |

с протезусом не до конца ещё разобрался, может и смогу собрать правильную схему

но вот с уже столкнулся с тем, что схема ИП4 из Шило и 74182 из даташита не совпадают. надо сидеть и сравнивать по табличным значениям. а хотелось бы общее АЛУ на 4хИП3+ИП4 и им же считать адреса, если эта схема способна уложиться в 1 такт приемлемой частоты, а лучше чтобы этим же тактом шел запрос к памяти (не факт что получится) я правильно думаю что адрес на шине уже должен быть, перед любым обращением к памяти? |

||||||||||||||||||

| 25 Mar 2014 00:03 |

|

||||||||||||||||||

|

Doomed

Joined: 10 Mar 2012 16:21 Posts: 598 Location: РФ |

Правильно.

А книга Шило - кандидат в номинации "количество "косяков" и ошибок" среди справочников. Туда смотреть в последнюю очередь. А ещё можно посоветовать многофазную синхронизацию. |

||||||||||||||||||

| 25 Mar 2014 03:08 |

|

||||||||||||||||||

|

Writer

Joined: 27 Feb 2014 05:15 Posts: 23 Location: 93.123.183.154 |

вот тут по подробнее пожалуйста, что сие есть |

||||||||||||||||||

| 25 Mar 2014 03:37 |

|

||||||||||||||||||

|

Writer

Joined: 27 Feb 2014 05:15 Posts: 23 Location: 93.123.183.154 |

помедитировал над схемами ИП3 и ИП4 и понял что это схема с хоть и ускоренным но все-таки последовательным переносом, так что скорость выполнения 16-битного сложения будет 4*ИП3 + 3*ИП4 , что для вычисления адреса неприемлемо, а жаль

значит будет пока на ИМ6:

надеюсь хоть это правильно итого получаем 3*17+24 = 74нс если я не ошибаюсь 1 такт на 10МГц составляет 100нс |

||||||||||||||||||

| 25 Mar 2014 03:52 |

|

||||||||||||||||||

|

Doomed

Joined: 25 Aug 2009 07:02 Posts: 460 Location: Москва |

Отнюдь. Зависит от выбранного протокола обмена с памятью. Хоть признак записи-чтения сначала выставляйте, потом данные и в конце адрес. К примеру. |

||||||||||||||||||

| 25 Mar 2014 04:59 |

|

||||||||||||||||||

|

Banned Joined: 02 Feb 2014 08:29 Posts: 102 Location: Павловский Посад |

Не знаю, насколько будет по-спортивному предложить одно интересное решение - вместо хитрющей логики поставить простое ПЗУ, да побольше объемом - так поступали в узкоспециализированных БЦВМ при коммунизме.

Пример : имеется задача за 200 нс перемножить 2 шт. 8-битных числа. Решение : ставим 128 кбайт ПЗУ - на входы адреса подаётся 1-е число - 8 бит и 2-е число - 8 бит. На выходе - 16 бит ответ. Для использования 573РФ4 получалась полная плата размера корзинки ДВК. Так же можно поступить и с некотрыми специфическими функциями. Если совсем кратко - с использованием 530-й серии и 9-слотовой корзинки от Э-60 получалась производительность процессора - не менее 1 флопс - в 1988 г. * ИМХО - если расписывать процессор по конвееру - для скромного 16-бит решения запросто можно потратить месяцы или даже годы. * Правда, уже в 1992 г. стали применять J11-15 мгц, он сопоставим по производительности с приведенным примером, и на полпорядка компактнее. * Припоминаю, была попытка сделать многоплатное решение с использованием массива ОЗУшек - статики, в который прописывалось задание пользователя ( точнее, развесистый микрокод пользователя), но дальше исследовательской работы это не пошло. |

||||||||||||||||||

| 25 Mar 2014 10:40 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22615 Location: Silicon Valley |

У меня тоже было такое исследование

|

||||||||||||||||||

| 25 Mar 2014 12:03 |

|

||||||||||||||||||

|

Doomed

Joined: 10 Mar 2012 16:21 Posts: 598 Location: РФ |

Я ещё учась в школе запросто перемножал два двоичных 12-битных без-знаковых числа за те же 200нс при помощи ПЗУ-шек организованных как 8192*24 и ещё четырёх ИМС средней степени интеграции ( в "нашем" смысле средней - в "буржуинском" они считаются мелкой логикой ) ( Не подумайте никоим образом, что хвастаю, ибо кроме меня так же умели делать, пожалуй, не менее десятка тысяч советских инженеров - дело то сие вполне заурядное, если школьные формулы знать... )

Уж не "британские учоные" часом ? Не верьте им. Как же 165гф2 тактировала процессоры серии 145ик ?(риторический) Советские разработчики потратили на проектирование отнюдь не 15 и не 10 лет....... И, кстати, неважно, "скромные" 16 бит или "роскошные" 128 бит - многофазное управление процессом будет совершенно одинаковое. |

||||||||||||||||||

| 25 Mar 2014 12:14 |

|

||||||||||||||||||

|

Banned Joined: 02 Feb 2014 08:29 Posts: 102 Location: Павловский Посад |

Насчет "расписывать процессор по конвееру" - это гораздо более сложный процесс я упомянул, следует понимать как "при максимальной тактовой частоте логики" - т.е. фазное управление в принципе не рассматривается. Реально это фантастически сложный процесс - Интел его делала усилием десятка яйцеголовых ручками за 2-3 года на камешек. Однако, результат - на максимальной ( тактовой ) частоте конвееризованный процессор показывает не менее, чем 2-х кратный прирост на классических смесях команд ( при линейной подаче команд - соответственно степени конвееризации ).

Первым конвеерным был 486 - но я могу ошибаться. Не конвеерным был 386DX - 7 тактов на рег-рег. Апофеоз одноядерности в Интел - 8-параллельный Т(итаниум) - до 3-х подряд идущих ветвлений без потери крейсерской скорости - думается, со временем и господа из Израиля сцапают этот рецепт ( разработчики Коре-дуля ). * Насчет хитрости с экономией ПЗУ - не я разработчик, я просто привел пример - не стоит упускать из внимания, что готово было в 1988 г. - т.е. начали свистать с оригинала году так в 1983. К тому же я привел законченный вариант - 200 нс РФка - её не обойти ( напрямую ). Были, конечно, и масочные ТТЛШ ПЗУ - с временами менее 60 нс, но мне такие конструктивы не извесны ( т.е. готовые умножители 12 бит ). * Вот клянчил у Ю.Л. Отрохова ТО на его камень 1013ВМ1 - хрен дал ( официально ). И даже не счел нужным ( он ) упомянуть, что полно камушков без "К" - по этому и не дает ТО ( официально ) : http://forum.ixbt.com/topic.cgi?id=64:3394-153 ( Иванов И.И. = MM ) |

||||||||||||||||||

| 25 Mar 2014 14:50 |

|

||||||||||||||||||

|

|

Page 2 of 5 |

[ 68 posts ] | Go to page Previous 1, 2, 3, 4, 5 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 52 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |