| Atom Feed | View unanswered posts | View active topics |

It is currently 13 May 2024 03:38 |

|

All times are UTC - 8 hours [ DST ] |

|

|

Page 4 of 5 |

[ 62 posts ] | Go to page Previous 1, 2, 3, 4, 5 Next |

| Previous topic | Next topic |

Троичная перепрограммируемая микросхема TERNARO (TRI00)

| Author | Message | |||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Banned Joined: 29 Jun 2018 08:48 Posts: 413 |

7 трит... О_О биты - в двоичной системе. триты - в троичной. квадры - в четвертичной... |

|||||||||||||||||||||||||||||||||||||||||||||

| 28 Jul 2018 01:08 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Это гибридный девайс - управление и конфигурирование остаются двоичными, а вот после конфигурирования оно работает полностью как троичное устройство |

|||||||||||||||||||||||||||||||||||||||||||||

| 28 Jul 2018 07:15 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Banned Joined: 29 Jun 2018 08:48 Posts: 413 |

ок. тогда - да... |

|||||||||||||||||||||||||||||||||||||||||||||

| 28 Jul 2018 07:52 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Что-то подумалось мне, что надо иметь ещё один вход разрешения программирования /PRG и в конце этого сигнала (т.е. по фронту) задвинутые через SDI биты передадутся в конфигурационные ячейки и FPGA заработает. Раньше я планировал переключение из программирования в работу, когда первая единичка дойдёт до конца цепочки - т.е. надо было бы обязательно засовывать весь битстрим, чтобы работать, а с отдельным входом разрешения программирования появится возможность заводить неполный битстрим и начинать работать с ним (все недовведённые конфигурационные биты остаются нулями после ресета) - это и в отладке сильно поможет, если скажем чего-то где-то не пропечётся. Значит ногу GND можно заменить на этот /PRG (всё равно земля уже есть в виде Vneg) ну и для пущей логичности можно переставить /PRG и /RES местами (а также TA биты перевернуть):

|

|||||||||||||||||||||||||||||||||||||||||||||

| 28 Jul 2018 08:29 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Ну вот по этому я и хотел в цепочку D-триггеров (обнулённую при включении через /RES) засунуть сначала "лишнюю" единичку, а потом уже сам битстрим бит за битом от конца к началу - как только первая единичка выплюнется из SDO - значит все битики встали на свои места и полное программирование закончено

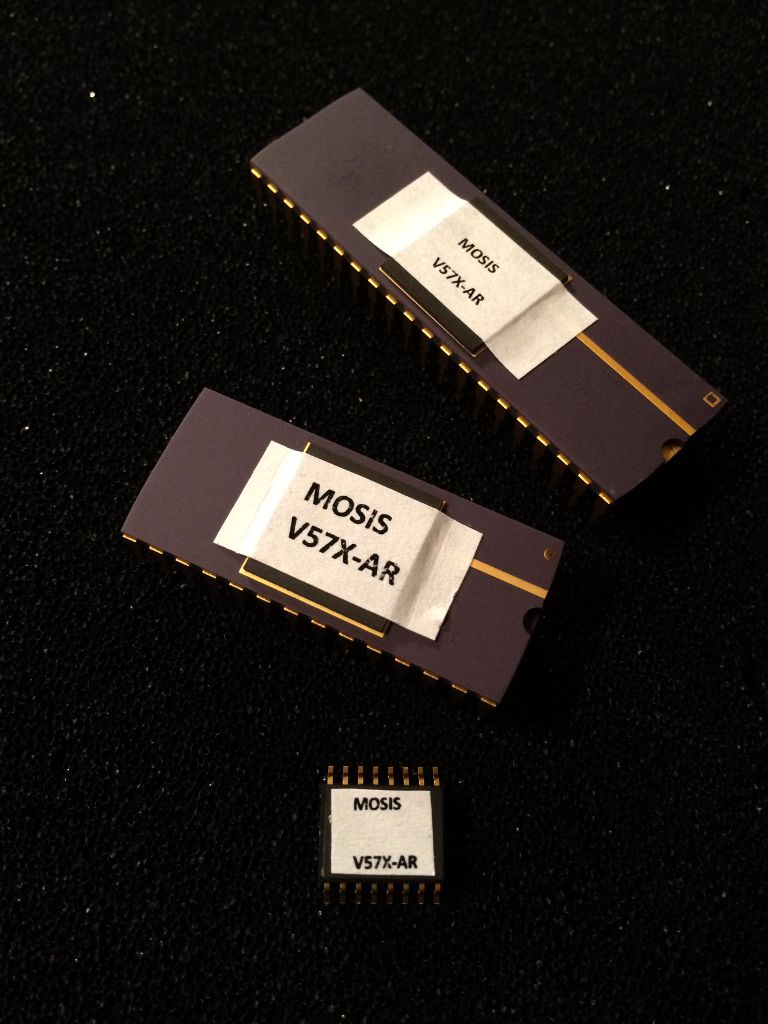

У мосиса будет 40 микросхем по цене чуть больше восьми штук убитых енотов ( кстати только что посмотрел - у них DIP28, а не 24 - надо ещё 4 ноги пририсовать : )

P.S. Четыре N.C. (Not Connected) т.к. я планирую делить чип с кем-то ещё и TERNARO займёт только половину кристалла с 48 выводными площадками, т.е. мне перепадут только 24 площадки... P.P.S. Тогда в 2015 я начал с DIP24 т.к. был в процессе подписания бумаг с европейской конторой типа мосиса - у них несколько дешевле и как раз DIP24 был самым дешёвым вариантом. Но с той конторой не срослось (выбранный ими австрийский заводик меня послал), а у мосиса самые дешёвые упаковки это DIP28 и DIP16, а DIP24 нету вовсе... P.P.P.S. Похоже цены на 0.35um упали - теперь оно чуть ли не в 2 раза дешевле, чем 0.5um |

|||||||||||||||||||||||||||||||||||||||||||||

| 28 Jul 2018 18:24 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Типа вот

|

|||||||||||||||||||||||||||||||||||||||||||||

| 28 Jul 2018 21:59 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

|

|||||||||||||||||||||||||||||||||||||||||||||

| 29 Jul 2018 13:42 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Ну масс-продакшин будет в пластмассе (хотя наверное таки оно в этом случае станет DIP24) |

|||||||||||||||||||||||||||||||||||||||||||||

| 29 Jul 2018 14:00 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

А если всё пропечётся, то также появится возможность подцепить несколько микросхем в цепочку и программировать их разом одной последовательностью битиков |

|||||||||||||||||||||||||||||||||||||||||||||

| 29 Jul 2018 18:55 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Придумал как соединять разные "партишины" внутри большой микросхемы - чтобы несколько полосок шириной 7 логических блоков могли соединяться друг с другом:

Подразумевается, что треугольнички на картинке - это управляемые троичные буферы для "усиления" сигналов между партишинами (либо полного отключения цепей друг от друга) - лишний управляющий битик (номер 0 снизу) можно скажем вместо цепляния к средней как на картинке точке (Vref), сделать битиком для превращения троичных буферов в двоичные (из NOP в NNP) если микросхема используется в режиме двоичного FPGA. Чтобы получить 1000 логических блоков в одной микросхеме, имея "партишины" высотой в 73 канала, потребуется 1000/(73*7) = 1.95 "партишинов" - округляем до 2 - будет 1022 логических блока на две партиции. Четыре соответственно дадут 2044 логических блока, а шесть - 3066 (дальнейшее увеличение количества "партишинов" скорее всего бессмысленно, т.к. они используют по сути одни и теже горизонтальные каналы и в какой-то момент все линии этих каналов просто будут заняты). P.S. Более того, можно сделать так, чтобы "партишены" программировались независимо друг от друга! Скажем путём добавления стольких сигналов разрешения программирования _PRG, сколько есть партишинов (межпартиционные соединения будут программироваться скажем если оба сигнала разрешения в нуле). Если у нас будет корпус PLCC84 в котором 73 ноги это IO, ещё 3 это Vneg, Vpos и Vref, т.е. остаётся 8 ног: /SCK /SDI /SDO /RES /PRG1 (for 1, 2, and 4-partition chip) /PRG2 (for 2 and 4-partition chip) /PRG3 (for 4-partition chip only) /PRG4 (for 4-partition chip only) Тестирование в таком случае будет по последовательному интерфейсу, когда все /PRG в "1" - загоняем в SDI десять бит тестового адреса и далее вытягиваем 2 или 4 троичных значения из SDO - по одному на каждый "партишин". P.P.S. По поводу названий таких микросхем: TRI00773S73 - TERNARO на 7 блоков в канале, 73 канала, slim-design с шириной окна 7 и смещением 3 (511 логических блоков) TRI00773S73X2 - TERNARO как описано выше, но с двумя "партишинами" (1022 логических блока) TRI00773S73X4 - TERNARO как описано выше, но с четырьмя "партишинами" (2044 логических блока) Если будет отбраковка, то можно запрещать "убитые" партишины, перемаркировав микросхему - TRI00773S73/1 если живая только первая "партишин", TRI00883S73/3 если только третья и т.д. P.P.P.S. Кстати скорее всего для производства таких больших микросхем придётся уходить на техпроцесс 0.35um с питанием 3.3V - получается нейтральная точка (Vref) в этом случае будет 1.65V... |

|||||||||||||||||||||||||||||||||||||||||||||

| 01 Aug 2018 23:31 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Интересный момент у меня в голове только что проявился - в одной партишине может сидеть виртуальный троичный софт-компьютер (тот же TRIADOR), который будет иметь возможность программировать вторую партишин той же самой микросхемы! Взрыв мозга - буффф...

P.S. На движке Circuits.CC начал делать сайт для поиграться c TERNARO: http://ternaro.com

Исходный текст этой веб-странички (всё остальное написано на JS и ROBBY):

|

|||||||||||||||||||||||||||||||||||||||||||||

| 02 Aug 2018 00:44 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Посчитал размеры по площадям моих компонентов - полноценная "не-Slim" версия TERNARO на 9 входов в 4 кв.мм НЕ влезает

Влезает только в 11 кв.мм (при технологии 0.5um), производство которых уже зашкаливает за 15 штук... P.S. И это я ещё не посчитал цепочки D-триггеров, которые будут при прошивке использоваться - если ещё и их посчитать, то получается совсем всё страшно Короче выходит, что 63 логических блока + 63 интерконнекта (вместе с сопутствующими цепочками D-триггеров) займут аж 16 кв.мм! Далее каждая дополнительная пара блоков интерконнекта вокруг каждого логического блока (опять же с D-триггерами) потребует 19 кв.мм!! В итоге Slim вариант с 3 интерконнектами в ряд потребует 35 кв.мм, Slim вариант с 7 интерконнектами в ряд потребует 73 кв.мм, а полноценный вариант с 9 интерконнектами в ряд - аж 92 кв.мм - это ж почти сантиметр на сантиметр!!! Если скажем делать только 3-входовой вариант TERNARO, то с 7 колонками (TRI00703) он тоже под 12 кв.мм займёт, а меньше делать бессмысленно... P.P.S. Либо на пробу сделать только 3 входа и 3 колонки в 2x2 мм? Это будет только 9 конфигурируемых логических блоков, 27 блоков интерконнекта и 9*32 + 27*48 = 1584 сдвоенных D-триггеров для прошивки... |

|||||||||||||||||||||||||||||||||||||||||||||

| 05 Aug 2018 01:01 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

С другой стороны можно попробовать сделать упрощённый вариант троичного селектора без просветов между срабатываниями:  Хотя оно уменьшит только площать логических блоков, а блоки интерконнектов останутся такими же т.к. там просто много аналоговых переключателей... |

|||||||||||||||||||||||||||||||||||||||||||||

| 05 Aug 2018 13:28 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Если воспользоватся методикой Xilinx по подсчёту эквивалентных логических гейтов (см. тут), то в случае использования TERNARO как двоичного FPGA (когда каждый троичный мультиплексор превратится в двоичный 2-to-1) каждый логический блок будет равносилен 4*4=16 логическим гейтам! Это значит, что Микросхема TRI00773S73 имея 511 логических блоков будет эквивалентна 8K гейтам Микросхема TRI00773S73X2 имея 1022 логических блоков будет эквивалентна 16К гейтам Микросхема TRI00773S73X4 имея 2044 логических блоков будет эквивалентна 32К гейтам |

|||||||||||||||||||||||||||||||||||||||||||||

| 06 Aug 2018 21:35 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22730 Location: Silicon Valley |

Поддержал отображение всех переключателей:

|

|||||||||||||||||||||||||||||||||||||||||||||

| 10 Aug 2018 01:45 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

Page 4 of 5 |

[ 62 posts ] | Go to page Previous 1, 2, 3, 4, 5 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 1 guest |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |