| Atom Feed | View unanswered posts | View active topics |

It is currently 21 May 2024 11:05 |

|

All times are UTC - 8 hours [ DST ] |

Xavroska-2009 (второе приближение)

Moderator: Shaos

|

|

Page 1 of 1 |

[ 9 posts ] |

| Previous topic | Next topic |

Xavroska-2009 (второе приближение)

| Author | Message | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

Редизайн платы для AVR ATMEGA8515 от Atmel (в PLCC-корпусе) и CPLD XC9572 от Xilinx (тоже в PLCC). Кроме того на плате будет 8К энергонезависимой памяти (SRAM со встроенной батарейкой на 10 лет), последовательный порт (для общения с компьютером), а также некоторые разъёмы (включая порт NI-15), опциональные переключаетели и светодиоды (совмещенные красно-зленые либо обычные, но в два раза больше).

Плату можно будет собрать в двух вариантах: 1) NedoPC-90-B/T - плата для эмуляции троичного компьютера 3niti alpha с панелью управления как вот тут; 2) NedoPC-90-B/X - универсальная плата с AVR, CPLD и кучей I/O. Также возможноы следующие нестандартные сборки: - NedoPC-90-B/XX - универсальная сдвоенная плата (когда квадрат не распилен на треугольные половинки); - NedoPC-90-B/XXX - универсальная строенная плата (когда квадрат не распилен на треугольные половинки и в него сверху воткнута третья треугольная плата); - NedoPC-90-B/ТТ - сдвоенный троичный компьютер; - NedoPC-90-B/ТТТ - строенный троичный компьютер; Возможна сборка 5-вольтовых или 3.3-вольтовых вариантов P.S. Треугольник не получается, так что плата будет называться просто Xavroska-2009 P.S. А троичный компьютер, собранный на её основе (NedoPC-90-B/T) будет называться "3niti alpha simula" Last edited by Shaos on 27 Sep 2009 00:04, edited 4 times in total. |

||||||||||||||||||

| 13 Sep 2009 12:00 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

Последняя версия AVROS (и соответственно система Xavroska 1.0) поддерживает режим NI_15_BUS в случае атмеги-8515 (см. http://www.nedopc.org/forum/viewtopic.php?t=8259 ), когда отдельные сигналы NI-15 не эмулируются (как в NedoPC-90 на атмеге-8535), а подключаются к шине внешней памяти (у которой младшие 8 бит мультиплексированы и имеется сигнал ALE - прямо как в NI-15). Однако мне не совсем нравится способ подключения памяти с точки зрения AVROS в этом режиме - когда A14 идёт на M_IO, а A15 - разрешает/запрещает порт NI15, при этом мы имеем в памяти чередующиеся области M и IO (старшие адреса памяти при этом переключаются отдельными ногами атмеги). С другой стороны у нас пока только 8К памяти и A14/A15 (и A13 кстати тоже) не используются по прямому назначению и могут быть заюзаны в таком варианте.

На самом деле адресный сигнал A13 занимать нельзя, т.к. чтобы увидеть начало 8K памяти нам надо смотреть во вторую копию (распологающуюся в адресном пространстве 0x2000...0x3FFF) - т.е. A13 не будет использоваться вообще! А вот адресные сигналы A14 и A15 могут быть свободны и будут переключать 4 области: 00 - память (M) или внутренние регистры в CPLD (IO); 01 - правый разъём NI-15 master (опциональный ряд контактов для втыкания в бред-боард или другую такую же плату); 10 - левый разъём NI-15 slave (опциональное гнездо для втыкания в него устройств либо другой такой же платы); 11 - центральный разъём NI-15 (который может быть либо гнездом, либо рядом контактов, либо вообще может отсутствовать, если плату не предполагается использовать совместно с шиной NI-15). |

||||||||||||||||||

| 13 Sep 2009 12:14 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

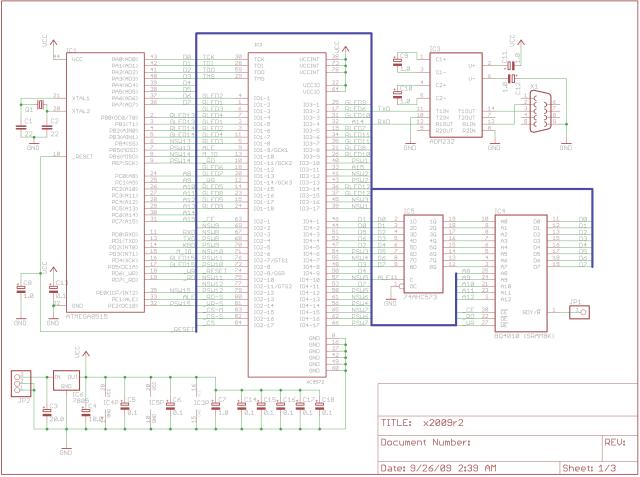

Подключение атмеги-8515:

|

||||||||||||||||||

| 23 Sep 2009 21:40 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

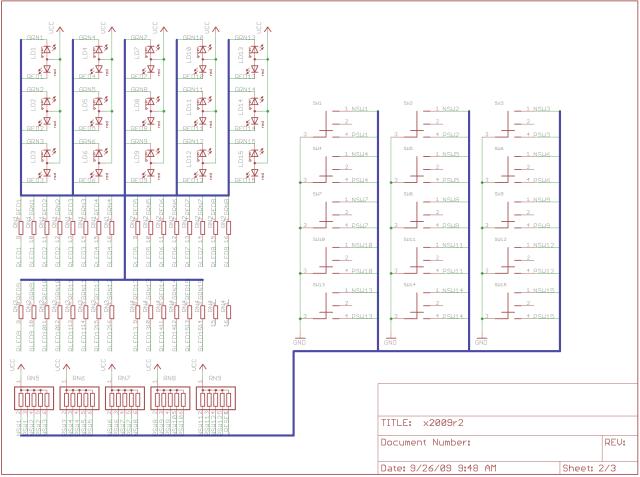

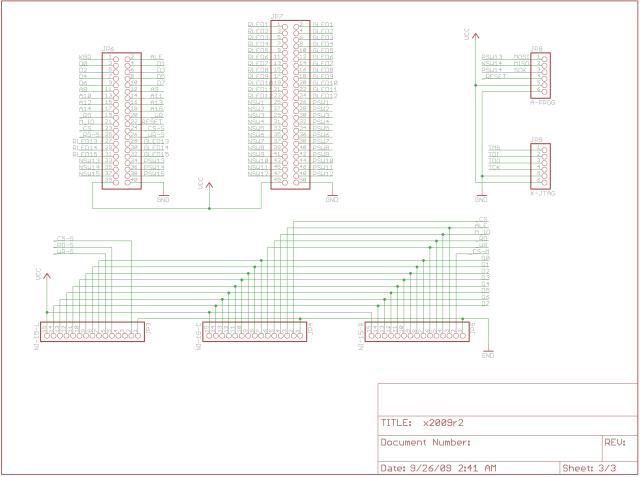

Не хватает ног у CPLD - придётся снаружи ещё регистр-защёлку 74AHC573 ставить между атмегой и памятью (получается что можно вообще без CPLD схему собрать). И левый NI-15 (который Slave) будет не полноценный - он игнорирует внешние сигналы ALE и M_IO (идущие от внешнего мастера), но в-принципе одного байта на ввод и вывод должно быть достаточно для обмена между двумя идентичными платами:

|

||||||||||||||||||

| 24 Sep 2009 18:59 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

|

||||||||||||||||||

| 25 Sep 2009 18:00 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

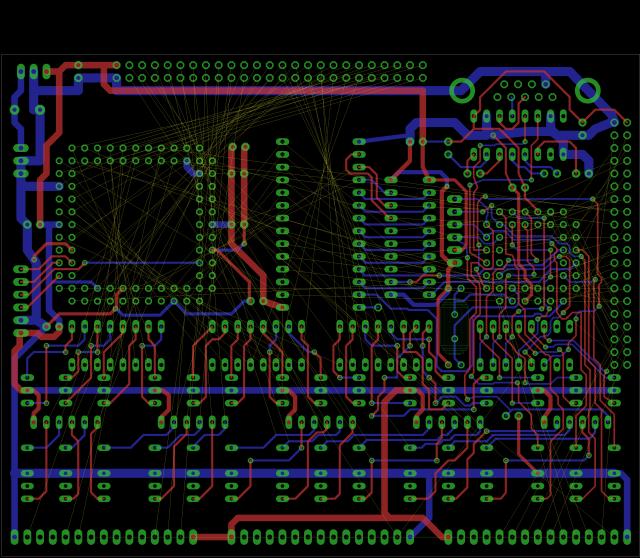

Пытаюсь разводить - мало того что треугольника не получается, так ещё и практически все пределы стандартной версии Eagle заполнил (16 x 10 см)

P.S. Вроде уплотнил до 12.7 x 10 см (будет дешевле изготовить) |

||||||||||||||||||

| 26 Sep 2009 06:37 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

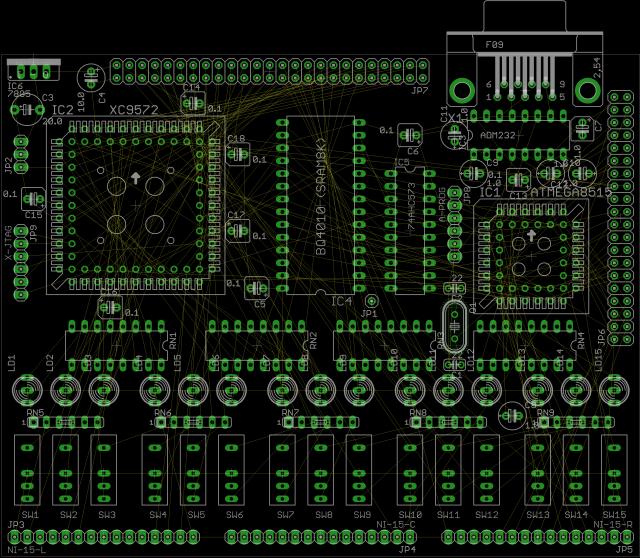

Вот - раскидал компоненты:

Попытаюсь развести в 2 слоя - если серъёзно застряну, то перейду в 4... |

||||||||||||||||||

| 26 Sep 2009 13:27 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

Похоже не разводится - ни в 2 слоя, ни в 4:

Да и дороговато будет такого размера плата в 4 слоя - 2 штуки за $432, 4 - за $492, 10 - за $603, 20 - за $660... Видимо надо упрощать конструкцию |

||||||||||||||||||

| 26 Sep 2009 18:56 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22758 Location: Silicon Valley |

Xavroska-2009 будет передизаёнена позже (без троичных выключателей-светодиодов), а для постройки 3niti alpha simula я решил использовать другой подход - модульный

|

||||||||||||||||||

| 27 Sep 2009 00:04 |

|

||||||||||||||||||

|

|

Page 1 of 1 |

[ 9 posts ] |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 1 guest |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |