| Atom Feed | View unanswered posts | View active topics |

It is currently 14 May 2024 18:47 |

|

All times are UTC - 8 hours [ DST ] |

|

|

Page 1 of 1 |

[ 14 posts ] |

| Previous topic | Next topic |

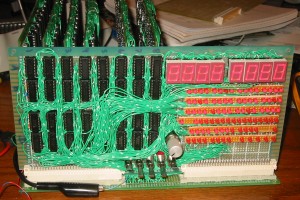

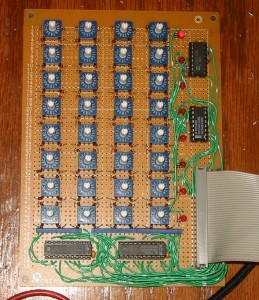

NANDputer

| Author | Message | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

Уже пролетало, однако пусть будет ещё и тут: http://blog.kevtris.org/?m=201303 Фигово конечно что нет ни схем, ни вообще какой-либо документации... P.S. После опубликования на dangerousprototypes было в комментариях:

P.P.S. Про Cray-1 чувак ошибся - он был на NOR построен, а не NAND... Last edited by Shaos on 13 May 2013 16:09, edited 1 time in total. |

||||||||||||||||||

| 09 May 2013 19:16 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

Я кстати иногда тыкаюсь в Logisim и строю всякое на NAND-ах чтобы проверить свои концепции - вчера например строил двухфазные D-триггеры и счётчики

|

||||||||||||||||||

| 09 May 2013 19:39 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

А RAM и ROM он всё-таки заюзал... что несколько неспортивно

с его стороны (ну, с точки зрения нищебродства)

Ещё RAM - куда ни шло... а вот ROM - мог бы и диодной матрицей обойтись... _________________ iLavr Last edited by Lavr on 14 May 2013 05:06, edited 1 time in total. |

||||||||||||||||||

| 13 May 2013 15:06 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

Ну как же - вот у него ROM - на целых 8 слов

|

||||||||||||||||||

| 13 May 2013 16:08 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Это П_О_К_А_З_У_Х_А!  _________________ iLavr |

||||||||||||||||||

| 13 May 2013 16:28 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

да может и 7400 напаяны тоже для показухи, а под пучками проводков спрятан PIC?

чувак же схемы зажилил |

||||||||||||||||||

| 13 May 2013 16:35 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Да... неприятно как-то... как в поговорке:"поманил, да обманул"... Но, впрочем, мы и без него фактически всё знаем. И предъявы мои к ПЗУ - больше ирония. Интересно, конечно же, взглянуть архитектуру, которой он придержался, хотя бы в общих чертах... Потому как сами узлы на NAND для нас тут не секрет, а вот подробности "нищебродской" архитектуры всегда интерес вызывают. _________________ iLavr |

||||||||||||||||||

| 14 May 2013 04:48 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

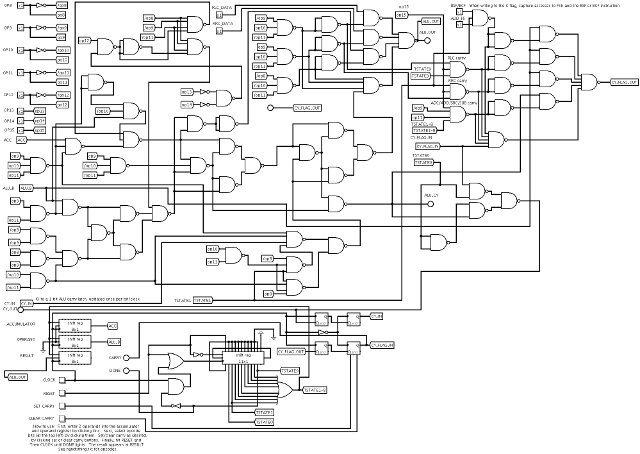

Потыкай его АЛУ на NAND-ах - вот и схемотехникой поинтересуемся... http://blog.kevtris.org/blogfiles/NANDputer/nandalu.circ _________________ iLavr |

||||||||||||||||||

| 14 May 2013 14:16 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

o - а в блоге линков на это нету |

||||||||||||||||||

| 14 May 2013 15:12 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Но мы то с тобой выяснили - где его линки... Но думается мне - большую часть он в Квартусе строил. У него большинство проектов в нем... Картинку выложишь? А то я Логисим уволил... _________________ iLavr |

||||||||||||||||||

| 14 May 2013 15:26 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

А чего уволил? У меня всё ещё есть, хоть я джаву и похоронил уже

Кликабельно. У него кстати тут всякие нанды - не только двухногие. |

||||||||||||||||||

| 14 May 2013 17:49 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Да что-то он ко двору не пришелся... я к другим двум пакетам привык, хоть вы их и не пользуете. За схему - благодарю! А АЛУ-то 1-битное похоже?... 96 тактов у него на инструкцию, кажется? Тут он даже EDUC-8 переплюнул по этому параметру! _________________ iLavr |

||||||||||||||||||

| 14 May 2013 18:09 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22734 Location: Silicon Valley |

Вот у него ещё текстики есть:

http://blog.kevtris.org/blogfiles/NANDp ... inouts.txt http://blog.kevtris.org/blogfiles/NANDp ... timing.txt Содержимое последнего файлика:

|

||||||||||||||||||

| 14 May 2013 19:38 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

А тебе его email нигде не попадался? Этого блогера - http://blog.kevtris.org ? Хочу ему пару вопросов письменно задать... но что-то почты не нашел... Он очень активный на разных сайтах, если, конечно, "kevtris" - это ник одного и того же человека... _________________ iLavr |

||||||||||||||||||

| 17 May 2013 04:23 |

|

||||||||||||||||||

|

|

Page 1 of 1 |

[ 14 posts ] |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 3 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |