| Atom Feed | View unanswered posts | View active topics |

It is currently 29 Apr 2024 08:22 |

|

All times are UTC - 8 hours [ DST ] |

Архитектура процессора 8080

Moderator: Shaos

|

|

Page 3 of 6 |

[ 90 posts ] | Go to page Previous 1, 2, 3, 4, 5, 6 Next |

| Previous topic | Next topic |

Архитектура процессора 8080

| Author | Message | |||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Devil

Joined: 26 May 2003 06:57 Posts: 865 |

Сканировать-то будешь?

|

|||||||||||||||||||||||||||||||||||||||||||||

| 15 Nov 2011 00:47 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22625 Location: Silicon Valley |

всю тыщу страниц? чувак признал свою вину и послал мне правильную книжку, также оставив мне неправильную |

|||||||||||||||||||||||||||||||||||||||||||||

| 15 Nov 2011 07:54 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Retired Joined: 25 Jul 2011 00:14 Posts: 1331 Location: WWW |

занятная книжица. а можно ее обложку сюда выложить? |

|||||||||||||||||||||||||||||||||||||||||||||

| 16 Nov 2011 01:54 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22625 Location: Silicon Valley |

справа "правильная" книжка, которая пришла недавно от этого мужика - там нет таблицы с растактовками, но зато есть блок-схема проца 8080 и все временные диаграммы... Last edited by Shaos on 23 Nov 2011 11:56, edited 1 time in total. |

|||||||||||||||||||||||||||||||||||||||||||||

| 20 Nov 2011 23:57 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

По крайней мере - явно видно, что я не "свистел", когда говорил, что отдельные образцы нашего 580ВМ80 вполне свободно работали на 3.5 МГц... А приборы с военной приёмкой могли потужиться и на 4.... PS. Некогда это погуглить плотно, но, я надеюсь, рефераты списывают с книжек...

Источник Разгон - это ж в значительной мере проблема отвода тепла, нет? |

|||||||||||||||||||||||||||||||||||||||||||||

| 23 Nov 2011 07:29 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

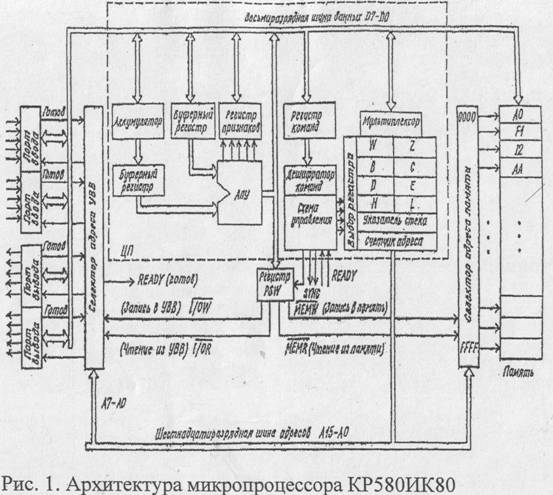

Попалась мне тут ещё одна архитектура нашего любимого процессора,

которая меня очень... очень смутила.

Нет... я конечно понимаю, что всяческие блок-схемы это различные уровни абстракции... Но всё же... |

|||||||||||||||||||||||||||||||||||||||||||||

| 06 Mar 2012 15:05 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Devil

Joined: 26 May 2003 06:57 Posts: 865 |

А что тебя смутило? Всё тут правильно, ЦП обозначен штрихпунктирной линией. Просто на диаграмме ещё и типичный способ использования ЦП обозначен.

|

|||||||||||||||||||||||||||||||||||||||||||||

| 06 Mar 2012 23:43 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Меня смутило - наличие регистра PSW. И способ его взаимодействия с окружением. Ни разу ранее регистр PSW на блок-схемах в таком включении не видел. По крайней мере должны быть ещё буферы адреса и данных, формирующие внешние шины. Должна быть схема управления обменом. Этого всего я не вижу. А вижу из якобы обведённого штриховой линией процессора вылазиют несколько непонятных магистралей, на одной из которых регистр PSW и подвешен. Меня также смутило, что сигналы IORD, IOWR, MEMRD, MEMWR обычно форируются из WR и DBIN процессора с помощью PSW, а совсем не так, как здесь. Меня смутило отсутствие схемы инкремента-декремента, которая обычно присутствует на типичных блок-схемах. Тебя это не смутило? Этого мало? Или это и есть "всё правильно"? PS. Вижу, что b2m такой фигнёй смущаться не привык - для него это "всё правильно"... |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 04:11 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Devil

Joined: 26 May 2003 06:57 Posts: 865 |

Я надеюсь ты не путаешь "регистр признаков" (как он тут обозначен), который в мнемокоде ассемблера обозначается буковками PSW, и слово состояния процессора (дословно processor status word), которое выдаётся в первом такте цикла схемой управления на шину данных. Кстати, единственное, чего нехватает - толстой стрелочки от "схемы управления" на шину данных.

Схемы усиления сигналов можно не относить к архитектуре. Ясно, что так или иначе они будут присутствовать.

Она есть. Так и называется - "схема управления".

Регистр PSW (не путать с регистром признаков), подвешен на шину данных и сохраняет слово состояния процессора (фактически - тип цикла) при выдаче SYNC.

Именно так, как здесь, и формируются. WR и DBIN лишь дублируют нормальные сигналы, которые обычно запоминает системный контроллер в первом такте цикла, и роль которого тут выполняет обычный регистр, названный "регистр PSW". Цель сигналов WR и DBIN - арбитраж шины данных в течении цикла. И невозможно отличить ввод/вывод в порт от чтения/записи памяти только лишь с помощью WR и DBIN. |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 04:59 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Я ничего не путаю. И не надо меня здесь путать множеством букв.

1. На рисунке явно не только "Архитектура микропроцессора КР580ИК80". 2. "Схема управления обменом" - это вовсе не "схема управления", которая здесь формирует сигналы управления внутренними блокам процессора. "Схема управления обменом" - формирует WR и DBIN и направление передачи буфера магистрали данных. "Схема управления" на рисунке WR и DBIN не формирует, их просто нет и сама эта схема - устройство управления и синхронизации. 3. "Схемы усиления сигналов можно не относить к архитектуре. Ясно, что так или иначе они будут присутствовать." - это твоё личное мнение, что не есть истина. Из каких соображений это "ясно" человеку, изучающему процессор по этому рисунку? Буферы магистралей определяют направление передачи и третье состояние. 4. "WR и DBIN лишь дублируют нормальные сигналы, которые обычно запоминает системный контроллер в такте М1" - ничего они не дублируют. Без "нормальных сигналов , которые обычно запоминает системный контроллер в такте М1" процессор полностью работоспособен. А вот интересно, что будет делать системный контроллер без WR и DBIN? Вот схема формирования IORD, IOWR, MEMRD, MEMWR:

Очевидно, что "нормальные сигналы" только определяют куда направить WR и DBIN: к памяти, УВВ или контроллеру прерываний. 5. И чтобы мне не перечислять, чего ещё не хватает на приведённой выше структурной схеме - вот блок-схема из справочника Шахнова:

или вот блок-схема вполне адекватная:

Подводем итог: структурная схема или блок-схема должна помочь разобраться с работой сложной системы без излишней детализации. Но если структурная схема не отражает то, что действительно важно и присутствует в устройстве, и запутывает читателя, то я не могу признать, что в ней "всё правильно". Мне-то уже поздно путаться... но то, что на рисунке называют PSW, обычно принято называть Status - чтобы никто не путался. Last edited by Lavr on 07 Mar 2012 07:27, edited 1 time in total. |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 05:41 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

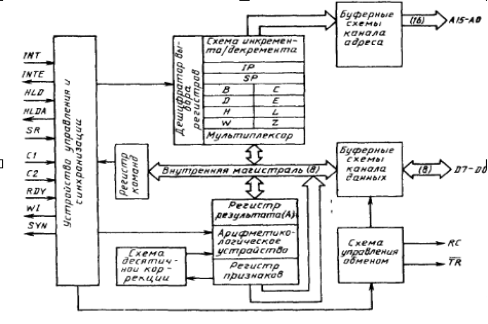

Кстати говоря, похожая блок-схема и то более верно отражает структуру К580ВМ80:

Но на ней забыли, что УУС управляет и всеми внутренними блоками проца. А вот с внешними сигналами - всё верно. Но по мелочам и здесь есть к чему придраться! Можно и просто не обращать внимания... большинству из нас все эти блок-схемы просто "фиолетовы"... Но по ним кто-то учится, их тащут из реферата в реферат, бездумно копируя из Интернета. Вот это меня и удручает... PS. И раз уж мы об этом заговорили, скажу, что и диаграмма машинного цикла К580ВМ80 в разных источниках заметно отличается. Не скажу, что кардинально, но отличия есть. Что тоже удивительно! |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 06:24 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Devil

Joined: 26 May 2003 06:57 Posts: 865 |

Ааа.. Ну если с такой позиции, то вопросов больше не имею. |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 07:12 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Я вобще удивился, почему они у тебя возникли... ну если на схеме чего-то нет, то этого и нет! А если на заборе написано, что это вовсе не забор? Тоже поверить? Дьявол кроется в деталях, мелочах и оттенках. (The devil is in the detail.) И для сравнения приведу блок-схему от Intel, которую Хардыч не зря назвал "самой правильной":

Попробуй, придерись к ней хотя бы в мелочах, раз уж ты такой юморной и умный. |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 07:26 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Devil

Joined: 26 May 2003 06:57 Posts: 865 |

Да пожалуйста! Вот из какого блока этой диаграммы попадает на шину данных слово состояния процессора (то, в котором зашифрованы сигналы MEMR,MEMW, и т.д., а не флаги SZAcPC) в первом такте цикла (одновременно с сигналом SYNC)? |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 08:12 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Ну так сам и ответы давай! Я когда придираюсь - всегда ссылаюсь на правильный вариант! А "от пуза" с криком:"Да пожалуйста!" - это всяк критиковать может... что ты обычно и делаешь. Приведи ссылку, где твоё замечание верно и полно отражено. |

|||||||||||||||||||||||||||||||||||||||||||||

| 07 Mar 2012 08:18 |

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

Page 3 of 6 |

[ 90 posts ] | Go to page Previous 1, 2, 3, 4, 5, 6 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 30 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |