| Atom Feed | View unanswered posts | View active topics |

It is currently 22 Apr 2024 23:36 |

|

All times are UTC - 8 hours [ DST ] |

|

|

Page 2 of 11 |

[ 160 posts ] | Go to page Previous 1, 2, 3, 4, 5 ... 11 Next |

| Previous topic | Next topic |

КМ1801ВМ2

| Author | Message | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22564 Location: Silicon Valley |

"МПИ-интерфейс" это Q-bus |

|||||||||||||||||||||||||||

| 27 Nov 2012 06:07 |

|

|||||||||||||||||||||||||||

|

Fanat

Joined: 27 May 2011 04:25 Posts: 79 Location: Perm |

На вики упоминается про 1Мб модули. Попытка поиска картинок привела к http://www.compsy.de/moduls/dmodul3.htm. Там есть фотки с кучей-кучей микросхем... Это к тому что 512 байтные рамины с родным для subj интерфейсом - как-то это печально все;) (КР573РУ11 - 256x16, К1809РУ1 - 1Kx16). Их лучше оставить для восстановления какого старого железа, а если и мутить новодел самодельный, то на DDR (...и ПЛИС, ага)... шутка))) на SRAM, EDO или cache, как минимум. |

|||||||||||||||||||||||||||

| 27 Nov 2012 08:50 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

я вот лично и хочу только ориганальные микросхемы. плисины для меня хуже ругательства.

меня устроит полностью настоящий килобайт 1809ру1. больше и не надо. зато никаких богомерзких плис пик и авр |

|||||||||||||||||||||||||||

| 27 Nov 2012 11:39 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Мне кажется такие же планарные, твердотельные... в некотором роде по отношению к 18хх - родня! В смысле - далёкие потомки... _________________ iLavr |

|||||||||||||||||||||||||||

| 27 Nov 2012 16:55 |

|

|||||||||||||||||||||||||||

|

Fanat

Joined: 27 May 2011 04:25 Posts: 79 Location: Perm |

Насчет плис шутка была... точнее насчет DDR;) По поводу оригинального набора... Для организации шины достаточно соединить двадцать один проводок от проца до микросхемы памяти... и до второй... и до третей... и так до 128-ой. Без всяких дешифраторов. В чем тут фан? Это слишком легко. И будет работать(при исправных микросхемах). Соединить subj с обычными 8-и битными КР573РУ (т.е. SRAM) или К565РУ5/РУ7 (-> EDO) - задачка повеселее. Если только решать ее самостоятельно, а не подглядывать в схемы от УКНЦ/ДВК/БК-0010/0011. А вот сочинить эмулятор К1801РР1, состоящий из ATMEGA8A и двух буферов 74HCT373, умещающийся на платке размером с сам ROM - вот это я понимаю, доказать себе что-то, так доказать! ;) |

|||||||||||||||||||||||||||

| 28 Nov 2012 05:13 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

А смысл что то доказывать? Да и для кого?

Судя по мануалу без доп дешифраторов можно соеденить только 32 1809РУ1 Но нужно понять как соеденить. А ведь еще надо 1801РР1 7-сегментные индикаторы и клавиатуру на 16 кнопок присоеденить. Может для знающего это легко Но я не знаю и пытаюсь разобраться и понять как это сделать |

|||||||||||||||||||||||||||

| 28 Nov 2012 06:34 |

|

|||||||||||||||||||||||||||

|

Fanat

Joined: 27 May 2011 04:25 Posts: 79 Location: Perm |

1801РР1 также подключается. Ее адрес задается при программировании. Причем если сами данные в микросхеме можно стереть, то биты адреса запрограммированные - в начальное состояние уже не вернуть.

У КР537РУ11 - 7 конфигурационных бит адреса, у 1809РУ1 - 5 бит. Если бы бит было больше, можно было до 794 микросхем подрубить конфигурируемых. Про перефирию - это да. Сродни подключению обычно памяти. Хотя наверняка есть ведь периферийные контроллеры. Да одназаначна. Почему не хочешь их использовать? |

|||||||||||||||||||||||||||

| 28 Nov 2012 08:49 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

судя по глючности РУ1 придется заказать их коробочку. Дорогие правда.

Выбор элементной базы в том что советские и керамика. тех ИС что не существует в керамике придется использовать пластик. Думаю со всем этим разберусь потихоньку. по поводу переферийный ИС врят ли есть что то для 7 сегментного индикатора и 16 кнопочной клавы. а если лепить из 180ВП1 что есть то выходит таже самая МС1201.хх |

|||||||||||||||||||||||||||

| 28 Nov 2012 11:43 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

тут изучая список прошивок 1801ВП1 обнаружил интересные варианты

контроллеры ЗУ ЦМД. похоже сами микросхемки добываемы Интересно схемка сложна будет или нет |

|||||||||||||||||||||||||||

| 28 Nov 2012 12:55 |

|

|||||||||||||||||||||||||||

|

Fanat

Joined: 27 May 2011 04:25 Posts: 79 Location: Perm |

Понятно. Для тебя в данном проекте также важен результат на выходе - некий артобъект. А кого-то интересуют задачки из серии как бы так это по новому все соединить, как никто еще не соединял! ))) |

|||||||||||||||||||||||||||

| 29 Nov 2012 03:43 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

ну раритет не нужен Не собираюсь востанавливать ДВК или УКНЦ. А вот примитивную машинку на оригинальных деталях собрать не против.

|

|||||||||||||||||||||||||||

| 30 Nov 2012 14:11 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22564 Location: Silicon Valley |

Вот они - ебейские приобретения - 2 ВМ1 и 2 ВМ2:

|

|||||||||||||||||||||||||||

| 11 Dec 2012 22:04 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

я вот сегодня получил посылочку с 1801ВМ2 и 1809РУ1 а так же кучку секций 1804ВС1 и ВС2 а таже же другие микросхемы МПК 1804

|

|||||||||||||||||||||||||||

| 12 Dec 2012 01:30 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22564 Location: Silicon Valley |

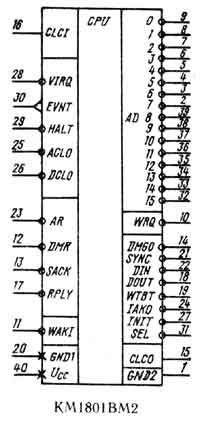

Стандартное отображение процессора на схемах:

Наименование большинства сигналов дословно повторяет сигналы Q-bus из PDP-11 (который LSI-11): VIRQ - по видимому запрос прерывания (в PDP-11 их несколько с разными приоритетами); EVNT - прерывание от внешнего события (в PDP-11 это прерывание с частотой сети 50 Гц или 60 Гц); HALT - ввод процессора в состояние HALT (запуск специальной программы отладки); ACLO - "AC low" (в LSI-11 этому сигналу соответствует BPOK) - участвует в процессе включения; DCLO - "DC low" (в LSI-11 этому сигналу соответствует BDCOK) - участвует в процессе включения; AR - адрес принят (в LSI-11 нету) - участвует в циклах обмена с шиной (проц не будет выдавать DIN/DOUT пока не получит этот сигнал от периферии); DMR - вход запроса режима DMA от девайса, который потом будет ждать DMGO; SACK - вход подтверждения режима DMA от девайса в ответ на DMGO; RPLY - ответ памяти на DIN или DOUT; WAKI - разрешения обмена с окном (в LSI-11 нету); AD0...AD15 - мультиплексированная шина данных и адреса; WRQ - запрос обмена с окном (в LSI-11 нету); DMGO - выход одобрения DMA от процессора (в ответ на DMR); SYNC - сигнализирует, что на мультиплексированной шине можно взять адрес; DIN - выход управления означающий цикл чтения; DOUT - выход управления означающий цикл записи; WTBT - сигнализирует о записи отдельного байта (кроме того находится в 0 при выдаче адреса); IAKO - выход подтверждения прерывания (в ответ на IRQ); INIT - выход для инициализации периферии; SEL - запрос стартового адреса (в LSI-11 нету); CLCI и CLCO - вход и выход тактирования (в LSI-11 такого нету). P.S. Вот описание всех процессоров 1801: http://vak.ru/doku.php/proj/bk/1801vm-series P.P.S. Ещё интересная инфа про старт ВМ1 и ВМ2:

из которой я делаю вывод, что DCLO и ACLO это тоже самое, что BDCOK и BPOK в LSI-11 (обозначил это чуть выше в описании сигналов). |

|||||||||||||||||||||||||||

| 28 Apr 2013 16:54 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22564 Location: Silicon Valley |

А вот интересно - зачем они в ВМ2 воткнули этот AR? Его небыло в ВМ1 (и вроде как нет в ВМ3). Его небыло в LSI-11 (и соответственно в Q-bus). Более того - его нету и в ГОСТе на МПИ! Тогда НАФИГА этот лишний сигнал подтверждения в процессоре, который как бы реализует именно МПИ (Q-bus)? P.S.

Эта схема НЕ будет работать с ВМ2, т.к. она НЕ реализует сигнал AR (адрес принят), отсутствующий в стандарте МПИ (Q-bus). Возможно и "родные" микросхемы памяти тоже работать не будут, если они под ВМ1 заточены, а не под ВМ2. А вот на PAL/GAL думаю относительно просто будет всю эту логику реализовать... P.P.S. Вот тут: http://www.emuverse.ru/wiki/%D0%9A573%D0%A0%D0%A43 (К573РФ3) есть косвенное подтверждение, что озвученные выше микросхемы памяти не содержат вывода AR:

P.P.P.S. Сигнал AR по видимому можно получить на инверсном выходе RS-триггера, взводимого от SYNC и сбрасываемого по RPLY, также ещё потребуется некоторая логика т.к. SYNC и RPLY могут быть нулевыми одновременно и это значит что схема уже не будет содержать просто проц и несколько просто родных памятей... |

|||||||||||||||||||||||||||

| 29 Apr 2013 00:16 |

|

|||||||||||||||||||||||||||

|

|

Page 2 of 11 |

[ 160 posts ] | Go to page Previous 1, 2, 3, 4, 5 ... 11 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 7 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |