| Atom Feed | View unanswered posts | View active topics |

It is currently 26 Apr 2024 02:02 |

|

All times are UTC - 8 hours [ DST ] |

nedoVGA на рассыпухе

Moderator: Shaos

|

|

Page 2 of 2 |

[ 25 posts ] | Go to page Previous 1, 2 |

| Previous topic | Next topic |

nedoVGA на рассыпухе

| Author | Message | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Last edited by Shaos on 04 Jun 2013 21:28, edited 1 time in total. |

|||||||||||||||||||||||||||

| 02 Jun 2013 22:12 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Вроде подобрал 8-битные DAC-и:

http://www.digikey.com/product-detail/e ... ND/2255151 У них правда диапазон выходных уровней от 3.8 вольт до 5 - как бы сдвинуть это дело к нулю?... |

|||||||||||||||||||||||||||

| 03 Jun 2013 15:14 |

|

|||||||||||||||||||||||||||

|

Senior Joined: 07 Aug 2012 11:11 Posts: 123 Location: Севастополь |

Аналоговый сумматор и вычитатель, нужен второй из них, на инвертирующий (?) вход ОУ подаем 3,8в.

Как вариант "быстро и грязно" - повесить на выход стабилитроны/диоды, ну и подобрать падение напряжения на них. |

|||||||||||||||||||||||||||

| 04 Jun 2013 16:14 |

|

|||||||||||||||||||||||||||

|

Retired Joined: 25 Jul 2011 00:14 Posts: 1331 Location: WWW |

|

|||||||||||||||||||||||||||

| 04 Jun 2013 16:31 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Медленные они говорят да и точность мне нужна А R-2R я поставлю на 16-битные выходы |

|||||||||||||||||||||||||||

| 04 Jun 2013 17:40 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

Ага точно - ОУ можно Только у меня 12 МГц - поди быстрые операционники надо? Типа такого: http://www.analog.com/en/all-operationa ... oduct.html И по выходу с 75 Ом монитора как согласовать? P.S. А - в даташите всё есть |

|||||||||||||||||||||||||||

| 04 Jun 2013 17:48 |

|

|||||||||||||||||||||||||||

|

Retired Joined: 25 Jul 2011 00:14 Posts: 1331 Location: WWW |

|

|||||||||||||||||||||||||||

| 04 Jun 2013 20:38 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

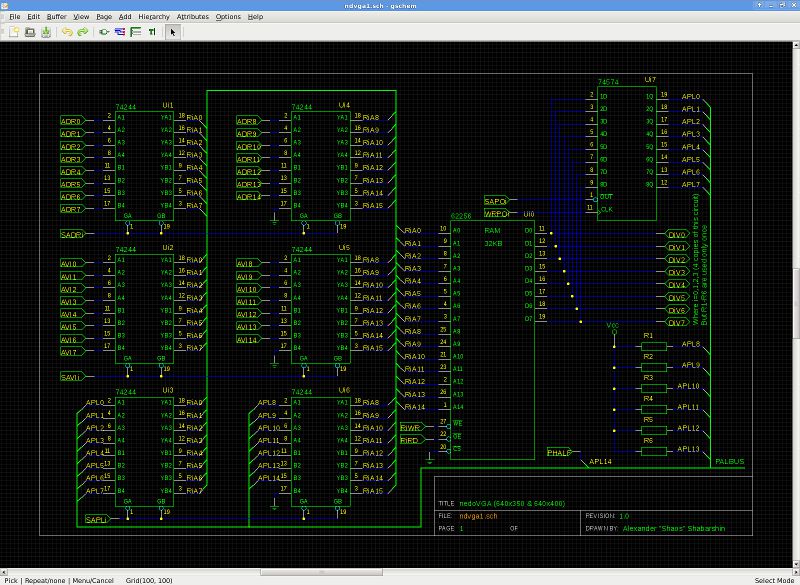

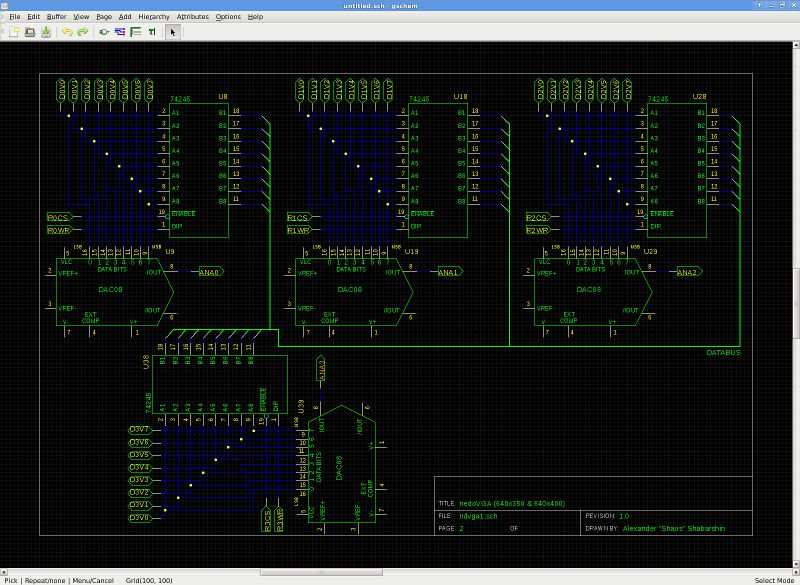

Вот вторая схема, собирающая шины данных всех четырёх каналов и имеющая по одному ЦАП-у и по одному двунаправленному буферу на канал:

ЦАПы пока нарисовал левые - те что были в gschem... Теперь осталось построить схему генерирующую указанные сигналы управления (все сигналы кроме PHALF являются инверсными): - PHALF (0 для первых 4 сегментов экрана и 1 для последних); - SADR0 (подача на адресные входы микросхемы памяти 0 сигналов с шины адреса, при этом SAVI0 и SAPL0 должны быть "1"); - SADR1 (подача на адресные входы микросхемы памяти 1 сигналов с шины адреса, при этом SAVI1 и SAPL1 должны быть "1"); - SADR2 (подача на адресные входы микросхемы памяти 2 сигналов с шины адреса, при этом SAVI2 и SAPL2 должны быть "1"); - SADR3 (подача на адресные входы микросхемы памяти 3 сигналов с шины адреса, при этом SAVI3 и SAPL3 должны быть "1"); - SAVI0 (подача на адресные входы микросхемы памяти 0 сигналов от генератора развёртки, при этом SADR0 и SAPL0 должны быть "1"); - SAVI1 (подача на адресные входы микросхемы памяти 1 сигналов от генератора развёртки, при этом SADR1 и SAPL1 должны быть "1"); - SAVI2 (подача на адресные входы микросхемы памяти 2 сигналов от генератора развёртки, при этом SADR2 и SAPL2 должны быть "1"); - SAVI3 (подача на адресные входы микросхемы памяти 3 сигналов от генератора развёртки, при этом SADR3 и SAPL3 должны быть "1"); - SAPL0 (подача на адресные входы микросхемы памяти 0 сигналов с шины палитры, при этом SADR0 и SAVI0 должны быть "1"); - SAPL1 (подача на адресные входы микросхемы памяти 1 сигналов с шины палитры, при этом SADR1 и SAVI1 должны быть "1"); - SAPL2 (подача на адресные входы микросхемы памяти 2 сигналов с шины палитры, при этом SADR2 и SAVI2 должны быть "1"); - SAPL3 (подача на адресные входы микросхемы памяти 3 сигналов с шины палитры, при этом SADR3 и SAVI3 должны быть "1"); - WRPO0 (запись данных из микросхемы памяти 0 в регистр выбора цвета 0); - WRPO1 (запись данных из микросхемы памяти 1 в регистр выбора цвета 1); - WRPO2 (запись данных из микросхемы памяти 2 в регистр выбора цвета 2); - WRPO3 (запись данных из микросхемы памяти 3 в регистр выбора цвета 3); - SAPO0 (выдача данных из регистра выбора цвета 0 на шину палитры, при этом SAPO1,SAPO2 и SAPO3 должны быть "1"); - SAPO1 (выдача данных из регистра выбора цвета 1 на шину палитры, при этом SAPO0,SAPO2 и SAPO3 должны быть "1"); - SAPO2 (выдача данных из регистра выбора цвета 2 на шину палитры, при этом SAPO0,SAPO1 и SAPO3 должны быть "1"); - SAPO3 (выдача данных из регистра выбора цвета 3 на шину палитры, при этом SAPO0,SAPO1 и SAPO2 должны быть "1"); - R0WR (сигнал записи в микросхему памяти 0); - R1WR (сигнал записи в микросхему памяти 1); - R2WR (сигнал записи в микросхему памяти 2); - R3WR (сигнал записи в микросхему памяти 3); - R0RD (сигнал чтения из микросхемы памяти 0); - R1RD (сигнал чтения из микросхемы памяти 1); - R2RD (сигнал чтения из микросхемы памяти 2); - R3RD (сигнал чтения из микросхемы памяти 3); - R0CS (разрешение двунаправленного буфера, подключающего шину данных к микросхеме памяти 0); - R1CS (разрешение двунаправленного буфера, подключающего шину данных к микросхеме памяти 1); - R2CS (разрешение двунаправленного буфера, подключающего шину данных к микросхеме памяти 2); - R3CS (разрешение двунаправленного буфера, подключающего шину данных к микросхеме памяти 3). P.S. Ставя отдельный ЦАП на каждую микросхему памяти я минимизирую кол-во корпусов, т.к. коммутировать аналоговые сигналы (ANA0, ANA1, ANA2, ANA3) проще, чем мультиплексировать цифровые... P.P.P.S. Смотрю, что если добавить ещё 6 корпусов КП11, то можно легко 16-битный режим RGB565 320x200 поддержать Last edited by Shaos on 05 Jun 2013 06:57, edited 5 times in total. |

|||||||||||||||||||||||||||

| 04 Jun 2013 21:29 |

|

|||||||||||||||||||||||||||

|

Senior Joined: 07 Aug 2012 11:11 Posts: 123 Location: Севастополь |

Быстрые/мощные есть у многих, из известных - у MAXIM-а, например. Сейчас они массово применяются в активных приемниках/передатчиках сигнала по витой паре (видеонаблюдение). |

|||||||||||||||||||||||||||

| 04 Jun 2013 23:40 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

По количеству цветов сдвоенной EGA2VGA палитры расклад такой: - сравнение цветов с точностью до единиц (маска 0xFFFFFF) даёт 1412 цветов; - сравнение цветов с точностью до двоек (маска 0xFEFEFE) даёт 970 цветов; - сравнение цветов с точностью до четвёрок (маска 0xFCFCFC) даёт 796 цветов; - сравнение цветов с точностью до восьмёрок (маска 0xF8F8F8) даёт 615 цветов. Я при генерации палитры использовал маску 0xFEFEFE на которой пожалуй и остановлюсь... P.S. Тот же подход замечательно сработает на ATM Turbo2+ / ZX-Evo Правда там эффективное разрешение будет меньше - 160x200... |

|||||||||||||||||||||||||||

| 17 Jul 2013 00:14 |

|

|||||||||||||||||||||||||||

|

|

Page 2 of 2 |

[ 25 posts ] | Go to page Previous 1, 2 |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 113 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |