| Atom Feed | View unanswered posts | View active topics |

It is currently 23 Apr 2024 13:58 |

|

All times are UTC - 8 hours [ DST ] |

|

|

Page 4 of 6 |

[ 79 posts ] | Go to page Previous 1, 2, 3, 4, 5, 6 Next |

| Previous topic | Next topic |

КР1801ВМ1

| Author | Message | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Devil

Joined: 26 May 2003 06:57 Posts: 860 |

Правильно подглядывали. И система команд на порядок лучше, и шина данных в два раза шире. Вот только не надо было передирать один-в-один. Совмещённая шина адреса/данных убивает нафиг всю производительность. Тут интел оказался молодцом. Надо было сделать проц с той же архитектурой, но с раздельной шиной. Программы работали бы не хуже, а вот производительность поднялась бы на порядок. |

|||||||||||||||||||||||||||

| 29 Aug 2013 00:20 |

|

|||||||||||||||||||||||||||

|

Retired

Joined: 27 Mar 2013 04:55 Posts: 587 Location: 62.192.229.16 |

У Intel 8080 чем то похоже на мультиплекс, по шине данных сначала слово состояния, а потом данные выплевываются. А в 8086 шины данных и адреса уже объединены.

|

|||||||||||||||||||||||||||

| 29 Aug 2013 00:35 |

|

|||||||||||||||||||||||||||

|

Devil

Joined: 26 May 2003 06:57 Posts: 860 |

Но уже в 80286 отказались от этого, что позволило поднять производительность при тех же тактовых частотах. |

|||||||||||||||||||||||||||

| 29 Aug 2013 00:54 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Нет, изюминки в PDP есть!.. Но ввод/вывод у неё мне представляется несколько надуманным и тяжеловатым... _________________ iLavr |

|||||||||||||||||||||||||||

| 29 Aug 2013 03:06 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Да это у них была проблема DIP-40 при разработке 8086... А как перешли на другие корпуса, от "мультиплексии" тут же и отказлись. _________________ iLavr |

|||||||||||||||||||||||||||

| 29 Aug 2013 03:08 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Я вот думаю, что если уж мы взялись драть у Интел - надо было делать сразу лучше Интел... То есть не плодить К580ВМ80, так, что он и сейчас не кончается... А быстрее сделать улучшенный - 580ВМ1... Хотя.. после времени - это лишь ретро-мечты... _________________ iLavr |

|||||||||||||||||||||||||||

| 29 Aug 2013 10:13 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

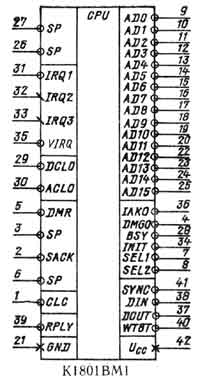

Я подумал, что для процессора 1801ВМ1 тестовую схему с имитацией NOP также адаптировать можно:

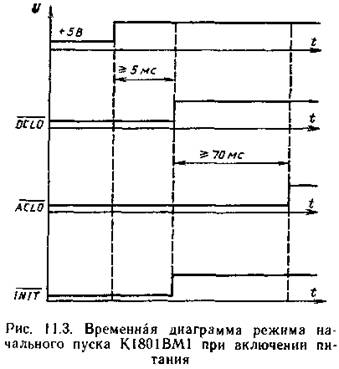

Смотреть Поскольку в верхних адресах у него предполагаются порты, да и в принципе - верхние 8КБайт его адресного пространства отдают под порты, то логично доработать схему тестирования узлом сброса процессора по адресу 0E000H = 1110.0000.0000.0000b на инверсной шине 0001.1111.1111.1111b. То есть, достаточно сделать сброс по трём старшим нулям на шине адреса. После чего тест продолжится с нулевого адреса. Элементы ИЛИ - DD7.3, DD7.4 отслеживают нули в разрядах А13-А15. Инвертор DD1.4 делает этот сигнал активным логической "1". После чего вентиль DD5.4 по этому сигналу при ACLO="1" открытым коллектором разряжает конденсатор С2, чем и осуществляет сброс. В остальном принцип работы схемы такой-же, как описано здесь. Значок "*" на схеме возле названий сигналов означает "буферированный" или "умощненный". Я добавил диод VD2 в цепь сброса, поскольку при подробном рассмотрении оказалось, что последовательность подачи сигналов ACLO и DCLO в схеме из МПСС отличается от приведенной в справочнике. ---------------

ACLO и DCLO должны быть в "0" одновременно, а ACLO - должен перейти в "1" позже DCLO. Несколько также беспокоит разрядка С2 открытым коллектором DD5.4. Но надеюсь, что процесс достаточно кратковремнный, и выходной транзистор DD5.4 не пробьёт. Если будут какие-либо замечания по существу - учту непременно, хотя, согласно имеющимся справочным данным, я и постарался, по возможности, всё предусмотреть. _________________ iLavr |

|||||||||||||||||||||||||||

| 24 Nov 2013 04:25 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Вот эта полоска на процессорах в керамике меня озадачивала всегда... Но, похоже, что с этим вопросом - я разобрался! Спасибо документации!

_________________ iLavr |

|||||||||||||||||||||||||||

| 28 Nov 2013 10:59 |

|

|||||||||||||||||||||||||||

|

Doomed Joined: 05 Apr 2011 12:45 Posts: 491 Location: Великий Новгород |

так же рекомендуется ставить конденсатор между этой перемычкой и общим и в КМ1809РУ1

_________________ танцуй пока живешь под каплями огненного дождя... |

|||||||||||||||||||||||||||

| 30 Nov 2013 15:23 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22567 Location: Silicon Valley |

Вот тут вроде есть 2-процессорный вариант подключения ВМ1 с программируемой логикой: http://zx-pk.ru/threads/21192-eksperimentalnye-protsessornye-moduli-2kh1801vm1-i-1801vm2.html P.S. ВМ2 схемка там тоже есть, правда однопроцессорная... P.P.S. и ВМ3 схемка тоже есть, правда автор указывает на странные глюки у него, решаемые навешиванием конденсаториков на все AD... |

|||||||||||||||||||||||||||

| 12 Jan 2018 20:09 |

|

|||||||||||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22567 Location: Silicon Valley |

Вот детальное техническое описание 1801ВМ1 (причём прошлогоднее) по итогам реверсинжыниринга:

https://github.com/1801BM1/cpu11/raw/master/vm1/doc/1801vm1.pdf Там детально описано поведение многопроцессорной конфигурации и даже примеры кода есть Также задокументированы рудименты от 1801ВЕ1, причём один из таких ранее недокументированных рудиментов - таймер - даже полноценно функционирует в 1801ВМ1Г (и частично функционирует в других буквах - этот таймер даже попал в одно описание БК как фича именно БК) и нога номер 6 (я там чуть выше пытался гадать что оно есть) используется именно для него:

|

|||||||||||||||||||||||||||

| 30 Jun 2019 17:01 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Про таймер в ВМ1 всегда писали, что он есть. Только пользоваться не рекомендовали из-за рудиментарности и недокументированности официально. _________________ iLavr |

|||||||||||||||||||||||||||

| 01 Jul 2019 02:43 |

|

|||||||||||||||||||||||||||

|

Writer

Joined: 03 Jun 2013 11:22 Posts: 19 Location: Минск |

- ВМ1 отличается от ВМ2 и в этой схеме есть некоторые противоречия: 1) если тестирование идёт не всего адресного пространства (а в виде "минус 8К") то до SEL1 и SEL2 попросту не дойдёт (тогда к ним подключены лишние элементы) - а это неправильно, цепочку с *А13*А14*А15 нужно убрать 2) SEL2 через инвертор D3.3 подкл. к выв.2 D5.4, SEL1 не нужно никуда подключать (D3.2 лишнее) 3) на выходе D5.4 поставить небольшой ограничительный резистор, напр. 330 ом - Итог этих изменений - циклический тест до адреса 177716 Last edited by bk-m on 05 Jul 2019 08:52, edited 2 times in total. |

|||||||||||||||||||||||||||

| 05 Jul 2019 07:01 |

|

|||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Вот этот момент не понял, объясните, как SEL1 сбросит на начало теста ? _________________ iLavr |

|||||||||||||||||||||||||||

| 05 Jul 2019 08:14 |

|

|||||||||||||||||||||||||||

|

Writer

Joined: 03 Jun 2013 11:22 Posts: 19 Location: Минск |

отредактировал 2) |

|||||||||||||||||||||||||||

| 05 Jul 2019 08:55 |

|

|||||||||||||||||||||||||||

|

|

Page 4 of 6 |

[ 79 posts ] | Go to page Previous 1, 2, 3, 4, 5, 6 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 17 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |