| Atom Feed | View unanswered posts | View active topics |

It is currently 09 May 2024 15:45 |

|

All times are UTC - 8 hours [ DST ] |

|

|

Page 2 of 2 |

[ 27 posts ] | Go to page Previous 1, 2 |

| Previous topic | Next topic |

Собрал небольшую коллекцию разных Intel 8080 и клонов

| Author | Message | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22703 Location: Silicon Valley |

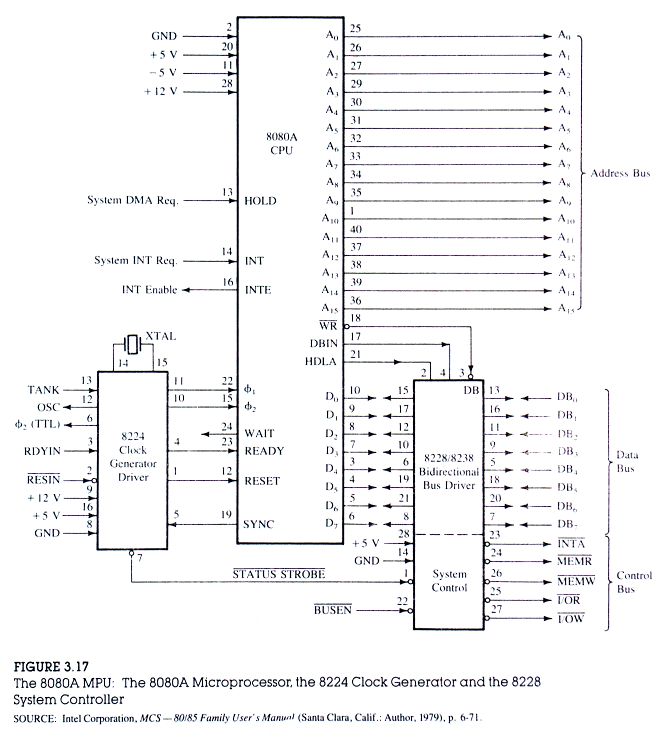

Вот минимальная обвязка из мануала:

Я даже было начал по этой схеме собирать платку накруткой больше года назад, но затормозил из-за нехватки времени...

P.S. Только RAM/ROM всё же надо настоящие поставить... |

||||||||||||||||||||||||||||||||||||

| 26 Dec 2012 21:51 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Мне кажется, если делать - для экспериментов на скорость и т.д. ГФ24 лучше заменить схемой на мелкой логике, как в "Микро-80" или "ЮТ-88". Раз уж мы собрались проверить и влияние питания +12В. Схема и компактная и работоспособная. Я и при моделировании её опять вполне удачно использовал. Кварц - не нужен, раз уж по частоте клока хотим "погулять". Можно просто взять цифровой генератор, если есть в наличии. Стабильности вполне хватит. Да и системный контроллер - для экспериментов как бы излишеством будет, на мой взгляд... Возможно, схема от "ЮТ-88" и будет наиболее подходящей. RDY, INT и HLD - в экспериментах обслуживать вроде как нет нужды - их зацепить на Ucc1 и GND соответственно. _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 26 Dec 2012 22:27 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Интересно, что схемы, подобные "Микро-80" или "ЮТ-88" - это не сугубо

изобретение радиолюбительских журналов. И в более серьёзной литературе они присутствуют...

Из книги: Алексенко А.Г. Проектирование РЭА на микропроцессорах. 1984. Для задающего генератора, кстати говоря, самое главное, чтобы спад С1 не налез на фронт С2. Справочники говорят - минимальное значение этого интервала = 0. Но можно и чуть больше, что и получается в похожих схемах. Вся затея в том, что по спаду С1 информация заносится внутрь МП, а по фронту С2 снимается строб чтения данных. Понятно, что в этот момент данные - "самые установившиеся"... _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 26 Dec 2012 23:06 |

|

||||||||||||||||||||||||||||||||||||

|

Doomed

Joined: 25 Aug 2009 07:02 Posts: 461 Location: Москва |

ГФ24 оставляет промежуток в один свой OSC клок. И в этот же промежуток формирует STSTB. |

||||||||||||||||||||||||||||||||||||

| 27 Dec 2012 14:27 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

А это хорошо или плохо для наших экспериментальных задач? _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 27 Dec 2012 14:33 |

|

||||||||||||||||||||||||||||||||||||

|

Doomed

Joined: 25 Aug 2009 07:02 Posts: 461 Location: Москва |

Экспериментальных? ХЗ. Просто факт. А для эксперимента может имеет смысл регулировку взаимного положения Ф1 и Ф2 замутить? |

||||||||||||||||||||||||||||||||||||

| 28 Dec 2012 07:48 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Не знаю.. с написанием Протеус-модели мне с ними стало всё совершенно ясно... Даже что такое "проблема тактов", про которую Хоровиц-Хилл упоминали, стало вполне прозрачно... Второй такт длиннее - так как в нём и дел больше... А основные привязки - к фронтам/спадам. Так что они не должны перекрываться... _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 28 Dec 2012 11:32 |

|

||||||||||||||||||||||||||||||||||||

|

Banned Joined: 20 Mar 2005 13:41 Posts: 2141 Location: От туда |

Все зависит от того, какие узлы их используют. Если узлы не зависят друг от друга - то почему бы и не перекрыть? |

||||||||||||||||||||||||||||||||||||

| 28 Dec 2012 21:31 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Очередной бред...

Если снять строб чтения данных до занесения информации внутрь МП? Поэтому

PS. Наверное, процессор не для того делают синхронной системой, чтобы основные синхронизирующие моменты времени перекрывались... _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 28 Dec 2012 22:03 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Интересно, что по справочнику Шахнова Микропроцессоры и микропроцессорные комплекты этого никак не скажешь...

Хотя тайминги для этой же К580ГФ24 в нем же изображены, похоже, верно... Хотя не очевидно, что STSTB формируется как "промежуток в один OSC клок"...

Видимо со временем несоответствие осознали, и тот же упрощенный рисунок схемы для К580ГФ24 стал попадаться в более корректном виде...

Но тут уже перестарались... можно было всё же показать, к чему RESIN и RDYIN привязывются по фазе... _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 28 Dec 2012 23:58 |

|

||||||||||||||||||||||||||||||||||||

|

Doomed

Joined: 25 Aug 2009 07:02 Posts: 461 Location: Москва |

Интересно, почему я так тогда сказал. Это же неправда. По клокам начало Ф2 примыкает к концу Ф1. Маленькая пауза там из-за всяких задержек получается. И STSTB тоже не там, как тогда сказал. Да, он в промежутке, но в другом. После Ф2 непосредственно перед Ф1. Если по тактам раскладывать: 1 2 Ф1 3 4 5 6 7 Ф2 8 пусто 9 STSTB Даже при кварце 18 МГц, фазы 2 МГц, все очень хорошо видно, ничего не расползается и не наезжает

И промежуток

|

||||||||||||||||||||||||||||||||||||

| 09 Mar 2021 15:01 |

|

||||||||||||||||||||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Потому как другие люди, хоть и не "зачерпывали пригоршнями на стенд", давно и без особой помпы посмотрели осциллограммы и 580ГФ24, и оригинальной i8224:

Да, это именно так и есть, похоже, что вы лишь сейчас "из мешка горстью" закинули экземпляр на пресловутый "стенд", так как и для аналога задающих генераторов на мелкой логике пауза там всегда есть. http://www.nedopc.org/forum/viewtopic.php?f=90&t=11201&start=15#p135789 Тем более, что один из этих сигналов активен срезом, а другой - фронтом. Некоторым людям, хочется вставить между ними задержку на RC-цепочке, тут остаётся только в недоумении развести руками... Что касается сигнала STSTB, то вполне очевидно, где он должен быть, поскольку его задача зафиксировать STATUS, а данные на шине максимально устойчивы ближе к их снятию. _________________ iLavr |

||||||||||||||||||||||||||||||||||||

| 10 Mar 2021 01:04 |

|

||||||||||||||||||||||||||||||||||||

|

|

Page 2 of 2 |

[ 27 posts ] | Go to page Previous 1, 2 |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: No registered users and 3 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |