Есть идея сделать миниатюрный вариант вроде Sprinter-а. На немного другом процессоре (ARM7TDMI + ПЛИС). Мне нужен Недопись вместо промперсоналок...

Она проста. Ядро - процессор ( с интегрированной периферией обычно, вроде COM, Eth, FPU, MAC ), ОЗУ, флеш-биос, часы, прочая муть, ПЛИС. В ПЛИСке реализованы скоростные последовательные порты ввода-вывода. Точка-точка. Штук 4 - 16. Однотипные. В ПЛИСке же ( в зависимости от сложности ) есть буфера на ввод-вывод, отображаемые на память процессора. Ответная часть, соответственно, должна иметь ответный буфер, контроллер, который поддерживают протокол обмена с стороны ПЛИС и управляющий периферийным устройством с другой. Ядро может изменяться, ответные части тоже. Интерфейс с протоколом обмена остаётся.

Типы интерфейсов:

1) Низкоскоростной. Дешёвый.

Это SPI, синхронный, уровни 5 и 3,3В КМОП.

Пропускная способность до 1 МБайт/сек. ( На сегодня полностью освоен )

2) Среднескоростной. Подороже.

Это LVDS, синхронный.

Пропускная способность до 30 МБайт/сек.( На сегодня опытные образцы )

3) Высокоскоростной. Дорогой.

Это опять LVDS, только запараллелен.( На сегодня только проект )

До 1 гига в теории :)

Разграничение обязанностей между бивисом и осом. Обеспечение платформонезависимости. Например сегодня ARM, а завтра суперпупермотороллер в свете прикладных программ (что б не переписывать). Обеспечение самоконфигурирования и горячего под/отключения.

Горизонты ( радужные ).

1-3 месяца обсуждение и поиск.

2-4 месяца изготовление прототипа.

1-3 месяца оживление и отладка.

Предлагаемая конфигурация прототипа. Ядро ARM AT91Mxxxx, 128К ОЗУ, 1-4М ПЗУ, иквадратные часы, ПЛИС альтера или ксайлинкс. Клавиатура PS/2. ЖКИ ( символьный или графический ). Флеш накопитель самопальный или DiskOnModul с нашим контроллером (как получиться). Звуковой модуль АС-97.

Вот набор тезисов.

Образно говоря РВМ - микромейнфрейм для одного пользователя. С терминалом, файловым сервером, сервером звука, видео и проч...

Процессорное ядро - собственно процессор, дополнительная ОЗУ, загрузочная флеш-память, связной интерфейс. Минимальное ядро может обойтись без дополнительной оперативной памяти если встроенной достаточно, например, если взять AT91M40800 с 8 Кбайт ОЗУ на борту. А можно применить и сверхпопулярный Z80. В современной инкарнации, наподобие eZ80. Главная и единственная задача процессорного ядра - обработка информации. Максимально быстро.

Как устроено ядро. Да просто. Минимум корпусов, минимум связей между ними. Процессор, ОЗУ, Флеш, ПЛИС связи плюс остальное по вкусу.

Процессор и ОЗУ перерабатывают информацию. Во флешке - бивис, который отвечает за начальное конфигурирование ядра и может, немного оси.

ПЛИС-ина организует интерфейс с листьями. Это самое важное место во всей архитектуре - интерфейс! Мы можем менять ядра ,листья, но интерфейс останется. Это да╦т возможность и постепенного апгрейда и независимой разработки железок.

Естественно, и даже прежде всего, этот интерфейс должен быть проработан с точки зрения программиста. Но опираясь на возможности существующего железа. Какие же возможности видны мне? Типы ПЛИС. Это семейства Flex10K ( есть 5В версии ) или Acex ( 3,3В и меньше) у Altera. Spartan у Xilinx. Во всех этих м/с есть внутренняя память. Которую и будем задействовать для связи. Для программера это будет выглядеть как двухпортовка или FIFO плюс регистры управления.

Примерный алгоритм обмена будет выглядеть так: Дожидаемся освобождения ресурса для обмена. Например, если до этого уже что-то кому-то передавали. Пишем в него запрос. Сваливаем по своим делам..... Приходим, интересуемся, как там наш запрос и не отвалился ли лист.... Ответ на запрос пришёл - прекрасно, забираем. Время, отводимое на эту операцию закончилось, а ответа нет или лист отвалился - обрабатываем ошибку.

К сему предлагаю три картинки - ядро, флеш, жки.

Показан набросок для младшей ПЛИСки серии Асекс фирмы Альтера. Процессор по параллельной шине имеет доступ к буферной памяти по 512 байт, в ПЛИСке таких три памяти. Каждая буферная память может подсоединятся к любому незанятому каналу. Процессор может независимо адресоваться к любой буферной памяти.

Для листа попроще. Задача его интерфейса - всегда быть готовым к приему данных от ядра. Поэтому ДВЕ буферные памяти. На случай, если ядро торопиться, а мелкопроцессор вс╦ ещ╦ ковыряется с предыдущим запросом. В качестве диспетчера памяти планируется использовать самую деш╦вую Альтеру (серии MAX3000A) или что то в этом роде. FRAM как буферную память. Она имеет последовательный, достаточно быстрый интерфейс. Доступны м/с с 5МГц и вроде как доступны с 20МГц. Сайт, где можно поинтересоваться что это - www.chipinfo.ru. Ну и мелкоконтроллер для листа скорее всего AVR или MSP430.

Проанализируем работу такого интерфейса.

Процессор ядра.

Начало

Наш╦л свободный ресурс ( буферную память ).

Записал запрос.

Послал, куда надо.

И так пока ресурсы не закончились.

Пошёл покурил, дела поделал. И с начала.

И так курит годами:)

Мелкоконтроллер листа

Начало

Отбрыкавшись от неотложных дел обнаружил запрос.

Поинтересовался, о чём там говориться.

Ответил. Если ещё есть время глянул - может ещё есть,

пообщаться-то охота. А то всё один, да один.

Ушел по неотложным делам к началу.

И так до очередного сброса:)

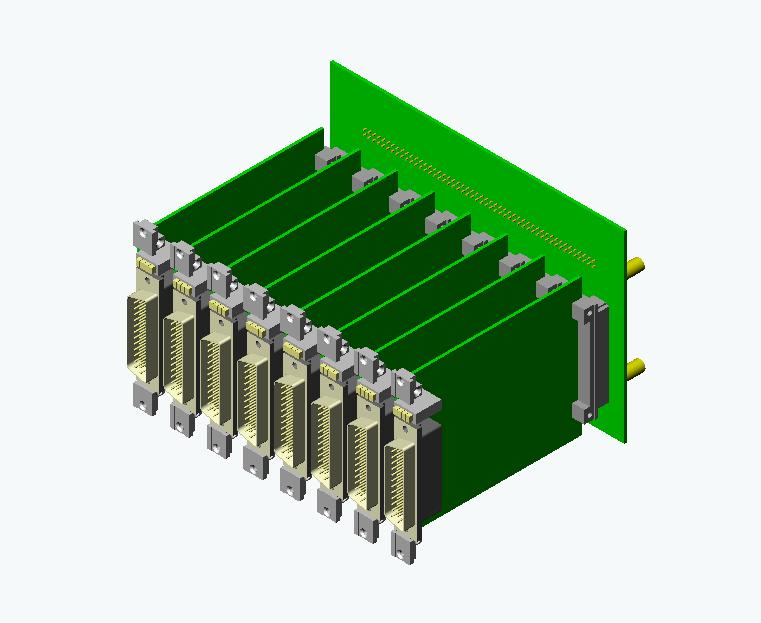

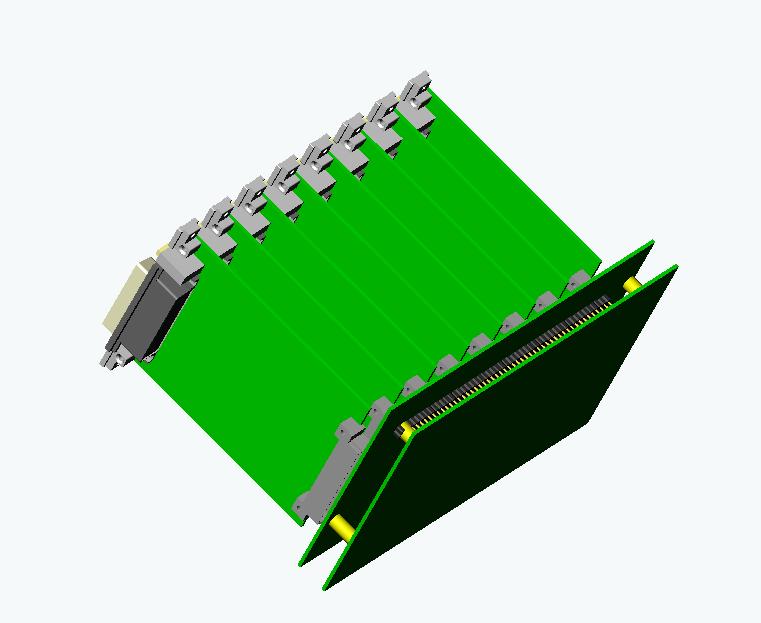

Разработан первый вариант конструктива.

Иллюстрация 1. Вид со стороны периферийных модулей

Иллюстрация 2. Вид со стороны управляющего модуля

Платы с разьёмами – периферийные модули, они крепяться на кросс-плату. С другой стороны на кросс плату крепиться управляющий модуль.

Иллюстрация 3. Вид периферийного модуля

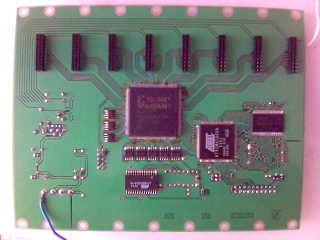

Схемы. Первый вариант УМ. На базе AT91M42800 ( Atmel ).

Иллюстрация 4. Центральный процессор

Схемка мелковата, если кому чего – так выложу покрупнее. Имеем загрузочную память 128Кбайт с 8-ми битной шиной. ОЗУ пока не ставим. Пользуемся внутренним. Используем только одну PLLB. Она самая скоростная. Естественно, часики и на всякий пожарный – DATAFLASH. Сделана одна плата. В настоящий момент идёт оживление конструкции.

Далее по плану:

Изготовление кросс платы и одного периферийного модуля.

Иллюстрация 5. Часы и DATAFLASH

Только 1 плата (УМ) есть. Следуюшее, что будем делать - ПМ(ЖКИ),

ПМ(накопитель),ПМ(связь).

Перед тем как изготавливать необходимо понять, что нужно.

По ПМ(ЖКИ):

Например - графический ч.б. ЖКИ 128х64 точки, пц клава, ps/2 мышь.

Или всё на USB. Может цветной ЖКИ 320х240 точек? Звук АС97 или нет?

Без клавы и без мыши? Может вообще, через писявый терминал работать на первых порах?

По ПМ(накопитель):

Ёмкость какая? Файловая система нужна - кто возьмётся?

По ПМ(связь):

СОМ достаточно?

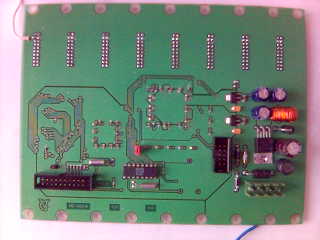

Вот скорбно гляжу на плату УМ. Некому оживить. Сам тоже не успеваю - заказчики навалились, из командировок и писюка не вылазию. Что есть хорошего:

Коммерческий вариант работает как лошадь. До некоммерческого никак не дойду. Хотя очень хочу. Вот фотки (правда с низким разрешением) сделал, пошлю Александру, попрошу вставить в сообщение. Нужны помощники. Программист на ARM и ксилинковец. Интересные факты по коммерческому варианту:

УМ вид со стороны подключения:

УМ вид со стороны БП и часов:

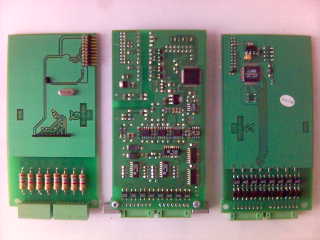

ПМ примеры плат:

Updated by Shaos on November 26, 2014