| Atom Feed | View unanswered posts | View active topics |

It is currently 26 Apr 2024 07:14 |

|

All times are UTC - 8 hours [ DST ] |

Z80 Finite State Machine

Moderator: Shaos

|

|

Page 3 of 9 |

[ 128 posts ] | Go to page Previous 1, 2, 3, 4, 5, 6 ... 9 Next |

| Previous topic | Next topic |

Z80 Finite State Machine

| Author | Message | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Почти готов третий слой, осталось частично АЛУ, регистры и логика, работающая с управляющими выводами процессора (#RD, #WR...). В некоторых местах плохо видно, но может и без них можно обойтись.

Попробовал нарисовать схему подключения регистров к шине данных, вроде получилось. http://yadi.sk/d/-4nYjbYf5Voxa Дальше будет управление регистрами, а потом попробую АЛУ, но там вообще жесть. Или может вас что-то другое в первую очередь интересует? |

||||||||||||||||||

| 04 Jun 2013 13:29 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

А на уровне логических элементов и вентилей это никак не получается? А то ты тратишь время и работу делаешь интересную, но только сколь это полезно кому-либо в виде транзисторов? _________________ iLavr |

||||||||||||||||||

| 04 Jun 2013 14:05 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Пока на уровне логических элементов никак не получается, потому что не понимаю как это работает целиком. Полезно в первую очередь мне самому, в любом виде. Вообще я хотел z80 на макетке запустить и вытащить подробности его работы, в том числе недокументированные, а по ним уже попытаться создать какую-то схему, которая вела себя так же. Но раз попались фотографии кристалла, то почему бы и нет? Вот и рисую транзисторы, потом буду в логику переводить. А чтобы проверить нет ли ошибок в этой логике - буду проверять на реальном процессоре. |

||||||||||||||||||

| 04 Jun 2013 14:41 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Наш Хардыч, помнится, где-то участвовал в аналогичном проекте и они там вроде как приспособились переводить эти транзисторные схемы в логику. Может быть - он подскажет... Мне же попадалось похожее вот в этом американском патенте: US3564226 Pat. Electronic calculator or digital processor chip having multiple function Посмотри его - может поможет... (по ссылке - "Загрузить PDF") Всё же отрисовать 8500 транзисторов - не многовато ли будет? _________________ iLavr |

||||||||||||||||||

| 04 Jun 2013 14:54 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Один разряд: 12 регистров по 4 транзистора на бит плюс 2 на выборку - 72, на чтение-запись ещё 18, итого 90 на разряд. Разрядов 16, 90*16=1440 транзисторов уже "отрисовано" Как транзисторы в логику перевести я в принципе понимаю. Практики не было. |

||||||||||||||||||

| 04 Jun 2013 15:07 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Срисовал всю регистровую часть: регистры, запись-чтение, 16-битный инкремент-декремент, формирование адреса. Ну и другие модули немного. Кое-где есть "зависающие в воздухе" затворы при #CLK=0.

Как вы думаете, почему у регистра R инкрементируются только 7 бит, а старший не меняется? |

||||||||||||||||||

| 07 Jun 2013 14:53 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

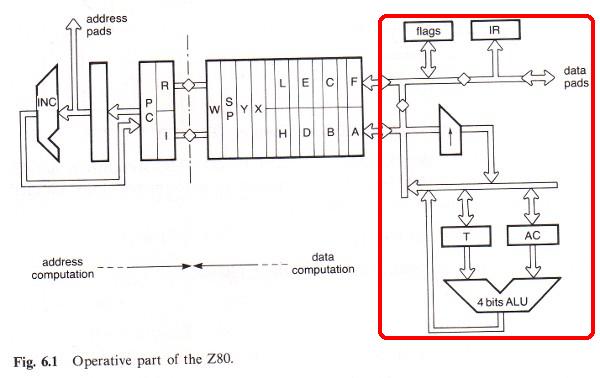

Слушай, мне вот кажется, что АЛУ потрясающих открытий нам не даст, т.к. мы неплохо представляем принцип его работы... А вот весь участок, выделенный на рисунке, ты не мог бы срисовать и объяснить?

Мы так и не поняли назначение вот этого "молотка", и как 8-битный путь данных становится 4-битным и обратно. Где-то же должны быть мультиплексоры, как мне кажется, хотя здесь их вроде как принято называть коммутаторы... _________________ iLavr |

||||||||||||||||||

| 07 Jun 2013 15:19 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Интересный рисунок. Откуда он? Очень похож, по-моему даже порядок регистров совпадает с кристаллом. Мультиплексоров (как я понимаю это слово) у процессора нет, у него действительно коммутаторы, то есть просто транзисторы "в разрыв". И входы-выходы во всей схеме понятие относительное, что для меня очень непривычно. Срисовать придётся всё АЛУ, потому что всё очень плотно расположено и где что я с первого взгляда понять не могу. T и AC по-моему находятся внутри АЛУ, да и тактовый сигнал куда-то в АЛУ заведён вместе с остальными тремя десятками управляющих сигналов. |

||||||||||||||||||

| 07 Jun 2013 15:40 |

|

||||||||||||||||||

|

Supreme God Joined: 21 Oct 2009 08:08 Posts: 7777 Location: Россия |

Собственно, видимо, это пока единственный найденный нами печатный источник, где блок-схему z80 приводят, учитывая 4-битность. Обычно - фальшиво показывают его 8-битным полностью. Но Shaos говорит - особых комментариев с подробностями к этому рисунку в книге нет. _________________ iLavr |

||||||||||||||||||

| 07 Jun 2013 15:52 |

|

||||||||||||||||||

|

Admin Joined: 08 Jan 2003 23:22 Posts: 22587 Location: Silicon Valley |

|

||||||||||||||||||

| 07 Jun 2013 15:55 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Головы не хватает всё удерживать, я уже стал за собой замечать что и читаю через строчку, особенно когда чем-то занят... чем-то вроде срисовывания схемы микропроцессора Завтра начну с шины данных и пойду в сторону АЛУ. Тем более что уже пора замеченное упорядочить в виде блок-схемы, самому же проще будет. |

||||||||||||||||||

| 07 Jun 2013 16:06 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

О микрокоде (там обсуждалось http://www.nedopc.org/forum/viewtopic.php?t=7790 )

- instruction register - декодер примерно на 100 выходов, распознающий команды и группы команд - блок многовходовых ИЛИ-НЕ (штук 50), на них заведены выходы декодера - штук 80 элементов И-ИЛИ-НЕ, ИЛИ-И-НЕ, которые в основном обрабатывают сигналы с 11 линий, идущих из управляющего блока (halt, wait, busrq и т.п.), - выходы этих элементов идут на АЛУ, блок регистров, и прочее управление Если микрокодом считать регулярную структуру логических элементов, которая что-то декодирует и выдаёт управляющие сигналы, то там таких структур, если не придираться к регулярности, аж три штуки. |

||||||||||||||||||

| 07 Jun 2013 16:38 |

|

||||||||||||||||||

|

Doomed

Joined: 25 Aug 2009 07:02 Posts: 460 Location: Москва |

Тот, который адрес регенерируемой строки держит? А что тут думать, DRAM того времени не более 128 усилителей строк имели. |

||||||||||||||||||

| 08 Jun 2013 03:03 |

|

||||||||||||||||||

|

Senior

Joined: 20 Mar 2013 03:36 Posts: 137 Location: Ростов-на-Дону |

Да? А я о другом подумал. У схемы inc/dec чёткая структура, I и R хранятся как 16-битное значение, а блокировку переноса было очень удобно сделать именно в этом разряде, потому что на нём как раз схема ускоренного переноса. Или наоборот, ускоренный перенос сделали в этом разряде, чтобы блокировку добавить? Или просто так совпало? Не покидает ощущение, что при проектировании было две основных проблемы "куда впихнуть желаемое" и "чего б такого добавить в оставшееся место" |

||||||||||||||||||

| 08 Jun 2013 03:18 |

|

||||||||||||||||||

|

Doomed

Joined: 25 Aug 2009 07:02 Posts: 460 Location: Москва |

Неверно, 128 строк регенерации, усилители это CAS. RAS это выбор ячейки в плече усилителя, по 64 в плече стало быть. |

||||||||||||||||||

| 08 Jun 2013 04:46 |

|

||||||||||||||||||

|

|

Page 3 of 9 |

[ 128 posts ] | Go to page Previous 1, 2, 3, 4, 5, 6 ... 9 Next |

|

All times are UTC - 8 hours [ DST ] |

Who is online |

Users browsing this forum: Bing [Bot] and 37 guests |

| You cannot post new topics in this forum You cannot reply to topics in this forum You cannot edit your posts in this forum You cannot delete your posts in this forum You cannot post attachments in this forum |