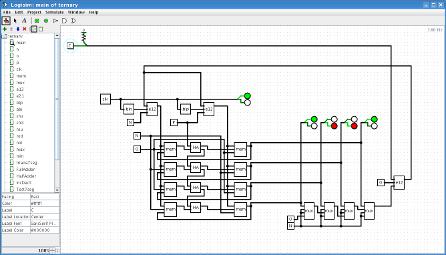

About circ-format - it is relatively easy one, because wires described as separate lines and it looks like Logisim constructs circuits from them on load. We even don't need to specify width of every wire (as 1-wire or 2-wire or more in one line) - it's just wire (but we need to specify width of every pin). Logisim builds network in moment of showing of schematics. That's cool!

What I don't like - there are bunch of lines in circ-files describing loaded libraries and some settings - so it looks like unrelated garbage for me. For example in 75 lines of simplest scheme (1 input pin directly connected to 1 output pin) only these 9 lines (12%) actually describe schematics:

Code: Select all

<wire from="(130,170)" to="(200,170)"/>

<comp lib="0" loc="(130,170)" name="Pin">

<a name="tristate" val="false"/>

</comp>

<comp lib="0" loc="(200,170)" name="Pin">

<a name="facing" val="west"/>

<a name="output" val="true"/>

<a name="labelloc" val="east"/>

</comp>

Code: Select all

<a name="width" val="2"/>

Also path to custom libraries is sometimes saved as relative, but sometimes as absolute - it is bad and inconsistent...