Слушай, какие участливые... - не хотят потерять потенциального клиента!Shaos wrote: потом через пару дней написали, что продолжают исследование вопроса...

Разработка и заказ троичной микросхемы

Moderator: haqreu

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Разработка и заказ троичной микросхемы

iLavr

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Прислали чертержи аж ТРЁХ разных корпусов DIP48Lavr wrote:Слушай, какие участливые... - не хотят потерять потенциального клиента!Shaos wrote: потом через пару дней написали, что продолжают исследование вопроса...

С углублением со стороной .310 дюймов (8мм), .350 дюймов (9мм) и .400 дюймов (10мм)

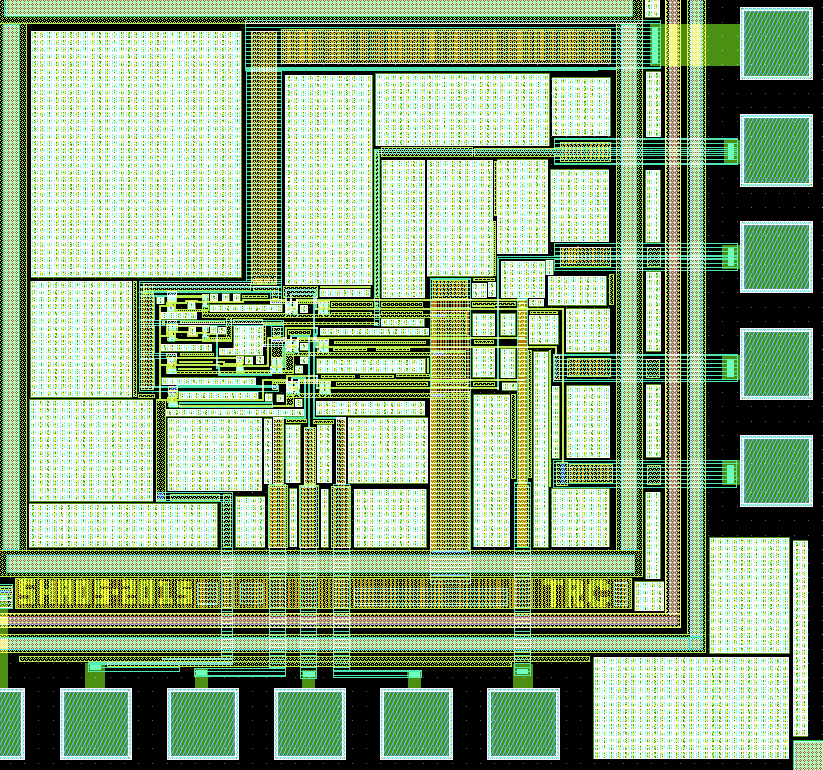

У меня, как я и говорил, будет кремниевый кристалл 2x2мм (на самом деле мосис делает кристалл чуть больше, где ставит каёмочку и заголовочек, куда вписывает номер партии)

P.S. Интересно, что по идентификационным номерам запросов в суппорт можно прикинуть сколько их у них вообще бывало - с июня по ноябрь 2015 номера увеличились на 1200 единиц (240 в месяц), а с ноября 2015 по декабрь 2017 - на 8100 (330 в месяц)...

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

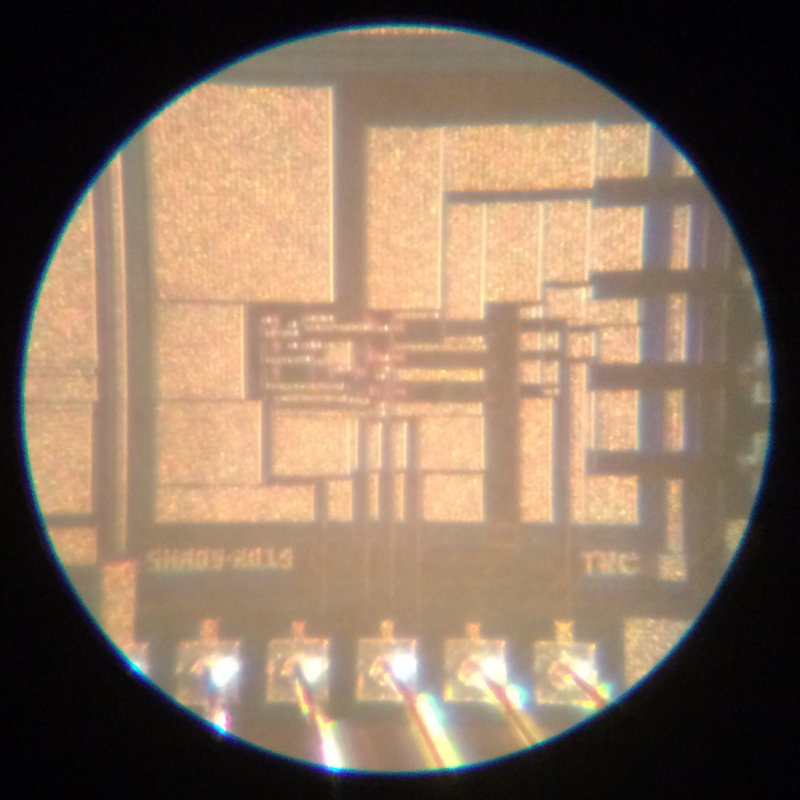

Временно отобрал у дочек детский микроскоп с USB-камерой и сфоткал свой угол с троичным мультиплексором в двух разрешениях - максимальном:Shaos wrote:Надо чтоли планировать второй заходShaos wrote:

P.S. На последней фотке правый-нижний угол кристалла, где расположен мой троичный мультиплексор, составленный из двоичных NAND/NOR (которые будут "Public Domain"):

Только в этот раз надо в чип что-то более полезное затолкать - например TRIADOR и NEDONAND

и минимальном:

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Не существует пока "троичных транзисторов" - всё строю на обычных двоичных CMOS, составляющих в том числе аналоговые ключи, которые собственно и переключают троичные сигналы

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Посчитал, что в кристалл 2x2мм влезет порядка 500 троичных мультиплексоров (каждый занимает площадку 77x60um), а чтобы воткнуть 1000 MUX-ов, размер кристалла надо увеличить до 2.7x2.7мм, что будет на 65% дороже выпустить (для первых 40 чипов), зато туда можно будет больше ног воткнуть и запаковать скажем в PLCC68 (заюзав все 68 ног)

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Как мы выяснили вот тут триадор таки влезет в текущие ограничения чипа 2x2мм и даже ещё место останется (под тот же NEDONAND например и другие тестовые схемы) - значит план такой - ко 2 апреля заталкиваем TRIADOR в TRIASIC, добавляем в оставшееся пространство NEDONAND (с другими тестовыми схемами) и сдаём в производство с запаковкой скажем 3 микросхем в DIP48 - при дальнейшем успешном тестировании можно доупаковать оставшиеся кристаллы в DIP28 либо для триадора, либо для недонанда (т.е. как бы 2 разные микросхемы получатся)

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

чото все запасы денег испарилисьShaos wrote:Вобщем пока ориентируюсь на 2 апреля 2018 года:

https://www.mosis.com/db/pubf/fsched?ORG=ON-SEMI

2 апреля отменяется...

-

Paguo-86PK

- Maniac

- Posts: 267

- Joined: 12 Apr 2011 20:43

- Location: Tashkent

Re: Разработка и заказ троичной микросхемы

Вышe писалось, что одна заказная микросхема обходится всего в $100, однако, минимальный заказ - 100 штук. Или я ошибся.

Меня заинтересовало следующее: Под заказные микросхемы портят одну болванку кремния и не так важно, сколько на ней будет отдельных схем. То есть, если разместить на ней 5 чипов, то каждый чип будет стоит $2000? Или я совсем запутался?

Вот потому хочу спросить: А на одной болванке размещается паттерн одной схемы? Или можно разработать 20 разных микросхем и разместить их на одной болванке комплектом?

Т.е. 5 сумматоров, 5 дешифраторов, 5 АЦП, 5 ЦАП и т.д. Чтобы всяко-разно покрывало всю поверхность болванки?

К чему это я… Просто хотел бы в перспективе оплатить пару собственных кристаллов для индивидуальных целей, чтобы отдельно не заказывать.

Меня заинтересовало следующее: Под заказные микросхемы портят одну болванку кремния и не так важно, сколько на ней будет отдельных схем. То есть, если разместить на ней 5 чипов, то каждый чип будет стоит $2000? Или я совсем запутался?

Вот потому хочу спросить: А на одной болванке размещается паттерн одной схемы? Или можно разработать 20 разных микросхем и разместить их на одной болванке комплектом?

Т.е. 5 сумматоров, 5 дешифраторов, 5 АЦП, 5 ЦАП и т.д. Чтобы всяко-разно покрывало всю поверхность болванки?

К чему это я… Просто хотел бы в перспективе оплатить пару собственных кристаллов для индивидуальных целей, чтобы отдельно не заказывать.

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Они разные заказы на одной и той же кремниевой пластине размещают - минимум порядка десяти штук бабосов получается за один заказ (если все сорок кристалов паковать)

P.S. Я предлагал объединяться опен-сорцным кремнеделателям чтобы на одном кристалле до 4 дизайнов размещать (в разных углах кристалла и с независимым питанием), которые можно по разному запаковать в корпуса (чтобы только "свои" ноги видеть)

P.S. Я предлагал объединяться опен-сорцным кремнеделателям чтобы на одном кристалле до 4 дизайнов размещать (в разных углах кристалла и с независимым питанием), которые можно по разному запаковать в корпуса (чтобы только "свои" ноги видеть)

-

Paguo-86PK

- Maniac

- Posts: 267

- Joined: 12 Apr 2011 20:43

- Location: Tashkent

Разработка и заказ микросхемы-оборотня

Конечнo, многие будут смеяться… Но, хотел вот разработать микросхему-хамелеон.

Суть работы такой микросхемы относительно проста.

Если корпус DIP14, то один пин - аналоговый вход к АЦП. Установкой около корпуса такой микросхемы маленького подстроечного резистора, можно его регулированием «настроить» внутренную логику чипа:

Если рассматривать последнюю четвёртую внизу схему, то она имеет весь набор элементов: DD1 - NAND, DD2 - NOR, DD3 - OR, DD4 - XOR. Тем самым, если взять селектор-мультиплексор и подключить его к выходам этих четырёх элементов, будем иметь готовые четыре функции.

Если достаточно хорошо продумать, можно реализовать все перечисленные восемь функций с минимальными затратами.

А с помощью АЦП просто управлять селекцией мультиплексирования.

Распиновка очень строгая: 1-АЦП, 2-вход триггера шмитта, 3-выход НЕ триггера шмитта, 4/5-X1/Y1, 6-Q1, 8-Q2, 9/10-Y2/X2, 11-Q3, 12/13-Y3/X3.

P.S.: Понимаю, практическая реализация идеальных цифровых узлов на таких «хамелеонах» будет не достаточно стабильной и вся логика будет нарушаться от любой помехи в цепях питания. Но, чисто ради эксперимента - любопытно очень…

Суть работы такой микросхемы относительно проста.

Если корпус DIP14, то один пин - аналоговый вход к АЦП. Установкой около корпуса такой микросхемы маленького подстроечного резистора, можно его регулированием «настроить» внутренную логику чипа:

- 0.5…0.9V - три элемента AND

- 1.0…1.4V - три элемента NAND

- 1.5…1.9V - три элемента OR

- 2.0…2.4V - три элемента NOR

- 2.5…2.9V - три элемента XOR

- 3.0…3.4V - три буферных повторителя с Z-состоянием

- 3.5…3.9V - три RS-триггера

- 4.0…4.4V - три D-триггера

Если рассматривать последнюю четвёртую внизу схему, то она имеет весь набор элементов: DD1 - NAND, DD2 - NOR, DD3 - OR, DD4 - XOR. Тем самым, если взять селектор-мультиплексор и подключить его к выходам этих четырёх элементов, будем иметь готовые четыре функции.

Если достаточно хорошо продумать, можно реализовать все перечисленные восемь функций с минимальными затратами.

А с помощью АЦП просто управлять селекцией мультиплексирования.

Распиновка очень строгая: 1-АЦП, 2-вход триггера шмитта, 3-выход НЕ триггера шмитта, 4/5-X1/Y1, 6-Q1, 8-Q2, 9/10-Y2/X2, 11-Q3, 12/13-Y3/X3.

P.S.: Понимаю, практическая реализация идеальных цифровых узлов на таких «хамелеонах» будет не достаточно стабильной и вся логика будет нарушаться от любой помехи в цепях питания. Но, чисто ради эксперимента - любопытно очень…

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Порогов сильно много - я делал максимум 4-уровневый детектор - уже размеры транзисторов в плечах инвертора отличались в разы...

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Следующие времена заходов:Shaos wrote:чото все запасы денег испарилисьShaos wrote:Вобщем пока ориентируюсь на 2 апреля 2018 года:

https://www.mosis.com/db/pubf/fsched?ORG=ON-SEMI

2 апреля отменяется...

- создание проекта до 23 июля (уже просрочено), окончательная сдача проекта - 6 августа 2018 (примерная дата готовности - 4 февраля 2019)

- создание проекта до 19 ноября, окончательная сдача проекта - 3 декабря 2018 (примерная дата готовности - 3 июня 2019)

Пока ориентируюсь на 3 декабря

P.S. Как видно по вышеуказанной ссылке, после лета мосис оставляет на ON Semiconductor только 0.5um процесс (C5F/C5N), убирая все остальные, но что-то мне сдаётся они и 0.5 вскорости могут прикрыть, так что надо успевать (а потом останется делать 0.35um на других заводах)

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re:

За прошедшие 3 года автор Паралеллы серъёзно поднялся в должности и всякой фигнёй больше не занимается (я с ним в 2015 кстати по е-мейлу успел пообщаться):Shaos wrote:Вот интересная статья автора, показавшего на личном примере как можно стать успешной "fabless semicondactor company" истратив "всего" 2 миллиона:

http://www.adapteva.com/white-papers/a- ... tup-model/

You do not have the required permissions to view the files attached to this post.

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re:

Чото там остался только ON Semi со своими 0.5um - пожалуй скопирую сюда, пока не прибили окончательно:Shaos wrote:Проблема с ними в том, что они поддерживают только коммерческие программы разработки, а вот MOSIS, как оказалось, поддерживает ещё и опенсорцные Magic и Electric:Shaos wrote:Ответили следующее - надо сначала подписывать соглашение о неразглашении через официально зарегистрированную компанию (которая у меня есть), затем они дадут библиотеки под один из коммерческих продуктов подготовки GDSII-файлов, но проверку присланного им GDSII они будут делать только в Mentor/Calibre. Получившийся GDSII я не имею права публиковать, но могу публиковать (например у себя на сайте) фотку кристалла и картинку топологии микросхемы. Также могу публиковать инфу о площади кристалла, быстродействии, частоте, потребляемой мощности, но не могу делать публичной инфу о проверочных правилах дизайна (DRC) или электрических параметрах процесса выбранного завода по производству кремниевых вафель...Shaos wrote: P.P.S. Написал французам письмецо с вопросами - посмотрим что ответят

https://www.mosis.com/pages/design/flow ... scmos-kits

Code: Select all

Foundry Comparable Process1 Technology Code Layer Map

ON Semi 0.50 micron,1P3M,C5 SCN3M,SCN3M_SUBM See SCN3M map

ON Semi 0.50 micron,2P3M,C5 SCN3ME,SCN3ME_SUBM See SCN3ME map

Code: Select all

Layer GDS CIF CIF-Synonym Rule-Section Notes

N_WELL 42 CWN 1

ACTIVE 43 CAA 2

POLY 46 CPG 3

N_PLUS_SELECT 45 CSN 4

P_PLUS_SELECT 44 CSP 4

CONTACT 25 CCC CCG 5, 6, 13

POLY_CONTACT 47 CCP 5 Can be replaced by CONTACT

ACTIVE_CONTACT 48 CCA 6 Can be replaced by CONTACT

METAL1 49 CM1 CMF 7

VIA 50 CV1 CVA 8

METAL2 51 CM2 CMS 9

VIA2 61 CV2 CVS 14

METAL3 62 CM3 CMT 15

GLASS 52 COG 10

PADS 26 XP Non-fab layer used to highlight pads

Comments -- CX Comments

-

Shaos

- Admin

- Posts: 25058

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Декабрь я благополучно профукал, как и следующую дату - 1 апреля 2019Shaos wrote:Следующие времена заходов:Shaos wrote:чото все запасы денег испарились

2 апреля отменяется...

- создание проекта до 23 июля (уже просрочено), окончательная сдача проекта - 6 августа 2018 (примерная дата готовности - 4 февраля 2019)

- создание проекта до 19 ноября, окончательная сдача проекта - 3 декабря 2018 (примерная дата готовности - 3 июня 2019)

Пока ориентируюсь на 3 декабря

P.S. Как видно по вышеуказанной ссылке, после лета мосис оставляет на ON Semiconductor только 0.5um процесс (C5F/C5N), убирая все остальные, но что-то мне сдаётся они и 0.5 вскорости могут прикрыть, так что надо успевать (а потом останется делать 0.35um на других заводах)

Теперь в соответствии с https://www.mosis.com/db/pubf/fsched?ORG=ON-SEMI есть ещё один шанс - 22 июля этого года!

Проект и всея бумажная возня должны быть закончены до 8 июля 2019 года, сдача на завод 22 июля 2019 года и примерная доставка микросхем - 20 января 2020 года