Возможные микроархитектуры для 3niti alpha/beta

Moderator: haqreu

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Возможные микроархитектуры для 3niti alpha/beta

Озадачился я тут реальной реализацией системы команд 3niti и понял, что это задача далеко нетривиальная - пытаюсь утолкать всё в 3 такта на короткую 1-триадную инструкцию (и соответственно 6 тактов на 2-триадную и 12 тактов на 4-триадную). Спасает то, что тактируется оно синусоидой, которая превращается в троичный сигнал NOPONOPO... и мы можем срабатывать как на P, так и на N - т.е. частота срабатывания в два раза больше частоты синусоиды (т.е. в 3 периода синусоиды можно утолкать 6 разных срабатываний конечного автомата).

Выдумалась микроархитектура, где добавляются несколько скрытых регистров:

I - старшая триада расширенной инструкции (используется для отработки многотриадных команд);

T0 - временный регистр для сохранения инструкции вычитанной из памяти;

T1 - временный регистр для сохранения младшей триады 9-тритового слова из памяти;

T2 - временный регистр для сохранения средней триады 9-тритового слова из памяти;

T3 - временный регистр для сохранения старшей триады 9-тритового слова из памяти;

TP - 9-тритовый псевдорегистр, составленный из T1,T2,T3.

P.S. На самом деле основная задача понять, влезает ли полноценная реализация 3niti alpha в ограничение на 1000 троичных мультиплексоров

Выдумалась микроархитектура, где добавляются несколько скрытых регистров:

I - старшая триада расширенной инструкции (используется для отработки многотриадных команд);

T0 - временный регистр для сохранения инструкции вычитанной из памяти;

T1 - временный регистр для сохранения младшей триады 9-тритового слова из памяти;

T2 - временный регистр для сохранения средней триады 9-тритового слова из памяти;

T3 - временный регистр для сохранения старшей триады 9-тритового слова из памяти;

TP - 9-тритовый псевдорегистр, составленный из T1,T2,T3.

P.S. На самом деле основная задача понять, влезает ли полноценная реализация 3niti alpha в ограничение на 1000 троичных мультиплексоров

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Микроархитектура 3niti alpha

Вот только не совсем понятно, почему "тактируется оно синусоидой"...Shaos wrote:Спасает то, что тактируется оно синусоидой, которая превращается в троичный сигнал NOPONOPO... и мы можем срабатывать как на P, так и на N - т.е. частота срабатывания в два раза больше частоты синусоиды (т.е. в 3 периода синусоиды можно утолкать 6 разных срабатываний конечного автомата).

Идеология конечного автомата в устройстве управления и синхронизации

заключается, если я не ошибаюсь, в том, что по тактовым импульсам счетчик

состояний перебирает все возможные состояния в пределах одного цикла.

А троичный счетчик, как мы выяснили, работает вовсе не по "синусоиде", а

скорее уж по "пиле"...

Lavr wrote:И я вот тут сделал прикидку, как считает троичный счетчик:

Lavr wrote:А второй глобальный вывод - логические троичные генераторы должны формировать

троичные импульсные последовательности, пропуская через вентиль несимметричную

пилу...

iLavr

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

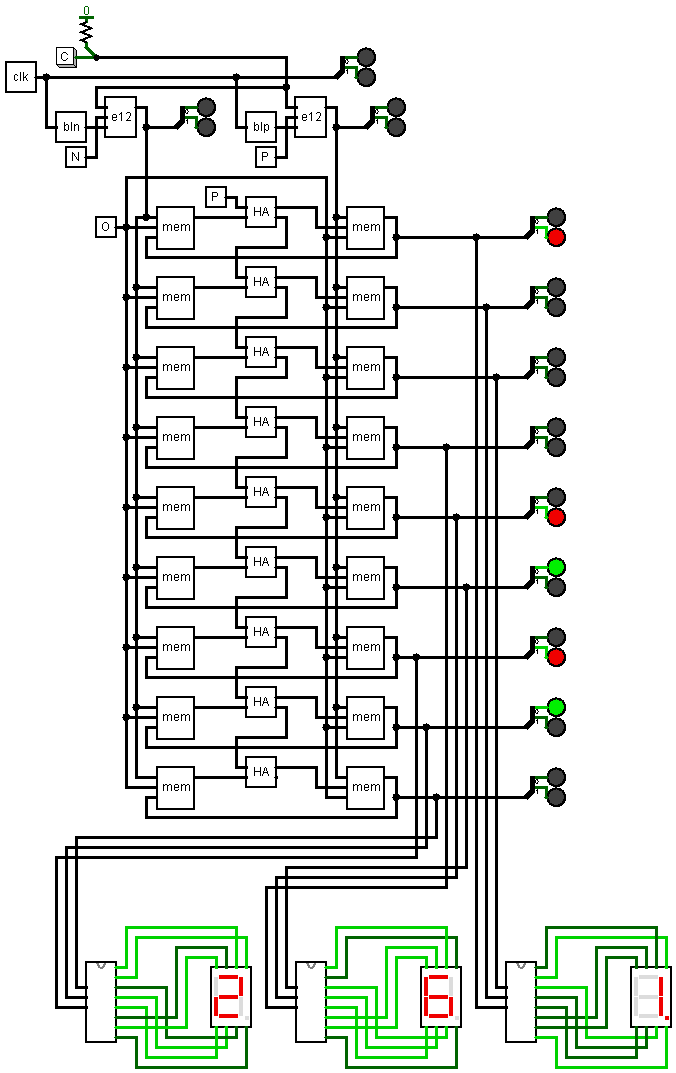

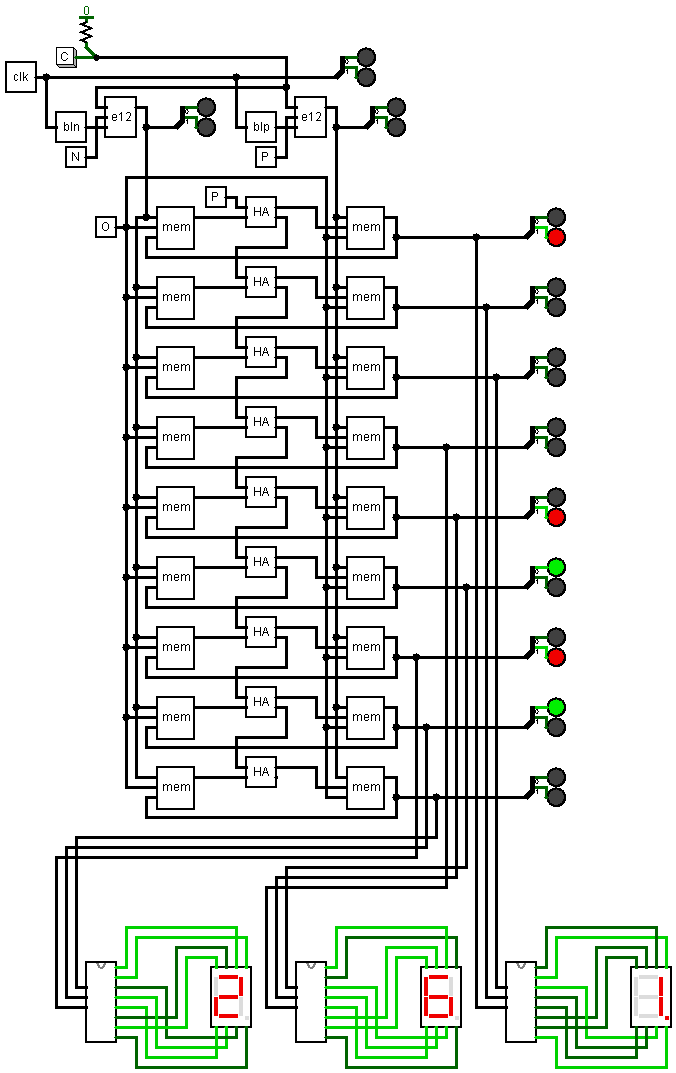

Ну у кого как, а у меня синхронный троичный счётчик управляется синусоидой

Левые мемы срабатывают по положительному импульсу, а правые - по отрицательному, а кнопка C сбрасывает всё в ноль

P.S. Возможно пилой он тоже сможет управляться, но мне как-то спокойнее от того, что нулевая пауза есть не только между негативным и позитивным импульсами, но и между позитивным и негативным...

Левые мемы срабатывают по положительному импульсу, а правые - по отрицательному, а кнопка C сбрасывает всё в ноль

P.S. Возможно пилой он тоже сможет управляться, но мне как-то спокойнее от того, что нулевая пауза есть не только между негативным и позитивным импульсами, но и между позитивным и негативным...

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Микроархитектура 3niti alpha

Тогда это не счетчик, потому как непонятно что считает.Shaos wrote:Ну у кого как, а у меня счётчик управляется синусоидой

А картинка

http://ternary.info/ternary/ternary_sec ... 9trits.png

почему-то не видна...

iLavr

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

ну он увеличивает число на 1 за каждый период входящей синусоидыLavr wrote:Тогда это не счетчик, потому как непонятно что считает.Shaos wrote:Ну у кого как, а у меня счётчик управляется синусоидой

проверил в опере - вроде видно

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Микроархитектура 3niti alpha

Забавно... только я никак не пойму, вроде разговор про "3niti alpha",Shaos wrote:ну он увеличивает число на 1 за каждый период входящей синусоидыLavr wrote:Тогда это не счетчик, потому как непонятно что считает.Shaos wrote:Ну у кого как, а у меня счётчик управляется синусоидой

а троичный счетчик почему-то считает "период входящей синусоиды"?...

PS. Я хоть и не вижу по-прежнему картинки, но догадываюсь, что ты показываешь.

Обсуждали, помнится...

РPS. Ладно... я больше ничего тут не комментирую, а то еще обидишься...

iLavr

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

не вижу никаких противоречий

P.S. вон наш 8080 тоже вполне себе двоичный проц, однако управляется он какими-то странными последовательностями Ф1 и Ф2, а никак не единственным двоичным синхросигналом с 50% скважностью...

P.S. вон наш 8080 тоже вполне себе двоичный проц, однако управляется он какими-то странными последовательностями Ф1 и Ф2, а никак не единственным двоичным синхросигналом с 50% скважностью...

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

Считает оно вот так:

Клок проходит через все каскады и не обязан быть троичным - все же остальные каскады считают вполне себе троично, причём синхронно

P.S. По сути это уже и есть PC - надо только прикрутить к нему схемку изменения его значения по командам JMP или LPCD

Code: Select all

_ _ _ _ _ _

CLK _| |_ _| |_ _| |_ _| |_ _| |_ _| |_ _...

|_| |_| |_| |_| |_| |_|

_______ _______

T0 _____| | _______| | ___...

|_______| |_______|

_______________________

T1 _____________| |

|___________...

___________...

T2 _____________________________________|

P.S. По сути это уже и есть PC - надо только прикрутить к нему схемку изменения его значения по командам JMP или LPCD

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Микроархитектура 3niti alpha

Дерёёёёвня...Shaos wrote:вон наш 8080 тоже вполне себе двоичный проц, однако управляется он какими-то странными последовательностями Ф1 и Ф2, а никак не единственным двоичным синхросигналом с 50% скважностью...

Почитал хотя бы пару книг из нашей библиотеки, прежде чем так позориться!

Надо же! Пол-века еще не прошло, а Ф1 и Ф2 вдруг стали "какими-то странными последовательностями"!

Ну не синусоидами все же они стали? А, Shaos? Ну надо же такое ляпануть!

Не... тут правда больше не следует ничего комментировать... всё откровенно ясно...

iLavr

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

Ну у меня тоже двухфазная синхронизация, только одним проводом

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

Короче PC будет начинаться со второго каскада, а первый просто перебирает такты внутри одной инструкции - всего с учётом клока получается 6 тактов:

1) CLK=N MEM=N - вывод нового PC на шину адреса

2) CLK=P MEM=N - тут может быть чтение триады инструкции и её декодировании, с сохранением флагов микрокода

3) CLK=N MEM=O - тут может быть выставление на шину адреса и данных чего-то в соответствии с флагами, снятыми с декодера инструкции

4) CLK=P MEM=O - тут может быть чтение из памяти либо регистров в соответствии с флагами, снятыми с декодера инструкции, в том числе запись регистра I произвольным числом

5) CLK=N MEM=P - тут может быть выставление на шину адреса чего-то ещё (опять же в соответствии с флагами), плюс инкремент регистра I либо его сброс

6) CLK=P MEM=P - тут опять чтение-запись плюс подготовка к переходу в случае JMP или LPCD

1) CLK=N MEM=N - вывод нового PC на шину адреса

2) CLK=P MEM=N - тут может быть чтение триады инструкции и её декодировании, с сохранением флагов микрокода

3) CLK=N MEM=O - тут может быть выставление на шину адреса и данных чего-то в соответствии с флагами, снятыми с декодера инструкции

4) CLK=P MEM=O - тут может быть чтение из памяти либо регистров в соответствии с флагами, снятыми с декодера инструкции, в том числе запись регистра I произвольным числом

5) CLK=N MEM=P - тут может быть выставление на шину адреса чего-то ещё (опять же в соответствии с флагами), плюс инкремент регистра I либо его сброс

6) CLK=P MEM=P - тут опять чтение-запись плюс подготовка к переходу в случае JMP или LPCD

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

Вобщем как-то так оно видится:

По идее вместо T0 можно задействовать T1 - тогда количество временных регистров уменьшится...

Потом вместо явных inc I и clr I можно просто в каждом машинном цикле на базе старого значения I выдавать новое значение I, которое будет запоминаться в конце

Code: Select all

_ _ _ _ _ _ _ _ _ _

CLK _| |_ _| |_ _| |_ _| |_ _| |_ _| |_ _| |_ _| |_ _| |_ _| |_ _

_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_|

_______ _______ _______

T0 _______| | _______| | _______| | ___

_______| |_______| |_______| |_______|

_______________________

T1 _______________________| |

_______________________| |___________

T2 ___________

_______________________________________________________________________|

^ ^ ^ ^ ^ ^

| | | | | |

| | | | | \--- Optional Read/Write, increment/clear I and storing PC+1

| | | | \------- Optional address bus

| | | \----------- Write/Read data

| | \--------------- Set something to address bus and/or date bus

| \------------------- Read triade from memory, decode and store microcode

\----------------------- PC on address bus

SAN:

I=OOO NNN A/DPn->m - - (I=OOO)

SAO:

I=OOO NNO A/DPo->m - - (I=OOO)

SAP:

I=OOO NNP A/DPp->m - - (I=OOO)

SAF:

I=OOO NON A ->F - - (I=OOO)

SPCD:

I=OOO NOO -> DP - - (I=OOO)

SAB:

I=OOO NOP A ->B - - (I=OOO)

SAL:

I=OOO NPN A ->L - - (I=OOO)

SAM:

I=OOO NPO A ->M - - (I=OOO)

SAH:

I=OOO NPP A ->H - - (I=OOO)

RLA:

I=OOO ONN A ->T0 RL ->A (I=OOO)

ADD:

I=OOO ONO A ->T0 AB ->A (I=OOO) set RFC

RRA:

I=OOO ONP A ->TO RR ->A (I=OOO)

LAI #:

I=OOO OON NPO ->I - - (I=NPP) inc I

I=NPP ttt m ->T0 T0 ->A (I=OOO) clr I

ADI #:

I=OOO OOO ONN ->I - - (I=ONO) inc I

I=ONO ttt m ->T0 AT ->A (I=OOO) clr I set RFC

OPA #:

I=OOO OOP ONP ->I - - (I=OON) inc I

I=OON ttt m ->T0 OA ->A (I=OOO) clr I set RFC

LDI # # #:

I=OOO OPN OPN ->I - - (I=OPO) inc I

I=OPO xxx m ->H - - (I=OPP) inc I

I=OPP yyy m ->M - - (I=PNN) inc I

I=PNN zzz m ->L - - (I=OOO) clr I

JMP # # #:

I=OOO OPO PNO ->I - - (I=PNP) inc I

I=PNP xxx m ->T1 - - (I=PON) inc I

I=PON yyy m ->T2 - - (I=POO) inc I

I=POO zzz m ->T3 TD ->PC (I=OOO) clr I store TD instead of PC+1

OPB # # #:

I=OOO OPP POP ->I - - (I=PPN) inc I

I=PPN xxx m ->T1 - - (I=PPO) inc I

I=PPO yyy m ->T2 - - (I=PPP) inc I

I=PPP zzz m ->T3 OB ->A (I=OOO) clr I set RFC

LAN:

I=OOO PNN DPn ->T0 T0 ->A (I=OOO)

LAO:

I=OOO PNO DPo ->T0 T0 ->A (I=OOO)

LAP:

I=OOO PNP DPp ->T0 T0 ->A (I=OOO)

LAF:

I=OOO PON F ->T0 T0 ->A (I=OOO)

LPCD:

I=OOO POO - - DP ->PC (I=OOO) store DP instead of PC+1

LAB:

I=OOO POP B ->T0 T0 ->A (I=OOO)

LAL:

I=OOO PPN L ->T0 T0 ->A (I=OOO)

LAM:

I=OOO PPO M ->T0 T0 ->A (I=OOO)

LAH:

I=OOO PPP H ->T0 T0 ->A (I=OOO)

Потом вместо явных inc I и clr I можно просто в каждом машинном цикле на базе старого значения I выдавать новое значение I, которое будет запоминаться в конце

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha

Поподбирал значения для I и пришёл вот к такой DDT задаче:

которая была успешно решена с помощью ddtc - получилось 80 DG403х для неоптимизированного варианта и 63 для оптимизированного (через ddtp):

Оптимальное решение имеет 49 полных троичных мультиплексоров и 33 полумультиплексора (17 E12 и 16 E21).

P.S. Для первого прототипа это всё можно сделать через двоичное ПЗУ...

Code: Select all

# Microcode for "3niti alpha"

#I OP =I' Flags

OOONNN=OOOPNNOOOOOOOOO

OOONNO=OOOPONOOOOOOOOO

OOONNP=OOOPPNOOOOOOOOO

OOONON=OOOOONPONOOOOOO

OOONOO=OOONONPOOOOOOPO

OOONOP=OOOOONPOPOOOOOO

OOONPN=OOOOONPPNOOOOOO

OOONPO=OOOOONPPOOOOOOO

OOONPP=OOOOONPPPOOOOOO

OOOONN=OOOOONNOOOONNOO

OOOONO=OOOOONNOOOONOOP

OOOONP=OOOOONNOOOONPOO

OOOOON=ONNOONPOOOOOOOO

OOOOOO=OONOONPOOOOOOOO

OOOOOP=OPNOONPOOOOOOOO

OOOOPN=PNNOONPOOOOOOOO

OOOOPO=PONOONPOOOOOOOO

OOOOPP=PPNOONPOOOOOOOO

OOOPNN=OOOPNONOONNOOOO

OOOPNO=OOOPOONOONNOOOO

OOOPNP=OOOPPONOONNOOOO

OOOPON=OOOOOPNONNNOOOO

OOOPOO=OOOOONPOOOOOONO

OOOPOP=OOOOOPNOPNNOOOO

OOOPPN=OOOOOPNPNNNOOOO

OOOPPO=OOOOOPNPONNOOOO

OOOPPP=OOOOOPNPPNNOOOO

#LAI

ONNXXX=OOONOOPNNNNOOOO

#ADI

OONXXX=OOONOOPNNOOPNOP

#OPA

OPNXXX=OOONOOPNNOOPOOP

#LDI

PNNXXX=PNONOOPPPOOOOOO

PNOXXX=PNPNOOPPOOOOOOO

PNPXXX=OOONOOPPNOOOOOO

#JMP

PONXXX=POONOOPNNOOOOOO

POOXXX=POPNOOPNOOOOOOO

POPXXX=OOONOOPNPOOOOON

#OPB

PPNXXX=PPONOOPNNOOOOOO

PPOXXX=PPPNOOPNOOOOOOO

PPPXXX=OOONOOPNPOOPPOP

#Flags:

#abus1/1 - PC,nothing,DPx

#abus1dp/1 - DPn,DPo,DPp used if abus1=DPx

#dbus1s/1 - A,mem,reg (source)

#dbus1d/1 - T1,mem,reg (destination)

#dbus1reg/2 - used if dbus1s=reg or dbus1d=reg (T1,T2,T3 instead of N,O,P)

#dbus2s/2 - T1,T2,T3,F,O,B,L,M,H

#dbus2o/2 - used if dbus2s=O (RL,AB,RR,A,A,A,AT,OA,OB)

#pcsto/1 - optional flag to copy PC to DP (P) or DP to PC (N)

#pcrfc/1 - optional flag to set RFC (P) or copy TD to PC (N)

Code: Select all

6 inputs detected (worst solution is 5460)

OLD 5|4|3|2|1|0 e12=81 e21=77 DG403=80

NEW 5|4|3|1|2|0 e12=76 e21=77 DG403=77

NEW 5|4|3|1|0|2 e12=77 e21=75 DG403=77

NEW 5|4|2|1|0|3 e12=77 e21=68 DG403=73

NEW 5|4|1|2|0|3 e12=73 e21=70 DG403=72

NEW 5|3|2|1|4|0 e12=74 e21=70 DG403=72

NEW 5|3|2|1|0|4 e12=67 e21=63 DG403=66

NEW 5|3|1|2|0|4 e12=62 e21=63 DG403=63

NEW 5|3|1|0|2|4 e12=63 e21=61 DG403=63

Optimal solution has 63 chips instead of 80

Ratio optimal/worst is 1%

103 functions were used

P.S. Для первого прототипа это всё можно сделать через двоичное ПЗУ...

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Микроархитектура 3niti alpha/beta

Для реализации расширенной системы команд 3niti beta надо ещё завести регистр SP, флаг копирвания туда-обратно, флаг инкремента-декремента SP и флаг использования SP для чтения/записи. Также ещё будет нужен флаг инкремента-декремента DP (схему инкремента-декремента можно сделать общей для PC, SP и DP).

P.S. Похоже надо писать эмулятор с возможностью задавать триты микрокода мышкой (онлайн?) или сделать эдакий компилятор микрокода, который на входе будет получать некое текстовое описание в человеческом виде, а на выходе будет выдавать описание для DDT...

P.S. Похоже надо писать эмулятор с возможностью задавать триты микрокода мышкой (онлайн?) или сделать эдакий компилятор микрокода, который на входе будет получать некое текстовое описание в человеческом виде, а на выходе будет выдавать описание для DDT...

-

Shaos

- Admin

- Posts: 25065

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Возможные микроархитектуры 3niti alpha/beta

Я когда этот микрокодовый подход придумывал в 2015 году, то хотел добиться чтобы большинство инструкций выполнялось бы за один цикл (три периода тактирующей пилы) и только сложные многотриадные инструкций занимали бы несколько циклов (выше можно видеть, что это LAI, ADI, OPA, LDI, JMP и OPB). Возможно я тогда переупростил и кое-какие из "простых" инструкций должны занимать больше одного цикла - например ADD т.к. она кроме сложения ещё меняет состояние двух флагов. Для 3niti beta добавятся несколько ещё более сложных "многоцикловых" инструкций типа CALL и RET, которые подразумевают инкремент-декремент 9-тритового регистра SP и многократное обращение к памяти.

Вместо непонятного регистра I я ещё тогда пошёл по пути адресации микропрограмм кодом инструкции - в простейшем случае инструкция выполнялась бы микропрограммой, расположенной по адресу OOOxxx, но при необходимости исполнение уходило бы на другой адрес - сейчас можно этот подход несколько упростить и сделать более логичным, задавая адрес перескока не тремя тритами устанавливающими старшие 3 трита из 6, а скажем четырьмя, причём все 4 трита будут использованы для адресации микропрограмм (при этом простейшие микропрограммы будут расположены по адресам Oxxx).

Например по адресу ONNN в памяти микропрограмм будет микропрограмма для инструкции SAN (сохранить A по адресу DPn):

- установить на шине адреса 9-тритное значение из DPn

- выложить на шину данных 3-тритное значение из A и сформировать строб записи

далее будет общая часть для всех окончаний микропрограмм:

- установить на шине адреса 9-тритное значение проинкрементированного PC либо 9-тритное значение из TP (для инструкций передачи управления)

- сформировать строб чтения из памяти, чтобы прочитать код следующей инструкции в регистр T0

- выполнить следующую микропрограмму начиная с адреса O|T0

и т.д.

Микропрограмма для выполнения инструкции ADD должна быть расположена по адресу OONO:

- подключить второй вход сумматора к регистру B (первый вход всегда будет запитан от регистра A)

- запомнить выход сумматора (T2 для суммы и T3 для флагов?)

- записать сохранённые данные в регистры A и F

- установить на шине адреса 9-тритное значение проинкрементированного PC

- сформировать строб чтения из памяти, чтобы прочитать код следующей инструкции в регистр T0

- выполнить следующую микропрограмму начиная с адреса O|T0

В случае ADI микропрограмма по адресу OOOO должна сделать чуть больше, чем микропрограмма для ADD:

- подключить второй вход сумматора к регистру Т1 (первый вход всегда будет запитан от регистра A)

- установить на шине адреса 9-тритное значение проинкрементированного PC

- сформировать строб чтения из памяти, чтобы прочитать следующую триаду в регистр T1

- запомнить выход сумматора (T2 для суммы и T3 для флагов?)

- записать сохранённые данные в регистры A и F

- установить на шине адреса 9-тритное значение проинкрементированного PC

- сформировать строб чтения из памяти, чтобы прочитать код следующей инструкции в регистр T0

- выполнить следующую микропрограмму начиная с адреса O|T0

Одна строчка тритов микроинструкции должна описывать то, что надо сделать за 3 периода тактовой пилы (или синусоиды) - простые инструкции типа SAN должны уложиться в одну микроинструкцию, а вот ADD наверное уже не уложится т.е. из первой микроинструкции этой микропрограммы надо будет перескочить за пределы зоны Oxxx для выполнения остальных микроинструкций этой микропрограммы. Перескок, как я уже писал выше, будет происходить на 4-тритный адрес в памяти микропрограмм - можно скажем принять, что если адрес перескока Oxxx, то это означает перескок на O|T0 (и для 3niti beta наверное можно поддержать спец.значение Nxxx, означающее перескок на N|T1 если старший трит регистра T1 равен N - это для реализации новых инструкций), а перескоки на Pxxx будут брать все 4 трита из кода микроинструкции (также все 4 трита будут браться в случае Nxxx когда старший трит регистра T1 был не равен N, т.е. был равен O или P).

P.S. Хотя всё-таки вычитка инструкции из памяти должна быть в начале цикла, а не в конце - простейшая микропрограмма в одну микростроку может выглядеть примерно так:

- прочитать триаду с шины данных (нужный PC к этому моменту уже должен быть подключен к шине адреса) и защёлкнуть её в регистре T0

- передать управление на адрес микропрограммы O|T0

- подключить регистр источник и регистр приёмник к внутренней шине данных

- осуществить строб записи для сохранения необходимых данных и если надо флагов, а также обновить PC (в общем случае инкрементировать)

Вместо непонятного регистра I я ещё тогда пошёл по пути адресации микропрограмм кодом инструкции - в простейшем случае инструкция выполнялась бы микропрограммой, расположенной по адресу OOOxxx, но при необходимости исполнение уходило бы на другой адрес - сейчас можно этот подход несколько упростить и сделать более логичным, задавая адрес перескока не тремя тритами устанавливающими старшие 3 трита из 6, а скажем четырьмя, причём все 4 трита будут использованы для адресации микропрограмм (при этом простейшие микропрограммы будут расположены по адресам Oxxx).

Например по адресу ONNN в памяти микропрограмм будет микропрограмма для инструкции SAN (сохранить A по адресу DPn):

- установить на шине адреса 9-тритное значение из DPn

- выложить на шину данных 3-тритное значение из A и сформировать строб записи

далее будет общая часть для всех окончаний микропрограмм:

- установить на шине адреса 9-тритное значение проинкрементированного PC либо 9-тритное значение из TP (для инструкций передачи управления)

- сформировать строб чтения из памяти, чтобы прочитать код следующей инструкции в регистр T0

- выполнить следующую микропрограмму начиная с адреса O|T0

и т.д.

Микропрограмма для выполнения инструкции ADD должна быть расположена по адресу OONO:

- подключить второй вход сумматора к регистру B (первый вход всегда будет запитан от регистра A)

- запомнить выход сумматора (T2 для суммы и T3 для флагов?)

- записать сохранённые данные в регистры A и F

- установить на шине адреса 9-тритное значение проинкрементированного PC

- сформировать строб чтения из памяти, чтобы прочитать код следующей инструкции в регистр T0

- выполнить следующую микропрограмму начиная с адреса O|T0

В случае ADI микропрограмма по адресу OOOO должна сделать чуть больше, чем микропрограмма для ADD:

- подключить второй вход сумматора к регистру Т1 (первый вход всегда будет запитан от регистра A)

- установить на шине адреса 9-тритное значение проинкрементированного PC

- сформировать строб чтения из памяти, чтобы прочитать следующую триаду в регистр T1

- запомнить выход сумматора (T2 для суммы и T3 для флагов?)

- записать сохранённые данные в регистры A и F

- установить на шине адреса 9-тритное значение проинкрементированного PC

- сформировать строб чтения из памяти, чтобы прочитать код следующей инструкции в регистр T0

- выполнить следующую микропрограмму начиная с адреса O|T0

Одна строчка тритов микроинструкции должна описывать то, что надо сделать за 3 периода тактовой пилы (или синусоиды) - простые инструкции типа SAN должны уложиться в одну микроинструкцию, а вот ADD наверное уже не уложится т.е. из первой микроинструкции этой микропрограммы надо будет перескочить за пределы зоны Oxxx для выполнения остальных микроинструкций этой микропрограммы. Перескок, как я уже писал выше, будет происходить на 4-тритный адрес в памяти микропрограмм - можно скажем принять, что если адрес перескока Oxxx, то это означает перескок на O|T0 (и для 3niti beta наверное можно поддержать спец.значение Nxxx, означающее перескок на N|T1 если старший трит регистра T1 равен N - это для реализации новых инструкций), а перескоки на Pxxx будут брать все 4 трита из кода микроинструкции (также все 4 трита будут браться в случае Nxxx когда старший трит регистра T1 был не равен N, т.е. был равен O или P).

P.S. Хотя всё-таки вычитка инструкции из памяти должна быть в начале цикла, а не в конце - простейшая микропрограмма в одну микростроку может выглядеть примерно так:

- прочитать триаду с шины данных (нужный PC к этому моменту уже должен быть подключен к шине адреса) и защёлкнуть её в регистре T0

- передать управление на адрес микропрограммы O|T0

- подключить регистр источник и регистр приёмник к внутренней шине данных

- осуществить строб записи для сохранения необходимых данных и если надо флагов, а также обновить PC (в общем случае инкрементировать)