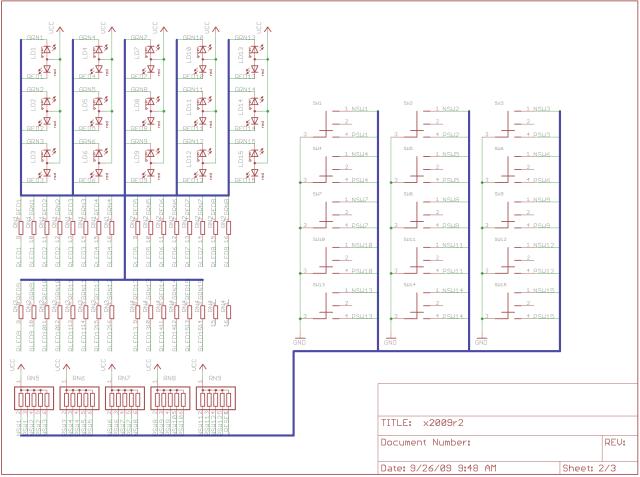

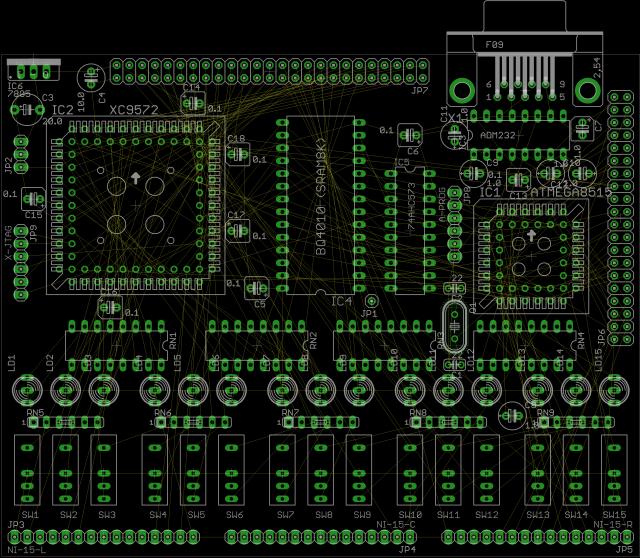

Редизайн платы для AVR ATMEGA8515 от Atmel (в PLCC-корпусе) и CPLD XC9572 от Xilinx (тоже в PLCC). Кроме того на плате будет 8К энергонезависимой памяти (SRAM со встроенной батарейкой на 10 лет), последовательный порт (для общения с компьютером), а также некоторые разъёмы (включая порт NI-15), опциональные переключаетели и светодиоды (совмещенные красно-зленые либо обычные, но в два раза больше).

Плату можно будет собрать в двух вариантах:

1) NedoPC-90-B/T - плата для эмуляции троичного компьютера 3niti alpha с панелью управления как вот тут;

2) NedoPC-90-B/X - универсальная плата с AVR, CPLD и кучей I/O.

Также возможноы следующие нестандартные сборки:

- NedoPC-90-B/XX - универсальная сдвоенная плата (когда квадрат не распилен на треугольные половинки);

- NedoPC-90-B/XXX - универсальная строенная плата (когда квадрат не распилен на треугольные половинки и в него сверху воткнута третья треугольная плата);

- NedoPC-90-B/ТТ - сдвоенный троичный компьютер;

- NedoPC-90-B/ТТТ - строенный троичный компьютер;

Возможна сборка 5-вольтовых или 3.3-вольтовых вариантов

P.S. Треугольник не получается, так что плата будет называться просто Xavroska-2009

P.S. А троичный компьютер, собранный на её основе (NedoPC-90-B/T) будет называться "3niti alpha simula"

Xavroska-2009 (второе приближение)

Moderator: Shaos

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Xavroska-2009 (второе приближение)

Last edited by Shaos on 27 Sep 2009 00:04, edited 4 times in total.

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

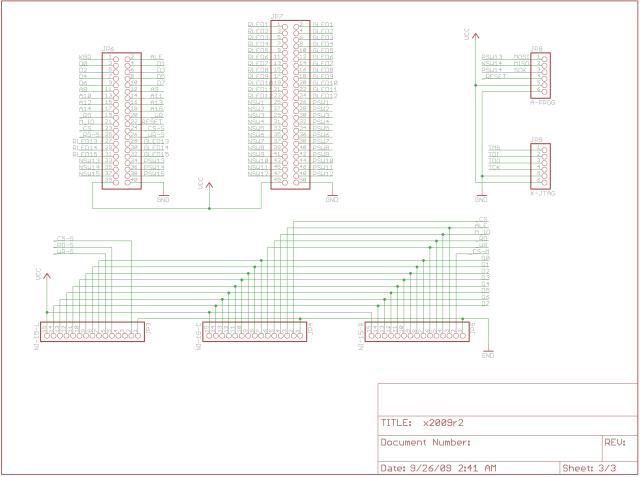

Последняя версия AVROS (и соответственно система Xavroska 1.0) поддерживает режим NI_15_BUS в случае атмеги-8515 (см. viewtopic.php?t=8259 ), когда отдельные сигналы NI-15 не эмулируются (как в NedoPC-90 на атмеге-8535), а подключаются к шине внешней памяти (у которой младшие 8 бит мультиплексированы и имеется сигнал ALE - прямо как в NI-15). Однако мне не совсем нравится способ подключения памяти с точки зрения AVROS в этом режиме - когда A14 идёт на M_IO, а A15 - разрешает/запрещает порт NI15, при этом мы имеем в памяти чередующиеся области M и IO (старшие адреса памяти при этом переключаются отдельными ногами атмеги). С другой стороны у нас пока только 8К памяти и A14/A15 (и A13 кстати тоже) не используются по прямому назначению и могут быть заюзаны в таком варианте.

На самом деле адресный сигнал A13 занимать нельзя, т.к. чтобы увидеть начало 8K памяти нам надо смотреть во вторую копию (распологающуюся в адресном пространстве 0x2000...0x3FFF) - т.е. A13 не будет использоваться вообще!

А вот адресные сигналы A14 и A15 могут быть свободны и будут переключать 4 области:

00 - память (M) или внутренние регистры в CPLD (IO);

01 - правый разъём NI-15 master (опциональный ряд контактов для втыкания в бред-боард или другую такую же плату);

10 - левый разъём NI-15 slave (опциональное гнездо для втыкания в него устройств либо другой такой же платы);

11 - центральный разъём NI-15 (который может быть либо гнездом, либо рядом контактов, либо вообще может отсутствовать, если плату не предполагается использовать совместно с шиной NI-15).

На самом деле адресный сигнал A13 занимать нельзя, т.к. чтобы увидеть начало 8K памяти нам надо смотреть во вторую копию (распологающуюся в адресном пространстве 0x2000...0x3FFF) - т.е. A13 не будет использоваться вообще!

А вот адресные сигналы A14 и A15 могут быть свободны и будут переключать 4 области:

00 - память (M) или внутренние регистры в CPLD (IO);

01 - правый разъём NI-15 master (опциональный ряд контактов для втыкания в бред-боард или другую такую же плату);

10 - левый разъём NI-15 slave (опциональное гнездо для втыкания в него устройств либо другой такой же платы);

11 - центральный разъём NI-15 (который может быть либо гнездом, либо рядом контактов, либо вообще может отсутствовать, если плату не предполагается использовать совместно с шиной NI-15).

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Подключение атмеги-8515:

Code: Select all

ATMEGA8515 (PLCC-44) for NedoPC-90-B:

Pin 01: NC Not connected

Pin 02: PB0 (OC0/T0) Red LED 13 | External IO

Pin 03: PB1 (T1) Green LED 13 | External IO

Pin 04: PB2 (AIN0) Red LED 14 | External IO

Pin 05: PB3 (AIN1) Green LED 14 | External IO

Pin 06: PB4 (SS) Switch 13- | External IO

Pin 07: PB5 (MOSI) Switch 13+ | Prog MOSI | External IO

Pin 08: PB6 (MISO) Switch 14- | Prog MISO | External IO

Pin 09: PB7 (SCK) Switch 14+ | Prog SCK | External IO

Pin 10: RESET Prog RESET + reset scheme | External IO

Pin 11: PD0 (RXD) Serial port RxD

Pin 12: NC Not connected

Pin 13: PD1 (TXD) Serial port TxD

Pin 14: PD2 (INT0) Optional 3.3V keyboard | External IO

Pin 15: PD3 (INT1) M_IO (NI-15) | External IO

Pin 16: PD4 (XCK) Red LED 15 | External IO

Pin 17: PD5 (OC1A) Green LED 15 | External IO

Pin 18: PD6 (_WR) _WR (NI-15) + Memory _WE | External IO

Pin 19: PD7 (_RD) _RD (NI-15) + Memory _OE | External IO

Pin 20: XTAL2 16 MHz crystal (2)

Pin 21: XTAL1 16 MHz crystal (1)

Pin 22: GND Ground

Pin 23: NC Not connected

Pin 24: PC0 (A8) Memory A8 | External IO

Pin 25: PC1 (A9) Memory A9 | External IO

Pin 26: PC2 (A10) Memory A10 | External IO

Pin 27: PC3 (A11) Memory A11 | External IO

Pin 28: PC4 (A12) Memory A12 | External IO

Pin 29: PC5 (A13) External IO

Pin 30: PC6 (A14) NIA0 | External IO

Pin 31: PC7 (A15) NIA1 | External IO

Pin 32: PE2 (OC1B) Switch 15+ | External IO

Pin 33: PE1 (ALE) ALE (NI-15) | External IO

Pin 34: NC Not connected

Pin 35: PE0 (ICP/INT2) Switch 15- | External IO

Pin 36: PA7 (ADC7) D7 (NI-15) | External IO

Pin 37: PA6 (ADC6) D6 (NI-15) | External IO

Pin 38: PA5 (ADC5) D5 (NI-15) | External IO

Pin 39: PA4 (ADC4) D4 (NI-15) | External IO

Pin 40: PA3 (ADC3) D3 (NI-15) | External IO

Pin 41: PA2 (ADC2) D2 (NI-15) | External IO

Pin 42: PA1 (ADC1) D1 (NI-15) | External IO

Pin 43: PA0 (ADC0) D0 (NI-15) | External IO

Pin 44: VCC +5 Volts

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Не хватает ног у CPLD - придётся снаружи ещё регистр-защёлку 74AHC573 ставить между атмегой и памятью (получается что можно вообще без CPLD схему собрать). И левый NI-15 (который Slave) будет не полноценный - он игнорирует внешние сигналы ALE и M_IO (идущие от внешнего мастера), но в-принципе одного байта на ввод и вывод должно быть достаточно для обмена между двумя идентичными платами:Shaos wrote:Последняя версия AVROS (и соответственно система Xavroska 1.0) поддерживает режим NI_15_BUS в случае атмеги-8515 (см. viewtopic.php?t=8259 ), когда отдельные сигналы NI-15 не эмулируются (как в NedoPC-90 на атмеге-8535), а подключаются к шине внешней памяти (у которой младшие 8 бит мультиплексированы и имеется сигнал ALE - прямо как в NI-15). Однако мне не совсем нравится способ подключения памяти с точки зрения AVROS в этом режиме - когда A14 идёт на M_IO, а A15 - разрешает/запрещает порт NI15, при этом мы имеем в памяти чередующиеся области M и IO (старшие адреса памяти при этом переключаются отдельными ногами атмеги). С другой стороны у нас пока только 8К памяти и A14/A15 (и A13 кстати тоже) не используются по прямому назначению и могут быть заюзаны в таком варианте.

На самом деле адресный сигнал A13 занимать нельзя, т.к. чтобы увидеть начало 8K памяти нам надо смотреть во вторую копию (распологающуюся в адресном пространстве 0x2000...0x3FFF) - т.е. A13 не будет использоваться вообще!

А вот адресные сигналы A14 и A15 могут быть свободны и будут переключать 4 области:

00 - память (M) или внутренние регистры в CPLD (IO);

01 - правый разъём NI-15 master (опциональный ряд контактов для втыкания в бред-боард или другую такую же плату);

10 - левый разъём NI-15 slave (опциональное гнездо для втыкания в него устройств либо другой такой же платы);

11 - центральный разъём NI-15 (который может быть либо гнездом, либо рядом контактов, либо вообще может отсутствовать, если плату не предполагается использовать совместно с шиной NI-15).

Code: Select all

XC9572 (PLCC84) for NedoPC-90-B:

Pin 01: 1-02 Red LED 1 | External I/O (optional)

Pin 02: 1-05 Green LED 1 | External I/O (optional)

Pin 03: 1-06 Red LED 2 | External I/O (optional)

Pin 04: 1-01 Green LED 2 | External I/O (optional)

Pin 05: 1-08 Red LED 3 | External I/O (optional)

Pin 06: 1-03 Green LED 3 | External I/O (optional)

Pin 07: 1-04 Red LED 4 | External I/O (optional)

Pin 08: (GND) Ground

Pin 09: 1-09 (GCK1) ALE (NI-15)

Pin 10: 1-11 (GCK2) _RD (NI-15)

Pin 11: 1-07 Green LED 4 | External I/O (optional)

Pin 12: 1-14 (GCK3) _WR (NI-15)

Pin 13: 1-10 M_IO (NI-15)

Pin 14: 1-15 Red LED 5 | External I/O (optional)

Pin 15: 1-17 Green LED 5 | External I/O (optional)

Pin 16: (GND) Ground

Pin 17: 3-02 Red LED 6 | External I/O (optional)

Pin 18: 1-12 Green LED 6 | External I/O (optional)

Pin 19: 3-05 Red LED 7 | External I/O (optional)

Pin 20: 1-13 Green LED 7 | External I/O (optional)

Pin 21: 3-08 Red LED 8 | External I/O (optional)

Pin 22: (VCCIO) +5 Volts | +3.3 Volts (optional)

Pin 23: 1-16 Green LED 8 | External I/O (optional)

Pin 24: 1-18 Red LED 9 | External I/O (optional)

Pin 25: 3-01 Green LED 9 | External I/O (optional)

Pin 26: 3-09 Red LED 10 | External I/O (optional)

Pin 27: (GND) Ground

Pin 28: (TDI)

Pin 29: (TMS)

Pin 30: (TCK)

Pin 31: 3-03 Green LED 10 | External I/O (optional)

Pin 32: 3-04 NIA0

Pin 33: 3-11 NIA1

Pin 34: 3-06 Red LED 11 | External I/O (optional)

Pin 35: 3-07 Green LED 11 | External I/O (optional)

Pin 36: 3-14 Red LED 12 | External I/O (optional)

Pin 37: 3-15 Green LED 12 | External I/O (optional)

Pin 38: (VCCINT) +5 Volts

Pin 39: 3-17 Switch 1- | External I/O (optional)

Pin 40: 3-10 Switch 1+ | External I/O (optional)

Pin 41: 3-12 Switch 2- | External I/O (optional)

Pin 42: (GND) Ground

Pin 43: 3-13 Switch 2+ | External I/O (optional)

Pin 44: 4-02 D0 (NI-15)

Pin 45: 3-16 Switch 3- | External I/O (optional)

Pin 46: 4-01 D1 (NI-15)

Pin 47: 4-05 D2 (NI-15)

Pin 48: 4-08 D3 (NI-15)

Pin 49: (GND) Ground

Pin 50: 4-09 D4 (NI-15)

Pin 51: 4-03 D5 (NI-15)

Pin 52: 4-04 D6 (NI-15)

Pin 53: 4-11 D7 (NI-15)

Pin 54: 4-06 Switch 3+ | External I/O (optional)

Pin 55: 4-07 Switch 4- | External I/O (optional)

Pin 56: 4-14 Switch 4+ | External I/O (optional)

Pin 57: 4-10 Switch 5- | External I/O (optional)

Pin 58: 4-12 Switch 5+ | External I/O (optional)

Pin 59: (TDO)

Pin 60: (GND) Ground

Pin 61: 4-13 Switch 6- | External I/O (optional)

Pin 62: 4-16 Switch 6+ | External I/O (optional)

Pin 63: 2-01 _CE (RAM)

Pin 64: (VCCIO) +5 Volts | +3.3 Volts (optional)

Pin 65: 4-15 Switch 7- | External I/O (optional)

Pin 66: 4-17 Switch 7+ | External I/O (optional)

Pin 67: 2-03 Switch 8- | External I/O (optional)

Pin 68: 2-04 Switch 8+ | External I/O (optional)

Pin 69: 2-02 Switch 9- | External I/O (optional)

Pin 70: 2-05 Switch 9+ | External I/O (optional)

Pin 71: 2-06 Switch 10- | External I/O (optional)

Pin 72: 2-08 Switch 10+ | External I/O (optional)

Pin 73: (VCCINT) +5 Volts

Pin 74: 2-09 (GSR) Reset

Pin 75: 2-10 Switch 11- | External I/O (optional)

Pin 76: 2-07 (GTS1) Switch 11+ | External I/O (optional)

Pin 77: 2-11 (GTS2) Switch 12- | External I/O (optional)

Pin 78: (VCCINT) +5 Volts

Pin 79: 2-12 Switch 12+ | External I/O (optional)

Pin 80: 2-13 Input _RD-S (NI-15) | External I/O (optional)

Pin 81: 2-14 Input _WR-S (NI-15) | External I/O (optional)

Pin 82: 2-16 Input _CS-S (NI-15) | External I/O (optional)

Pin 83: 2-15 _CS-M (NI-15) | External I/O (optional)

Pin 84: 2-17 _CS (NI-15) | External I/O (optional)

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

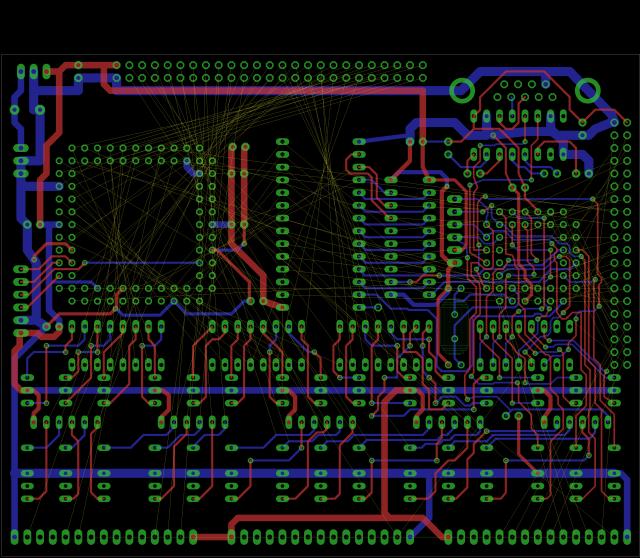

Вот - раскидал компоненты:Shaos wrote:Пытаюсь разводить - мало того что треугольника не получается, так ещё и практически все пределы стандартной версии Eagle заполнил (16 x 10 см)

P.S. Вроде уплотнил до 12.7 x 10 см (будет дешевле изготовить)

Попытаюсь развести в 2 слоя - если серъёзно застряну, то перейду в 4...

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Xavroska-2009 будет передизаёнена позже (без троичных выключателей-светодиодов), а для постройки 3niti alpha simula я решил использовать другой подход - модульный

Я тут за главного - если что шлите мыло на me собака shaos точка net