В сумматор одни стробируемые тактовым сигналом данные поступают с переключателя, другие - из того же регистра, в котором будет результат. Оно может складывать так: сначала загружается первое слагаемое, складываясь с изначальным нулём попадает в регистр, а потом второе слагаемое складывается с идущим из "кольца" первым.

Вторую часть ТМ2 просто последовательно подключил к ТМ8, и общий регистр сумматора стал пятибитным.

При этом выяснилось, что если на триггере переноса форсировать "1", то на выходе вместо сложения будет побитовое XNOR, форсировать "0" - побитовое XOR. И раз есть сложение и можно делать инверсию, то реализуемы и другие операции?

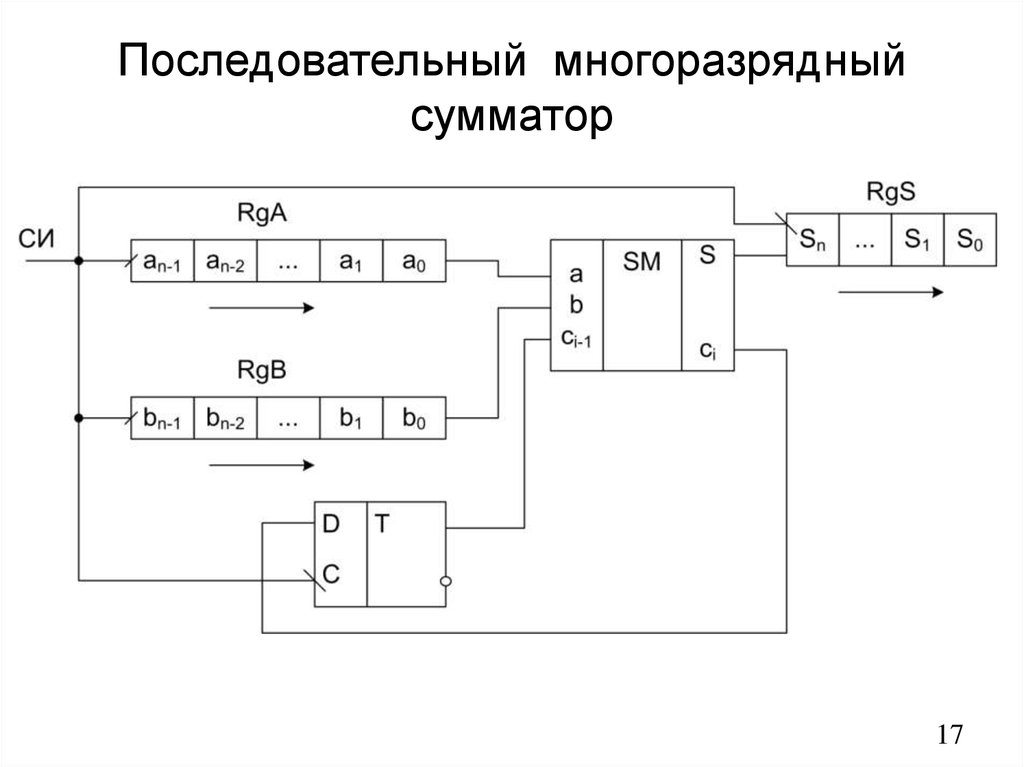

Ввиду закрытости магазинов на НГ праздники, решил собрать что-то подобное на том, что имелось: В реальности столкнулся с дребезгом тактовой кнопки, пришлось на оставшихся элементах ЛА3 делать триггер и использовать кнопку из мышки для выхода из ситуации: Да, обычно сумматоры последовательного действия работают так:

И, как ни крути, ощущение, что где-то про это много всего интересного написали уже давно.

Есть ли какая-нибудь литература/информация на эту тему? Про EDUC-8 ещё почитаю, но он один как-то пока не особо цепляет (но счётчик команд зашёл