Дешифрация кода команды CPU

Moderator: Lavr

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

Shaos - тут уже дело просто в принципе. По прикидкам схемотехника самодельного ЦП,

совместимого с К580ВМ80, получается сложной и объёмной.

Я прицеливаюсь уместиться сугубо на двойной стандартной макетке.

При таком объёме хорош только проц со своей короткой системой команд.

Сейчас тупик в том - какой набор команд оставить. А схемотехника местами

прорисовывается весьма красивая.

совместимого с К580ВМ80, получается сложной и объёмной.

Я прицеливаюсь уместиться сугубо на двойной стандартной макетке.

При таком объёме хорош только проц со своей короткой системой команд.

Сейчас тупик в том - какой набор команд оставить. А схемотехника местами

прорисовывается весьма красивая.

-

aav8

- Maniac

- Posts: 287

- Joined: 05 Nov 2008 19:47

- Location: 81.28.208.238

"А не посчитать-ли нам уважаемые кроты" (цитата из мультфильма Дюймовочка)Lavr wrote:Shaos - тут уже дело просто в принципе. По прикидкам схемотехника самодельного ЦП,

совместимого с К580ВМ80, получается сложной и объёмной.

Я прицеливаюсь уместиться сугубо на двойной стандартной макетке.

При таком объёме хорош только проц со своей короткой системой команд.

Сейчас тупик в том - какой набор команд оставить. А схемотехника местами

прорисовывается весьма красивая.

580ИК80 содержит около 5000 транзистров.

ЛА3 в одном элементе около 5-и транзистров, т.е. в одном корпусе

20 транзисторов.

5000/20=250 корпусов.

Если учесть, что в логике половина из 5-и транзистров не учавствует (для обеспечения выхода с заданной нагрузочной мощьностью), можно смело увеличить кол-во микросхем вдвое.

...

Используем регистры, счетчики двухпортовую память, АЛУ ...

примерно вдвое сокращается кол-во микросхем.

...

где-то как-то читал, что внутри ИК80 все регистры динамические (т.е. все теряется при тактовой частоте ~0Гц (проверьте пж-ста у кого есть такая возможность)) - 1 бит - 1 транзистртор, т.е. чтобы получилось ~5000 транзистров - придется увеличить кол-во корпусов...

---------------------

Конечно это прикидки, и я ошибаюсь примерно на пол-порядка/порядок...

Процессор Э60 на рассыпухе занимет примерно 0.5*0.5*0.3м.

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

Это действительно так и есть, проверять не надо. Об этом, в частности,aav8 wrote:внутри ИК80 все регистры динамические (т.е. все теряется при тактовой частоте ~0Гц (проверьте пж-ста у кого есть такая возможность))

Хоровиц и Хилл пишут, а я им верю.

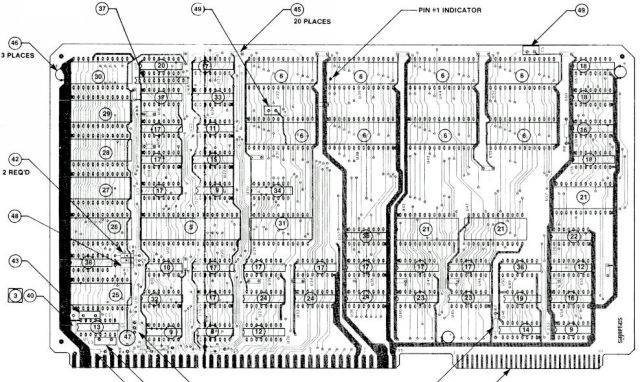

Тоже излишне - здесь у нас была ссылка на 580-й на мелкой логике. Я еёaav8 wrote:"А не посчитать-ли нам уважаемые кроты" (цитата из мультфильма Дюймовочка)

скачивал и смотрел внимательно.

http://tech-systems-labs.com/booksdata/ ... mulMan.pdf

Прежде чем изобрести велосипед, я по привычке просматриваю источники и

прототипы. Мне вполне уже понятно, что мой "велосипед" , пожалуй будет плох.

Остаётся только убедить себя, что в нём будет хоть какой-то смысл.

К примеру - я не леплю античных статуй just for fun, я в них и в реальных

не вижу смысла. А есть люди - лепят...

Last edited by Lavr on 10 Mar 2011 16:18, edited 1 time in total.

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

Что-то прям зацепило меня - где я уже что-то похожее слышал...aav8 wrote:можно не придумывать как реализовать в железе систему команд какого-либо процессора, а загружать нужный микрокод.

А вот где оказывается:

viewtopic.php?t=9177&postdays=0&postorder=asc&start=45

Не по кругу ли мы уже пошли?Shaos wrote:Склоняюсь я к мысли, что 6502/8085 процессор должен быть подгружаем как микропрограмма внутрь нашего гибридного процессора - в таком случае мы даём ещё одну степень свободы пользователю - при желании он сможет написать свою микропрограмму по своей собственной спецификации своего процессора

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

aav8

- Maniac

- Posts: 287

- Joined: 05 Nov 2008 19:47

- Location: 81.28.208.238

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

Я с ними вобще не работал, но везде читаю примерно вот такое:

Вот при этом, наверное, страницы по 256 байт...Индексные регистры позволили расширить доступные способы адресации за счет страничной организации памяти: 8-битовое содержимое X/Y выступало либо в качестве смещения в диапазоне от -128 до +128 относительно содержимого счетчика команд, либо использовалось как короткий физической адрес в так называемой "нулевой" странице (ячейки оперативной памяти с адресами 0--255), что значительно увеличивало скорость выполнения многих "правильно" написанных программ. Существенным отличием от "традиционно" принятой была и реализация стека -- он размещался в странице памяти с номером 1 (ячейки ОЗУ с адресами в диапазоне 256--511) и, соответственно, имел ограниченную глубину. Впоследствии по этому же принципу будут реализованы стеки большинства стандартных де-факто микроконтроллеров.

Система команд 6502 включала интересные короткие переходы (в пределах 256-байтовой страницы), длинные переходы между страницами и вызовы подпрограмм (естественно, с автоматическим сохранением значения счетчика команд на стеке), небольшой набор стандартных арифметических и логических операций и ряд уникальных, "намертво привязанных" к страничной архитектуре, очень удобных для программиста команд.

-

jdigreze

- God

- Posts: 1388

- Joined: 02 Jan 2006 02:28

- Location: Abakan

С этими процессорами не работал, но видимо идёт речь про релятивные переходы, типа jr в z80. С учётом того, что помимо релятивных переходов используются индексы, то скорее всего адрес на шине выставляется как сумма непосредственно указателя адреса и смещения. Т.е. адресная шина связана с регистрами через промежуточный 16бит сумматор. А про границы забей, там же не сегментированная модель по типу 8086. С другой стороны в 8086 точно также стоит сумматор, только на 20бит и сложение идет со смещением 4 бита для указателя сегмента.

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

Что-то все, кто сами не работали, мне дают прикольные советы.jdigreze wrote:С этими процессорами не работал... А про границы забей

А между тем, если почитать систему команд 6502 на проблемы пересечения

границ страниц явно указывается, и это я хочу чётко выяснить.

[url]http://www.emuverse.ru/wiki/MOS_Technology_6502/Система_команд[/url]Отличия NMOS и CMOS вариантов

Индексная адресация при пересечении границы страницы:

- NMOS: Дополнительное чтение по неправильному адресу;

- CMOS: Дополнительное чтение последнего байта инструкции;

Переход по косвенному адресу, когда операнд пересекает границу страницы (xxFFH):

- NMOS: Второй байт берется из первого байта текущей страницы;

- CMOS: Второй байт берется со следующей страницы, ко времени исполнения добавляется 1 такт.

-

Shaos

- Admin

- Posts: 24973

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

jdigreze

- God

- Posts: 1388

- Joined: 02 Jan 2006 02:28

- Location: Abakan

-

Lavr

- Supreme God

- Posts: 16922

- Joined: 21 Oct 2009 08:08

- Location: Россия

Не хочу сказать, что собираюсь что-то делать с 6502, просто его схемотехника,

отражается в его системе команд, а так как 6502 прост - схемотехника заимствуется

в различных самодельных ЦПУ. И суть вот в чем - регистровый пул схемотехнически

удобно сделать 8-разрядными. В этом случае программный счетчик получится как PC(Low)

и PC(Hi). Младший - указатель в странице 256 байт, старший - по сути перключатель

страниц (или банков - как в микроконтроллерах).

Команды удобно выровнять, скажем, на 2 байта. В этом случае PC(Low) и PC(Hi) загружаются

раздельно, а одновременно на шину выставляются только в случаях вызовов и переходов.

Не все команды дотягивают до 2-х байт. Однобайтные тоже приемлемы. Вот тут и возникает

вопрос - как поступать, если 2-байтная команда не выровняется на границу 256 байт.

отражается в его системе команд, а так как 6502 прост - схемотехника заимствуется

в различных самодельных ЦПУ. И суть вот в чем - регистровый пул схемотехнически

удобно сделать 8-разрядными. В этом случае программный счетчик получится как PC(Low)

и PC(Hi). Младший - указатель в странице 256 байт, старший - по сути перключатель

страниц (или банков - как в микроконтроллерах).

Команды удобно выровнять, скажем, на 2 байта. В этом случае PC(Low) и PC(Hi) загружаются

раздельно, а одновременно на шину выставляются только в случаях вызовов и переходов.

Не все команды дотягивают до 2-х байт. Однобайтные тоже приемлемы. Вот тут и возникает

вопрос - как поступать, если 2-байтная команда не выровняется на границу 256 байт.