VituZz wrote: Но только за один такт - по фронту загрузить нужные "приёмники" все сразу, по спаду - выгрузить результат. Но, блин, никак не получается посидеть над идеей достаточное количество времени, может, это и хрень полная

...

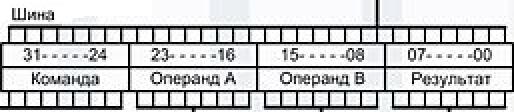

Ширина шины микрокоманд, как мне кажется, достаточно дешёвый ресурс. Нужно "переложить на её плечи" как можно больше работы в схеме.

Виталий, я сначала решал более нищебродскую задачу - сократить 2 микрухи ОЗУ

до одной.

Но все мучения подсказали мне - RISC не получится так, а CISC - усложнит мне

устройство управления и синхронизации, для разных длин команд.

Сейчас у меня всё четко аппаратно уложилось в один цикл - FETCH+ВЫПОЛНЕНИЕ.

Я набросал систему команд и оказалось, что похоже на PDP-8, кроме вот таких "диких"

команд...

Раз уж я не смог ужаться до 1 микрухи ОЗУ, решил юзать обе ОЗУ - на полную!

И оказалось - что аппаратно больше НИЧЕГО добавлять не надо!

Получается на первый взгляд всё очень удобно аппаратно...

Конечно, микрокоманды переписать придется и цепи микропрограммного

управления пересмотреть.

Но из тупика я вроде вышел - помогла фраза из текстов про PDP-8 - "максимально использовать

то, что даже для этой цели не предназначено".

Не дословно - но мысль такая.

Но прежде чем дальше биться лбом в открытые двери хочу "пощупать" команды PDP-8,

чтобы оценить свою систему команд.