спасибо, Piotr.

piotr433 wrote:Мне в руки попал микропроцессор Т36ВМ1-2 с датой выпуска 9109, который передаёт по шине ЖКИ восемь бит данных.

таки, не совсем 8-мь бит.

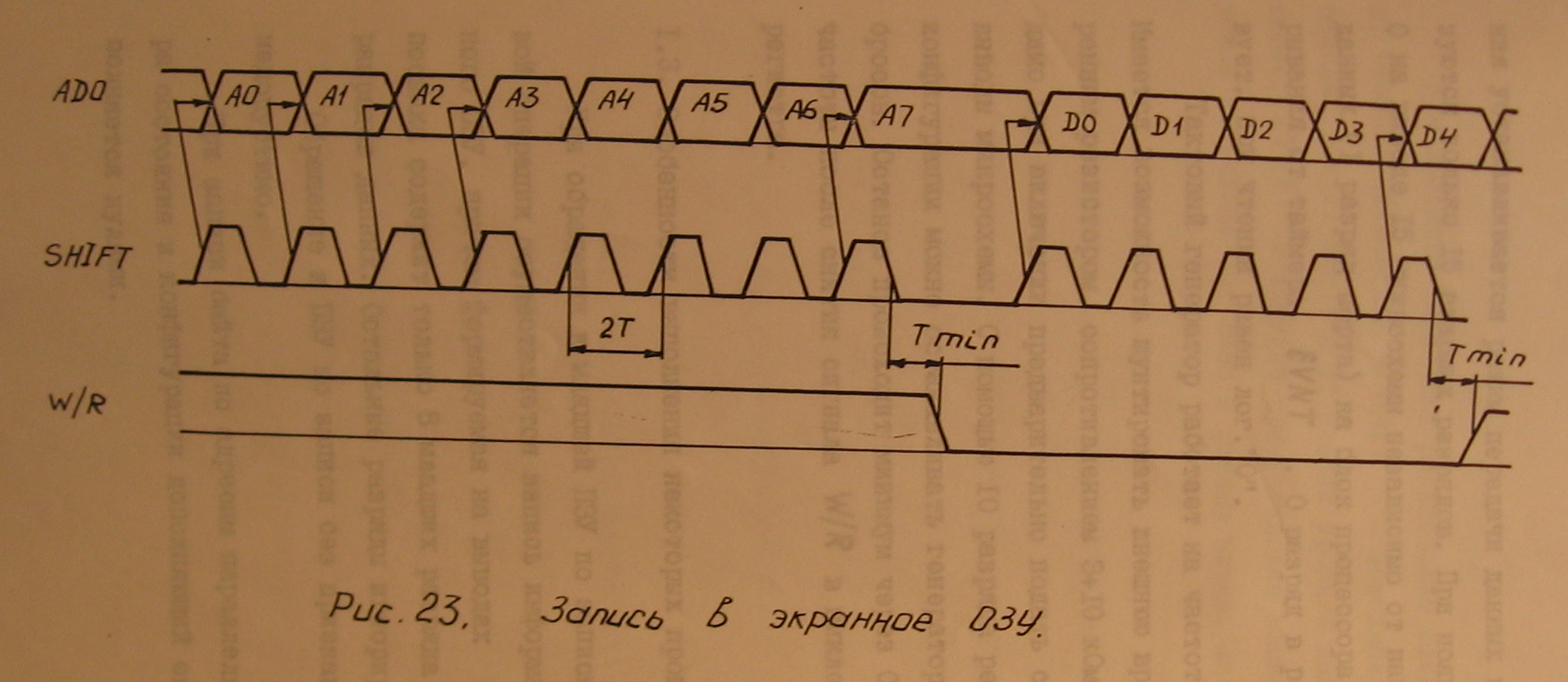

9-й короткий импульс, как и в версии процессора с 5-ю битами, - присутствует.

при отладке кода подозревал его наличие.

иначе бы не приходилось выключать SPI после получения второго байта и заново не включать по событию SYNC RISING

Code: Select all

ISR(SPI_STC_vect) {

if (mode_byte == 0) {

address = ~SPDR - 0x80;

mode_byte = 1;

}

else {

data = ~SPDR;

SPCR &= ~(1<<SPE); // выключить SPI

mode_byte = 0;

}

}

ISR(INT1_vect) {

SPCR |= (1<<SPE); // включить SPI

if (address <= 0x68 /*0xE8 - 0x80*/) {LCD_MK85[address] = data; print_screen = 1;}

}

piotr433 wrote:Я ещё подумал, что может такая упрощена схема бы заработала:

эта схема будет работать, но немного не так, как нужно.

нужно, что бы пины Q0-Q7 регистра выдавали содержимое регистра в момент изменения логического состояния SYNC и хранили до следующего изменения SYNC.

для этого нужно перевести пин STB регистра в состояние "1", затем в "0" до того как изменится CLK сигналом SHIFT.(пример, конвертации события SYNC RISING в управляющий сигнал для STB в моей схеме - можно посмотреть в приложенной к посту картинко)

предложенная вами схема будет так работать только при изменении SYNC с "1" в "0".

при изменении SYNC с "0" в "1" у нас может остаться ровно один такт времени до изменения SHIFT, что бы успеть считать актуальные на момент изменения SYNC данные, иначе они будут изменены приёмом битов очередной пары байтов.

что сводит на нет желание получить достаточное время для обработки данных контроллером AVR равное времени приёма регистром 16-ти бит или 8-ми бит, в случае использования одного регистра.

в случае использования одного регистра, нужна аналогичная ниже(для двух регистров) схема конвертации изменения SYNC по событию SYNC RISING в управляющий сигнал для STB , но по событию SYNC CHANGE.

You do not have the required permissions to view the files attached to this post.