Принципиальная схема исполнителя шины PCI

Moderator: Shaos

-

ls-al

- Junior

- Posts: 1

- Joined: 22 Nov 2014 05:43

- Location: 217.118.93.137

Принципиальная схема исполнителя шины PCI

Доброго времени суток.

Возник интерес в более подробном изучении шины PCI. К имеющемуся описанию данной шины в Гуке и в книгах прочих авторов, захотелось найти хотя бы какую-то функционально-принципиальную схему данной шины.

Нашёл либо только структурную: http://www.konsalter.ru/biblioteka/i1/6_2.htm

Либо с использованием ПЛИС: http://www.platan.ru/shem/pdf/pci.pdf

и http://elm-chan.org/works/pci/report_e.html

Если кто-то знает, где можно схемку найти - я буду огромно благодарен.

Спасибо.

Возник интерес в более подробном изучении шины PCI. К имеющемуся описанию данной шины в Гуке и в книгах прочих авторов, захотелось найти хотя бы какую-то функционально-принципиальную схему данной шины.

Нашёл либо только структурную: http://www.konsalter.ru/biblioteka/i1/6_2.htm

Либо с использованием ПЛИС: http://www.platan.ru/shem/pdf/pci.pdf

и http://elm-chan.org/works/pci/report_e.html

Если кто-то знает, где можно схемку найти - я буду огромно благодарен.

Спасибо.

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Проблема в том, что шина в принципе создавалась как межмикросхемная, ориентированнаяls-al wrote:Доброго времени суток.

Возник интерес в более подробном изучении шины PCI. К имеющемуся описанию данной шины в Гуке и в книгах прочих авторов, захотелось найти хотя бы какую-то функционально-принципиальную схему данной шины.

Нашёл либо только структурную: http://www.konsalter.ru/biblioteka/i1/6_2.htm

Либо с использованием ПЛИС: http://www.platan.ru/shem/pdf/pci.pdf

и http://elm-chan.org/works/pci/report_e.html

Если кто-то знает, где можно схемку найти - я буду огромно благодарен.

Спасибо.

на реализацию как ведущего, так и ведомых устройств в виде одной ИМС (ПЛИС или заказная).

Реализация простенького ведомого на мелкой логике в принципе возможна, но очень проблематична.

дело даже не в высокой тактовой (33 МГц многие серии потянут), а в реализации конфигурационных

регистров, обязательных для корректной работы в PCI-системе.

Даже минимальный набор весьма громоздкий и корректная реализация, например, LPT-SPP порта

на PCI может вылиться в десятки корпусов 1554 или 74АС. Естественно, связываться с этим

любителям не хочется и таких схем, скорее всего, просто нет в природе.

-

JeNNeR

- Fanat

- Posts: 52

- Joined: 18 Nov 2014 09:17

- Location: Отсюда

Re: Принципиальная схема исполнителя шины PCI

В принципе, там же, где вы плис нашли, там и схема лежит...

http://elm-chan.org/works/pci/pci_io.png

http://elm-chan.org/works/pci/pci_io.png

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Всё так, но в этой схеме U3 - хоть и слабая, но всё-таки ПЛИС и адрес задаётся переключателями SW1, SW2,JeNNeR wrote:В принципе, там же, где вы плис нашли, там и схема лежит...

http://elm-chan.org/works/pci/pci_io.png

а должен задаваться регистром базового адреса (см. стандарт PCI) ...

-

Odin P. Morgan

- Senior

- Posts: 151

- Joined: 23 Feb 2015 15:37

- Location: OMS

Re: Принципиальная схема исполнителя шины PCI

А по-моему вполне удачное решение, если ещё можно купить ПЛИСины по 65р./шт (такие когда-то видел), то вполне реализуемо.viv-pm wrote:Всё так, но в этой схеме U3 - хоть и слабая, но всё-таки ПЛИС и адрес задаётся переключателями SW1, SW2,JeNNeR wrote:В принципе, там же, где вы плис нашли, там и схема лежит...

http://elm-chan.org/works/pci/pci_io.png

а должен задаваться регистром базового адреса (см. стандарт PCI) ...

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Вопрос ставился, можно ли без ПЛИС? Ответ - можно, но очень трудно.Odin P. Morgan wrote:А по-моему вполне удачное решение, если ещё можно купить ПЛИСины по 65р./шт (такие когда-то видел), то вполне реализуемо.viv-pm wrote:Всё так, но в этой схеме U3 - хоть и слабая, но всё-таки ПЛИС и адрес задаётся переключателями SW1, SW2,JeNNeR wrote:В принципе, там же, где вы плис нашли, там и схема лежит...

http://elm-chan.org/works/pci/pci_io.png

а должен задаваться регистром базового адреса (см. стандарт PCI) ...

Вопрос второй - корректно ли реализованы обе схемы на ПЛИС? Ответ - не корректно,

нет обязательных, предусмотренных стандартом вещей. В PCI-системе они не сконфигурируются.

Мало того, что к этим устройствам нормально не обратиться, они ещё могут нарушить работу

других устройств.

-

Odin P. Morgan

- Senior

- Posts: 151

- Joined: 23 Feb 2015 15:37

- Location: OMS

Re: Принципиальная схема исполнителя шины PCI

Да, тут не поспоришь. Однако же можно-же что-нить придумать.

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Тут придумывать не надо, тут просто надо разрабатывать.Odin P. Morgan wrote:Да, тут не поспоришь. Однако же можно-же что-нить придумать.

Обязательными в PCI являются 5 полей в общей сложности в 4 конфигурациоонных

регистрах, плюс в регистре команд необходимо, как минимум, реализовать флаг

доступа к памяти, и для доступа даже к одному регистру данных - регистр

базового адреса. В общем, на слепыше не спаяешь - надо делать

полноценную печатную плату.

-

Stan

- Banned

- Posts: 397

- Joined: 04 Jan 2013 10:09

- Location: 95.24.178.158

Re: Принципиальная схема исполнителя шины PCI

А как же: http://elm-chan.org/works/pci/report_e.html ?viv-pm wrote:В общем, на слепыше не спаяешь - надо делать

полноценную печатную плату.

viv-pm wrote:...тут просто надо разрабатывать.

Обязательными в PCI являются 5 полей в общей сложности в 4 конфигурациоонных

регистрах, плюс в регистре команд необходимо, как минимум, реализовать флаг

доступа к памяти, и для доступа даже к одному регистру данных - регистр

базового адреса.

Если Вы разобрались подробно, написали бы алгоритм по тактам, что и когда и откуда считывают и куда записывают?

Ну и попробовали бы мы сделать аппаратную прикидку этого алгоритма на быстрой логике.

А то тема с PCI-платой всплывает не в первый раз, и меня тоже интересовала вот в этом топике:

viewtopic.php?f=68&t=10720

Но всякий раз это заканчивается безрезультатно...

-

Odin P. Morgan

- Senior

- Posts: 151

- Joined: 23 Feb 2015 15:37

- Location: OMS

Re: Принципиальная схема исполнителя шины PCI

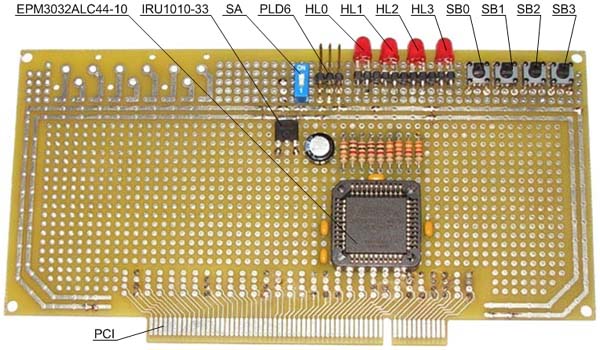

Вид такого "слепыша" немного пугает: чем он проводки экранировал?

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Тут дело не в алгоритме, он очень простой, просто действительно нужно много регистров.Stan wrote: Если Вы разобрались подробно, написали бы алгоритм по тактам, что и когда и откуда считывают и куда записывают?

Ну и попробовали бы мы сделать аппаратную прикидку этого алгоритма на быстрой логике.

А то тема с PCI-платой всплывает не в первый раз, и меня тоже интересовала вот в этом топике:

viewtopic.php?f=68&t=10720

Но всякий раз это заканчивается безрезультатно...

Если немного освобожусь, нарисую подробную функциональную схему простейшего устройства

параллельного ввода/вывода для PCI.

-

Lavr

- Supreme God

- Posts: 16689

- Joined: 21 Oct 2009 08:08

- Location: Россия

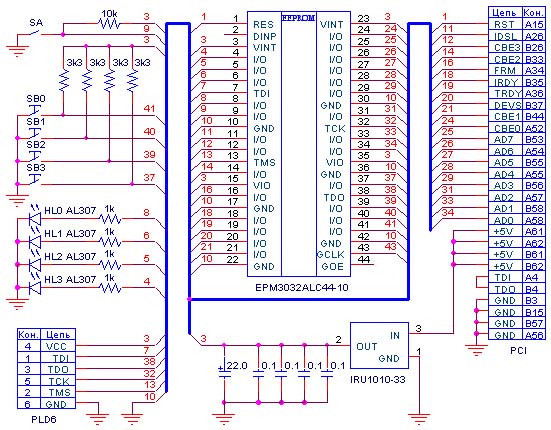

Карта PCI - microcart

Интересно, что-нибуть сдвинулось с этим устройством?viv-pm wrote:Если немного освобожусь, нарисую подробную функциональную схему простейшего устройстваStan wrote:тема с PCI-платой всплывает не в первый раз, и меня тоже интересовала вот в этом топике:

viewtopic.php?f=68&t=10720

Но всякий раз это заканчивается безрезультатно...

параллельного ввода/вывода для PCI.

А то я тоже интересовался схемотехникой PCI-плат, но так и не осилил пока это дело.

Но сегодня весьма неожиданно из статьи Программирование драйверов устройств нашел

ссылку на PCI-устройство на одной ПЛИС: Карта PCI - microcart П. Уварова

Где г-н П. Уваров позиционирует своё PCI-устройство на одной ПЛИС так:

...если вам требуется разработать оригинальное PCI-устройство с не очень большой производительностью (кстати, в разы превышающей производительность шины ISA) не спешите хвататься за такие "редкоземельные" и дорогостояшие агрегаты, как PLX или MCCA. Возьмите дешовую ПЛИС в 128/256 макроячеек и сделайте свое устройство по подобию "microcart".

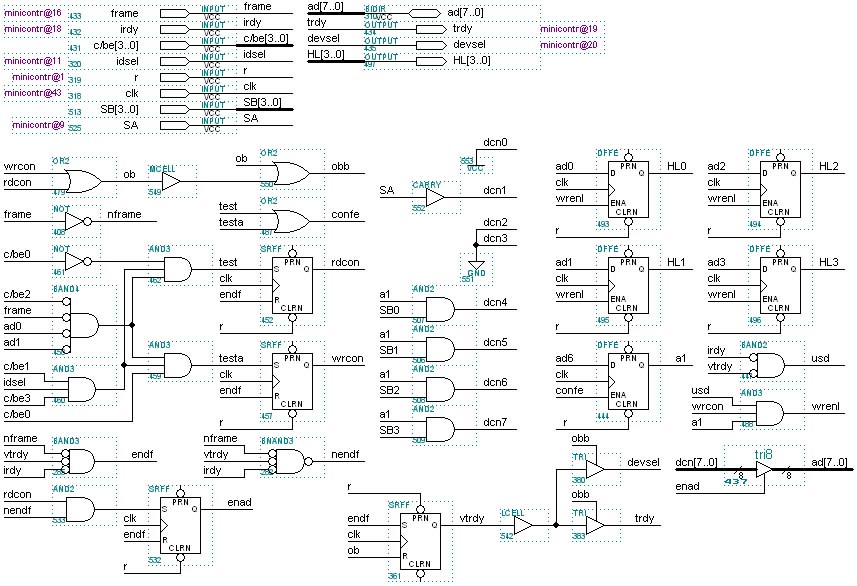

И я вот призадумался, если есть в статье схема того, что реализовано в ПЛИС :

То, может быть, есть возможность повторить это устройство на шустрой дискретной логике?

iLavr

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Проблема в том, что даже функциональная схема

СООТВЕТСТВУЮЩЕГО СТАНДАРТУ устройства PCI

получается непростой (это ещё не всё)...

СООТВЕТСТВУЮЩЕГО СТАНДАРТУ устройства PCI

получается непростой (это ещё не всё)...

You do not have the required permissions to view the files attached to this post.

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Описание узлов функциональной схемы:

РгВх - входной регистр адреса/данных;

РгВых - выходной регистр данных

(с разрешением выхода, как КФ1554ИР23);

Рг - регистр разнородных управляющих сигналов;

РгУВх - входной регистр управляющих сигналов;

РгУВых - выходной регистр управляющих сигналов

(с разрешением выхода);

Км - коммутатор выходных данных;

ДшКд - дешифратор команды на шине PCI

(чтение/запись памяти или конфигурационных регистров);

ДшФ - дешифратор фазы обмена на шине PCI:

ФС - фаза останова /FRAME1 = 1 /IRDY1 = 1,

ФА - фаза адреса /FRAME1 = 0 /IRDY1 = 1,

ФД - фаза данных /IRDY1 = 0;

РгА - регистр адреса

(с разрешением записи, как КФ1533ИР27);

ДшРг - дешифратор конфигурационных регистров

(Идентификаторов, КоманД, КЛасса, Базового Адреса);

РгБА - регистр базового адреса

(с разрешением записи);

== - узел сравнения текущего и базового адреса;

РгКд - регистр команд (одноразрядный, единственная

команда - разрешение обращения к памяти);

РгДВых - выходной регистр данных вывода

(с разрешением записи);

РгДВх - входной регистр данных ввода.

РгДВых и РгДВх - единственное, что доступно для записи и

чтения в 64-килобайтном пространстве памяти устройства.

РгВх - входной регистр адреса/данных;

РгВых - выходной регистр данных

(с разрешением выхода, как КФ1554ИР23);

Рг - регистр разнородных управляющих сигналов;

РгУВх - входной регистр управляющих сигналов;

РгУВых - выходной регистр управляющих сигналов

(с разрешением выхода);

Км - коммутатор выходных данных;

ДшКд - дешифратор команды на шине PCI

(чтение/запись памяти или конфигурационных регистров);

ДшФ - дешифратор фазы обмена на шине PCI:

ФС - фаза останова /FRAME1 = 1 /IRDY1 = 1,

ФА - фаза адреса /FRAME1 = 0 /IRDY1 = 1,

ФД - фаза данных /IRDY1 = 0;

РгА - регистр адреса

(с разрешением записи, как КФ1533ИР27);

ДшРг - дешифратор конфигурационных регистров

(Идентификаторов, КоманД, КЛасса, Базового Адреса);

РгБА - регистр базового адреса

(с разрешением записи);

== - узел сравнения текущего и базового адреса;

РгКд - регистр команд (одноразрядный, единственная

команда - разрешение обращения к памяти);

РгДВых - выходной регистр данных вывода

(с разрешением записи);

РгДВх - входной регистр данных ввода.

РгДВых и РгДВх - единственное, что доступно для записи и

чтения в 64-килобайтном пространстве памяти устройства.

You do not have the required permissions to view the files attached to this post.

-

viv-pm

- Novelist

- Posts: 31

- Joined: 17 Mar 2015 21:54

Re: Принципиальная схема исполнителя шины PCI

Описание сигналов на функциональной схеме:

AD31..AD0, /CBE3../CBE0, /FRAME, /IRDY, IDSEL,

/DEVSEL, /TRDY, /STOP, CLK, /RST - сигналы шины PCI;

C - общий сигнал синхронизации, все регистры в устройстве

тактируются нарастающим фронтом этого сигнала;

/RES - общий сигнал сброса (необходим лишь для некоторых

регистров устройства);

/FRAME1, /IRDY1, IDSEL1 - задержанные на 1 такт сигналы шины PCI;

ФС, ФА, ФД - сигналы соответственно фазы останова, адреса, данных;

ФС1, ФА1, ФД1 - тоже самое, но задержанные на такт;

РгИ, РгКд, РгКл, РгБА, РгВВ - сигналы обращения

соответственно к регистрам идентификаторов,

команд, класса, базового адреса, ввода/вывода;

ЧтП, ЗпП, ЧтКф, ЗпКф - на шине PCI дешифрирована команда

чтения памяти, записи в память

чтения конфигурационного регистра,

записи в конфигурационный регистр;

ВыбКф - выборка конфигурационных регистров;

ВыбА - выборка адресуемой памяти;

ОБР - сигнал обращения к устройству по шине PCI;

Бт0 - выборка нулевого байта в двойном слове (т.е. AD7..AD0);

РП - разрешеие доступа к пространству памяти устройства;

ЗпК - строб записи в конфигурационый регистр;

ЗпД - строб записи в регистр данных;

Чт - строб чтения.

AD31..AD0, /CBE3../CBE0, /FRAME, /IRDY, IDSEL,

/DEVSEL, /TRDY, /STOP, CLK, /RST - сигналы шины PCI;

C - общий сигнал синхронизации, все регистры в устройстве

тактируются нарастающим фронтом этого сигнала;

/RES - общий сигнал сброса (необходим лишь для некоторых

регистров устройства);

/FRAME1, /IRDY1, IDSEL1 - задержанные на 1 такт сигналы шины PCI;

ФС, ФА, ФД - сигналы соответственно фазы останова, адреса, данных;

ФС1, ФА1, ФД1 - тоже самое, но задержанные на такт;

РгИ, РгКд, РгКл, РгБА, РгВВ - сигналы обращения

соответственно к регистрам идентификаторов,

команд, класса, базового адреса, ввода/вывода;

ЧтП, ЗпП, ЧтКф, ЗпКф - на шине PCI дешифрирована команда

чтения памяти, записи в память

чтения конфигурационного регистра,

записи в конфигурационный регистр;

ВыбКф - выборка конфигурационных регистров;

ВыбА - выборка адресуемой памяти;

ОБР - сигнал обращения к устройству по шине PCI;

Бт0 - выборка нулевого байта в двойном слове (т.е. AD7..AD0);

РП - разрешеие доступа к пространству памяти устройства;

ЗпК - строб записи в конфигурационый регистр;

ЗпД - строб записи в регистр данных;

Чт - строб чтения.