Порты для 0-3 логических сегментов Z80

Moderator: Shaos

-

Vasil Ivanov

- Doomed

- Posts: 413

- Joined: 11 Dec 2003 14:34

Порты для 0-3 логических сегментов Z80

Привет!

Прошу помощи у всезнающего ALL-а!

Все адресное пространство Z80 (64 кило) делится на 4 сегмента (0-3) по 16 кило каждый. Каким образом (схемно) делаются порты каждый на свой 16kB сегмент ?. Т.е. каждый из 4-х портов включает указанную

(любую из 0-255, при 4 метрах ОЗУ) страницу только в свой сегмент.

Чо то не могу докумекать как это делается.

Прошу помощи у всезнающего ALL-а!

Все адресное пространство Z80 (64 кило) делится на 4 сегмента (0-3) по 16 кило каждый. Каким образом (схемно) делаются порты каждый на свой 16kB сегмент ?. Т.е. каждый из 4-х портов включает указанную

(любую из 0-255, при 4 метрах ОЗУ) страницу только в свой сегмент.

Чо то не могу докумекать как это делается.

Vasil Ivanov

vasil-i@yandex.ru

vasil-i@yandex.ru

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Порты для 0-3 логических сегментов Z80

Тебе надо четыре регистра 8-разрядных поставить с Z состоянием - чтобы проц мог туда писать (как минимум), выходы с них соединяешь вместе и ведёшь на A14-A21 твоей памяти. От проца A14 и A15 ведёшь к демультиплексору 2:4, выходы которого цепляешь к OE каждого из регистров. Адреса A0-A13, шину данных, RD и WR от проца ведёшь прямиком на память. ВсёVasil Ivanov wrote:Привет!

Прошу помощи у всезнающего ALL-а!

Все адресное пространство Z80 (64 кило) делится на 4 сегмента (0-3) по 16 кило каждый. Каким образом (схемно) делаются порты каждый на свой 16kB сегмент ?. Т.е. каждый из 4-х портов включает указанную

(любую из 0-255, при 4 метрах ОЗУ) страницу только в свой сегмент.

Чо то не могу докумекать как это делается.

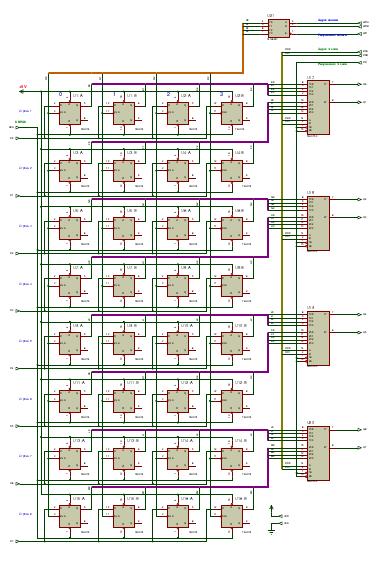

P.S. Во - нашёл свою зарисовку 4-летней давности! Тут к вышеописанному добавился ещё демультиплексор на порты доступа к регистрам и логика записи в них по WR - это можно по всякому делать:

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Vasil Ivanov

- Doomed

- Posts: 413

- Joined: 11 Dec 2003 14:34

Re: Порты для 0-3 логических сегментов Z80

Спасибо за хелп!. Буду схемно проверять (в протеусе) твою зарисовку.Shaos wrote:Тебе надо четыре регистра 8-разрядных поставить с Z состоянием - чтобы проц мог туда писать (как минимум), выходы с них соединяешь вместе и ведёшь на A14-A21 твоей памяти. От проца A14 и A15 ведёшь к демультиплексору 2:4, выходы которого цепляешь к OE каждого из регистров. Адреса A0-A13, шину данных, RD и WR от проца ведёшь прямиком на память. ВсёVasil Ivanov wrote:Привет!

Прошу помощи у всезнающего ALL-а!

Все адресное пространство Z80 (64 кило) делится на 4 сегмента (0-3) по 16 кило каждый. Каким образом (схемно) делаются порты каждый на свой 16kB сегмент ?. Т.е. каждый из 4-х портов включает указанную

(любую из 0-255, при 4 метрах ОЗУ) страницу только в свой сегмент.

Чо то не могу докумекать как это делается.

P.S. Во - нашёл свою зарисовку 4-летней давности! Тут к вышеописанному добавился ещё демультиплексор на порты доступа к регистрам и логика записи в них по WR - это можно по всякому делать:

Vasil Ivanov

vasil-i@yandex.ru

vasil-i@yandex.ru

-

b2m

- Devil

- Posts: 907

- Joined: 26 May 2003 06:57

А не проще поставить пару ИР26 (74HC670)?

Страничка эмулятора наших компьютеров

http://bashkiria-2m.narod.ru/

http://bashkiria-2m.narod.ru/

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Может и проще - но они труднодоставаемые, а значит - дорогие. В данный момент доступны только в соиках (HC и HCT) по цене за полтора доллара штучка (хорошо, что я раньше прикупил себе 4 штучки 74LS670 в DIP-корпусе для экспериментов).b2m wrote:А не проще поставить пару ИР26 (74HC670)?

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

HardWareMan

- Banned

- Posts: 2139

- Joined: 20 Mar 2005 13:41

- Location: От туда

Если будешь пихать схему в CPLD, то забудь о Z, и сделай переключение на мультиплексоре. Остальное все так. Ну я про основную идею. От себя добавлю, что сбрасываемый регистр (особенно в 0 странице) желателен, чтобы по сбросу был всегда установлен рабочий код (если 4МБ адресное пространство у тебя общее для RAM и ROM.

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Да - согласен - регистры надо инициировать, например при включении чтобы управление передавалось в ROM, который по умолчанию втыкается в нулевую страницу, а тот уже инитит регистры соответствующим образом.HardWareMan wrote:Если будешь пихать схему в CPLD, то забудь о Z, и сделай переключение на мультиплексоре. Остальное все так. Ну я про основную идею. От себя добавлю, что сбрасываемый регистр (особенно в 0 странице) желателен, чтобы по сбросу был всегда установлен рабочий код (если 4МБ адресное пространство у тебя общее для RAM и ROM.

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

Vasil Ivanov

- Doomed

- Posts: 413

- Joined: 11 Dec 2003 14:34

Пока остановился на таком варианте.Shaos wrote:Да - согласен - регистры надо инициировать, например при включении чтобы управление передавалось в ROM, который по умолчанию втыкается в нулевую страницу, а тот уже инитит регистры соответствующим образом.HardWareMan wrote:Если будешь пихать схему в CPLD, то забудь о Z, и сделай переключение на мультиплексоре. Остальное все так. Ну я про основную идею. От себя добавлю, что сбрасываемый регистр (особенно в 0 странице) желателен, чтобы по сбросу был всегда установлен рабочий код (если 4МБ адресное пространство у тебя общее для RAM и ROM.

Code: Select all

+---+----+----+

---|D0 | | Q0|---

---|D1 | | Q1|---

---|D2 | | Q2|---

---|D3 | | Q3|---

---|D4 | | Q4|---

---|D5 | | Q5|---

---|D6 | | Q6|---

---|D7 | | Q7|---

+---| | |

---|WRA| | |

---|WRB| | |

--o|WR | | |

+---| | |

---|RDA| | |

---|RDB| | |

--o|RD | | |

+---| | |

--o|RES| | |

+---+----+----+

В четыре 8-ми разрядных регистра можно раздельно записывать/читать любую информацию.

D0..D7 - входы

Q0..Q7 - выходы

При WR 1->0 происходит защелкивание данных со входов D0..D7.

WRA-WRB - выбор регистров для записи.

При RD=1 на всех выходах Q уст."0".

При RD=0 происходит выдача информации на выходы Q, согласно адресу на RDA-RDB.

RDA-RDB - выбор регистров для чтения.

RES - сброс записанных данных м/с в ноль.

Шурик схему брошу тебе на мыло (shaos@mail.ru), вставь ее (или сцилку) в эту мессагу. Там дешифратор 74139my отличается

от стандартного 74139 только тем, что у моего варианта выходы не инверсные. Все равно эта схема для

плисины, так что лучше перерисовать дешифратор 2:4, чем добавлять лишние инверторы.

Vasil Ivanov

vasil-i@yandex.ru

vasil-i@yandex.ru

-

Vasil Ivanov

- Doomed

- Posts: 413

- Joined: 11 Dec 2003 14:34

Спасибо, учту. Что касается схемной реализации, то имеется матрица на D-триггерах, 4 колонки на 8 строк. 74139 выбирает колонки, 74153 выбирают строки.HardWareMan wrote:Если будешь пихать схему в CPLD, то забудь о Z, и сделай переключение на мультиплексоре.

Ты прав. Я такую фитчу встречал еще у Орион-128, когда читал описание работы его схемы. Как раз для этого у меня есть пин RES,От себя добавлю, что сбрасываемый регистр (особенно в 0 странице) желателен, чтобы по сбросу был всегда установлен рабочий код (если 4МБ адресное пространство у тебя общее для RAM и ROM.

сбрасывающий все записанные данные.

Vasil Ivanov

vasil-i@yandex.ru

vasil-i@yandex.ru

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Вставляю (кликнув на картинку можно стянуть PDF размером 171K):Vasil Ivanov wrote: Шурик схему брошу тебе на мыло (shaos@mail.ru), вставь ее (или сцилку) в эту мессагу. Там дешифратор 74139my отличается

от стандартного 74139 только тем, что у моего варианта выходы не инверсные. Все равно эта схема для

плисины, так что лучше перерисовать дешифратор 2:4, чем добавлять лишние инверторы.

А вот сцылка на зазипованный PDF:

http://nedopc.org/nedopc/upload/4x8.zip (27K)

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

masterspammer

- Fanat

- Posts: 95

- Joined: 13 Dec 2020 21:11

Re:

Спасибо за наводку! Внезапно нашёл кучу в соседнем магазине (видать никому кроме меня не были нужны). В DIPе, купил 6 штук.b2m wrote:А не проще поставить пару ИР26 (74HC670)?

Кстати, на этих регистрах можно ещё и палитру для видеовывода сделать, например, 4 из 16 возможных цветов, 8 из 16 или 4 из 256 - на двух, ну и,

раз пошла такая пьянка, 8 из 256 на 4-х.

Рядом всё равно городить ещё регистр/буфер, чтоб пропускать адрес насквозь при обращении к портам (страницы у адреса портов это не плохо, но вот со страницами памяти совпадать им уж точно незачем), можно его использовать для первичного включения (если !IORQ или ещё со времён сброса установлен триггер, сбрасываемый любым переключением страниц).Shaos wrote: Да - согласен - регистры надо инициировать, например при включении чтобы управление передавалось в ROM, который по умолчанию втыкается в нулевую страницу, а тот уже инитит регистры соответствующим образом.

-

oldlazycat

- Fanat

- Posts: 59

- Joined: 18 Nov 2022 06:33

- Location: Урюпинск

Re: Порты для 0-3 логических сегментов Z80

А не проще взять Z180? Там уже всё реализовано, правда, на 3 сегмента.

Two Beer? Or not Two Beer?

-

Shaos

- Admin

- Posts: 24011

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Порты для 0-3 логических сегментов Z80

Ну Z180 это старьё-старое, а Z80 вроде как до сих пор штампуетсяoldlazycat wrote:А не проще взять Z180? Там уже всё реализовано, правда, на 3 сегмента.

А вообще в Z180 очень странный MMU - где-то тут на форуме обсуждалось... нашёл:

http://www.nedopc.org/forum/viewtopic.php?p=104326#p104326

т.е. фактически у Z180 перемещаемое окно одно - среднее, а первой и последнее это всегда начало и конец адресного пространства, так-что спасибо ненадо...Задействовать дополнительне разряды адреса от Z180 (A17,A18,A19) скорее всего не получится, т.к. бортовой MMU делит доступную память на 3 части, причём первая часть - это всегда начало памяти, а последняя - это всегда конец, т.е. перемещаться по большой памяти может только среднее окно, а нам надо 4 независимых области по 16K...

Я тут за главного - если что шлите мыло на me собака shaos точка net

-

oldlazycat

- Fanat

- Posts: 59

- Joined: 18 Nov 2022 06:33

- Location: Урюпинск

Re: Порты для 0-3 логических сегментов Z80

Ничего подобного! Открываются 3 окна в пределах 64 КБ из любой части адресуемого 1 МБ с шагом 4 КБ.Shaos wrote:Ну Z180 это старьё-старое, а Z80 вроде как до сих пор штампуетсяoldlazycat wrote:А не проще взять Z180? Там уже всё реализовано, правда, на 3 сегмента.

А вообще в Z180 очень странный MMU - где-то тут на форуме обсуждалось... нашёл:

http://www.nedopc.org/forum/viewtopic.php?p=104326#p104326т.е. фактически у Z180 перемещаемое окно одно - среднее, а первой и последнее это всегда начало и конец адресного пространства, так-что спасибо ненадо...Задействовать дополнительне разряды адреса от Z180 (A17,A18,A19) скорее всего не получится, т.к. бортовой MMU делит доступную память на 3 части, причём первая часть - это всегда начало памяти, а последняя - это всегда конец, т.е. перемещаться по большой памяти может только среднее окно, а нам надо 4 независимых области по 16K...

Two Beer? Or not Two Beer?