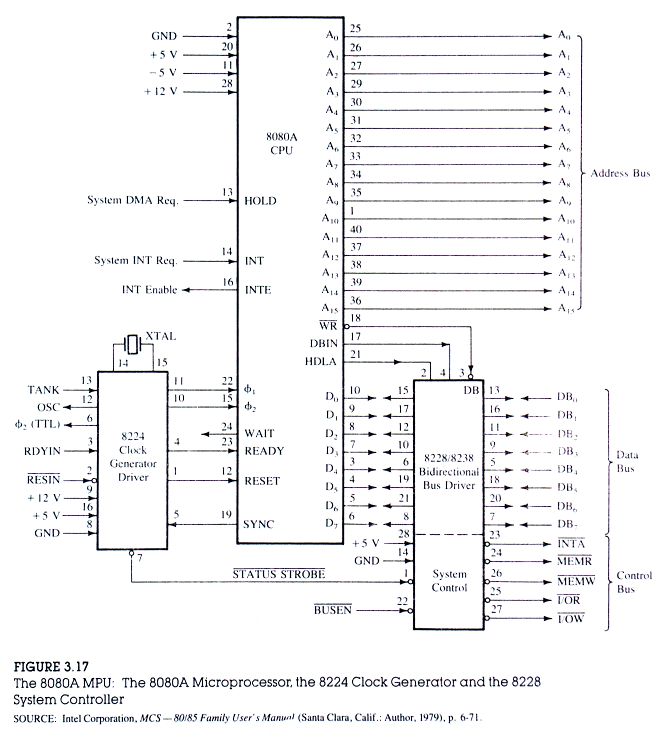

Вот минимальная обвязка из мануала:begoon wrote:О! Мысль!begoon wrote:Я б даже собрал минимальную обвязку для запуска i8080 и изоляции без всего лишнего для проверки этого факта, но увы - мне нужна схема, хотя бы базовая. Сам я ее не нарисую.Lavr wrote:Пробегала информация, то КР580ВМ80А способен работать в режиме:

Uss = 0V, Uсс1 = 5V, Uсс2 = 5V - вот мне и интересна достоверность такого факта.

А давайте замутим девайс для тестирования i8080? Минимальная "обвязка" для запуска проца, плюс пичок, например, для организации консоли (RS232 или USB) в PC. Типа как программа тестирования софтверного эмулятора, только с реальным процом. Дисплей, порты - не нужны, а RAM/ROM можно эмулировать на PIC32.

Буду раз собрать, если кто разработает основу.

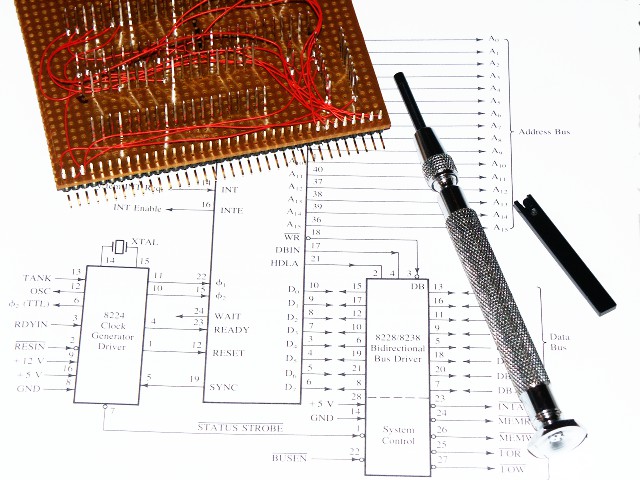

Я даже было начал по этой схеме собирать платку накруткой больше года назад, но затормозил из-за нехватки времени...

P.S. Только RAM/ROM всё же надо настоящие поставить...