А может, и совпало чудесным образом. Была бы возможность 256 перебирать - не отказались бы IMHO.pfgx wrote: Или просто так совпало?

Z80 Finite State Machine

Moderator: Shaos

-

Mixa64

- Doomed

- Posts: 510

- Joined: 25 Aug 2009 07:02

- Location: Москва

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Срисовал транзисторы блока АЛУ, получилось 4 почти одинаковых блока примерно по 150 транзисторов в каждом. Почти - потому что в блоках (1 блок - 2 бита данных и 1 бит АЛУ) есть некоторые различия, но пока я на них не хочу останавливаться. В дальнем конце АЛУ засунут маленький, но очень запутанный блок, по-моему это для daa, его пока не рисовал.

Есть проблема. Я нарисовал транзисторы, выделил более сложные структуры, даже есть какое-то понимание, но выразить так, чтобы это понял кто-то другой... Я тут порассуждаю вслух, вы не против?

Я тут порассуждаю вслух, вы не против?

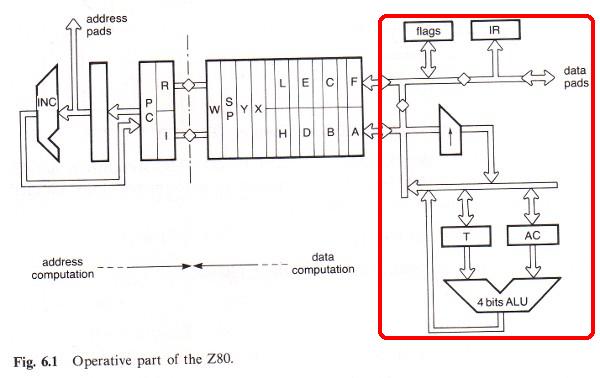

Внутренняя шина данных делится двумя коммутаторами на три части:

1. старший байт регистров, АЛУ

2. младший байт регистров, выходы формирователей флагов и коррекции для daa (00h, 06h, 60h, 66h)

3. instruction register, выводы D0...D7 (выводы как-то путаются, но вроде подключены сюда)

То есть на картинке, которая из книги, "поперечные ромбики" это и есть коммутаторы (по 8 транзисторов каждый). Ещё при рисовании регистров вывихнул мозг по поводу инверсии, и по-моему на внутренней ШД данные в инвертированном виде.

АЛУ я называю то, что явно выделяется на фотографии. Оно включает в себя:

0. Собственную 8-разрядную локальную шину данных (далее - ЛШД). Её наверное и имеют в виду авторы, говоря про 4 части ШД и 3 коммутатора.

1а. Коммутатор (тот самый третий?), который может соединить ЛШД с частью ШД процессора. Но сделать он это может "один к одному" или со сдвигом на один разряд. 0-й и 7-й разряды при сдвигах берутся не с шины, а с логики, видимо для реализации сдвига через флаг переноса.

1б. Push-pull драйвер для выдачи данных с ЛШД на общую ШД.

2. Схему (всё ещё 8-разрядную), которая может на свой выход подать бит с ЛШД (с инверсией или без), со своего входа подать бит на ЛШД (только с инверсией), она же содержит защёлку (8 разрядов).

3. Выходы этих схем попарно проходят через коммутаторы и получается 4 разряда (2 полубайта), которые подаются на

4. собственно АЛУ, 4-разрядное.

5. Ещё одна схема, назначение которой мне не совсем понятно.

6. Маленький, но сложный кусочек, возможно для десятичной коррекции.

При этом там внутри очень хитро перекрещиваются полубайты, понять как именно не могу, у меня от этого в голове тоже что-то перекрещивается на АЛУ заведены и выходы-входы схемы (см.п.2), и ЛШД, а на непонятный блок (п.6) ещё и 4, 5 и 6 разряды ШД процессора. Далее, видимо, уже надо просто срисовывать, не пытаясь понять назначение всей этой паутины.

на АЛУ заведены и выходы-входы схемы (см.п.2), и ЛШД, а на непонятный блок (п.6) ещё и 4, 5 и 6 разряды ШД процессора. Далее, видимо, уже надо просто срисовывать, не пытаясь понять назначение всей этой паутины.

У меня пока всё. Потом (точно не сегодня) попробую выразить это графически, блок схемой.

Есть проблема. Я нарисовал транзисторы, выделил более сложные структуры, даже есть какое-то понимание, но выразить так, чтобы это понял кто-то другой...

Внутренняя шина данных делится двумя коммутаторами на три части:

1. старший байт регистров, АЛУ

2. младший байт регистров, выходы формирователей флагов и коррекции для daa (00h, 06h, 60h, 66h)

3. instruction register, выводы D0...D7 (выводы как-то путаются, но вроде подключены сюда)

То есть на картинке, которая из книги, "поперечные ромбики" это и есть коммутаторы (по 8 транзисторов каждый). Ещё при рисовании регистров вывихнул мозг по поводу инверсии, и по-моему на внутренней ШД данные в инвертированном виде.

АЛУ я называю то, что явно выделяется на фотографии. Оно включает в себя:

0. Собственную 8-разрядную локальную шину данных (далее - ЛШД). Её наверное и имеют в виду авторы, говоря про 4 части ШД и 3 коммутатора.

1а. Коммутатор (тот самый третий?), который может соединить ЛШД с частью ШД процессора. Но сделать он это может "один к одному" или со сдвигом на один разряд. 0-й и 7-й разряды при сдвигах берутся не с шины, а с логики, видимо для реализации сдвига через флаг переноса.

1б. Push-pull драйвер для выдачи данных с ЛШД на общую ШД.

2. Схему (всё ещё 8-разрядную), которая может на свой выход подать бит с ЛШД (с инверсией или без), со своего входа подать бит на ЛШД (только с инверсией), она же содержит защёлку (8 разрядов).

3. Выходы этих схем попарно проходят через коммутаторы и получается 4 разряда (2 полубайта), которые подаются на

4. собственно АЛУ, 4-разрядное.

5. Ещё одна схема, назначение которой мне не совсем понятно.

6. Маленький, но сложный кусочек, возможно для десятичной коррекции.

При этом там внутри очень хитро перекрещиваются полубайты, понять как именно не могу, у меня от этого в голове тоже что-то перекрещивается

У меня пока всё. Потом (точно не сегодня) попробую выразить это графически, блок схемой.

Last edited by pfgx on 08 Jun 2013 10:51, edited 4 times in total.

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Добавлю здесь ниже картинку, чтобы следить за мыслью автора:pfgx wrote:на картинке, которая из книги, "поперечные ромбики" это и есть коммутаторы...

А явно входы АЛУ не просматриваются?pfgx wrote:Срисовал транзисторы блока АЛУ, получилось 4 почти одинаковых блока

...

даже есть какое-то понимание, но выразить так, чтобы это понял кто-то другой...

По всем патентам и канонам - ко входам АЛУ должны подключаться коммутаторы...

Взглянь ещё на вот эту картинку в обвязке АЛУ - может быть сходные идеи

просматриваются?

Всё же авторы практически одни и те же...

Last edited by Lavr on 08 Jun 2013 10:41, edited 1 time in total.

iLavr

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Наоборот помочь стараюсь!pfgx wrote:Так, не сбивайте с мыслей, я ещё пытаюсь их выразить(см. выше)

А "молоток" со стрелкой вверх ещё ни к каким блокам не "привязывается"?

Это вполне может быть - такое решение нередко, вроде, как обещают,pfgx wrote:и по-моему на внутренней ШД данные в инвертированном виде

помехоустойчивость шины повышается...

iLavr

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Что мог выразил, читайте, спрашивайте

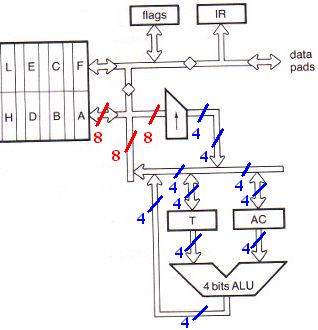

О! Под "молотком" могли иметь в виду третий коммутатор, реализующий сдвиг. Он как раз находится на пути с ШД процессора в ЛШД, далее в защёлки (не 8 бит, а две по 4), АЛУ, а с него на ЛШД и далее на ШД процессора.

Не знаю. Может куда-то и привязывается, но очень уж загадочное у него обозначение.Lavr wrote:А "молоток" со стрелкой вверх ещё ни к каким блокам не "привязывается"?

О! Под "молотком" могли иметь в виду третий коммутатор, реализующий сдвиг. Он как раз находится на пути с ШД процессора в ЛШД, далее в защёлки (не 8 бит, а две по 4), АЛУ, а с него на ЛШД и далее на ШД процессора.

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Вот этот момент и на блок-схеме очень непонятен...pfgx wrote:Под "молотком" могли иметь в виду третий коммутатор, реализующий сдвиг. Он как раз находится на пути с ШД процессора в ЛШД, далее в защёлки (не 8 бит, а две по 4), АЛУ, а с него на ЛШД и далее на ШД процессора.

Через "молоток", кем бы он ни был, 8-битная шина явно выходит 4-битной... А вот как она,

будучи 4-битной, обратно соединяется с 8-битной, без каких-либо явных узлов, - этот

момент просто в тупик ставит!...

iLavr

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Нет, после "молотка", если это коммутатор-сдвигатель, шина 8 бит. "Локальная" шина этого блока тоже 8 бит. А вот T, AC и ALU 4-битные, но оно там сильно перемешано "по кругу" (полубайты ЛШД, вход-выход АЛУ и прочие 4-битности) для последовательной обработки полубайтов.Lavr wrote:Через "молоток", кем бы он ни был, 8-битная шина явно выходит 4-битной... А вот как она, будучи 4-битной, обратно соединяется с 8-битной, без каких-либо явных узлов, - этот момент просто в тупик ставит!...

Но насчёт 4-битности T и AC не уверен, там со всеми этими временными защёлками очень сложно, кое-где в процессоре всё-таки есть элементы динамической логики и "повисший в воздухе" затвор может использоваться для хранения. Из-за этого, кстати, появляются значения флагов F3 и F5 - в схеме формирования флагов для выдачи на ШД на этих разрядах просто нет драйверов, что в ёмкости шины от предыдущей внутренней операции повисло, то в регистр F и записалось.

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Схема из п.5 оказалась почти такой же, как схема из п.2, то есть защёлок всего 16 и временные регистры всё-таки 8-битные.pfgx wrote:АЛУ я называю то, что явно выделяется на фотографии. Оно включает в себя:

...

2. Схему (всё ещё 8-разрядную), которая может на свой выход подать бит с ЛШД (с инверсией или без), со своего входа подать бит на ЛШД (только с инверсией), она же содержит защёлку (8 разрядов).

...

5. Ещё одна схема, назначение которой мне не совсем понятно.

...

1/4 блока АЛУ с временными регистрами

http://yadi.sk/d/HjmP9afY5cxde

- коммутатор 3в1 (К)

- push-pull на шину данных процессора

- регистр с инвертором на выходе (РЕГ, ИНВ)

- коммутатор 2в1 (К)

- собственно АЛУ (АЛУ)

- коммутатор 2в1 (К)

- регистр (РЕГ)

- не знаю что (?)

На вход АЛУ подаются половинки временных регистров (вот где появляется 4-битность). Результат АЛУ пишется в младшую половину первого регистра. Но АЛУ связано и с локальной шиной, зачем - пока не знаю.

Инвертор на выходе первого регистра может инвертировать, а может и не инвертировать данные на выходе (типа как XOR).

На второй регистр заведён clock.

В целом по инверсиям или я где-то ошибся, или там полный бардак. Данные с ШД попадают на ЛШД "как есть" (а они инвертированы), при этом драйвер с ЛШД на ШД с инверсией, то есть на локальной шине внутри блока результат операции в итоге без инверсии. Инверсию триггеров, с учётом того, что у них 1 вход, 1 выход и 1 вход-выход на локальную шину, описать на данный момент не берусь.

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Ну это классика - все так делают дополнение до 2-х для вычитания.pfgx wrote:Инвертор на выходе первого регистра может инвертировать, а может и не инвертировать данные на выходе (типа как XOR).

Ну если они явно работают с 4-бит АЛУ - они явно обязаны быть 4-битными простоpfgx wrote:Но насчёт 4-битности T и AC не уверен, там со всеми этими временными защёлками очень сложно...

без вариантов!

Ладно - я подожду окончательного варианта твоего "эпического подвига"...

Толкать человека под руку, когда он напряженно работает - не в моих правилах...

Доделаешь - тогда и разберемся поточнее...

iLavr

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Во-от. Сам я такое или не знаю, или просто не увижу, а вот такой контроль со стороны это то, чего мне не хватает.Lavr wrote:Ну это классика - все так делают дополнение до 2-х для вычитания.

Регистры - 8-битные, АЛУ - 4-битное. Там ещё коммутаторы есть.Lavr wrote:Ну если они явно работают с 4-бит АЛУ - они явно обязаны быть 4-битными просто без вариантов!

Открываем картинки

http://yadi.sk/d/HjmP9afY5cxde (эта уже была, это как оно выглядит на кристалле)

http://yadi.sk/d/cJtADjGA5dirU (блок-схема)

Таких блоков 4 штуки, они почти одинаковые, отличия в правой части АЛУ видны на изображении кристалла. (Есть ещё одно отличие в схеме precharge, но по-моему это несущественно.) В каждом блоке по 1 разряду из младшей и старшей половины. В качестве примера взял 3-й (счёт с 1), он обрабатывает разряды 2 и 6.

Сначала идёт 2 коммутатора 3в1. Они на внутреннюю шину (в данном случае два разряда Ш2 и Ш6) могут подать байт с ШД процессора "как есть" (D2 и D6), а могут сдвинуть на 1 разряд влево-вправо (D1/D5 или D3/D7). Там же находится отключаемый мощный драйвер для выдачи байта с локальной шины на шину процессора.

Слева и справа 4 блока, левые немного отличаются от правых, но каждый содержит коммутатор входов (взять данные с локальной шины или с альтернативного входа), защёлку, и отключаемый драйвер для выдачи данных на локальную шину. Альтернативный выход (на АЛУ) работает всегда. Регистры управляются только целиком, не половинами.

Альтернативные выходы (2 по 8 разрядов) проходят через коммутаторы 2в1 (получается 2 по 4 разряда) и через драйвер подаются на АЛУ. То есть регистры 8-разрядные, но на АЛУ для обработки подаются либо младшие, либо старшие половины регистров.

Куда точно выводятся результаты АЛУ, зачем ему соединения с локальной шиной и для чего нужны перекрёстные (старший/младший полубайт) подключения альтернативных входов защёлок пока не знаю.

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Я просто просмотрел довольно много схем процессоров, в поисках оригинальныхpfgx wrote:Во-от. Сам я такое или не знаю, или просто не увижу, а вот такой контроль со стороны это то, чего мне не хватает.Lavr wrote:Ну это классика - все так делают дополнение до 2-х для вычитания.

решений для своей конструкции. Так что многое в "районе АЛУ" повторяется у них...

Мне кажется, пора бы делать прикидку на соответствие топологии командам z80...pfgx wrote:Куда точно выводятся результаты АЛУ, зачем ему соединения с локальной шиной и для чего нужны перекрёстные (старший/младший полубайт) подключения альтернативных входов защёлок пока не знаю.

По описанию - напоминает SWAPF от PIC... но у z80 вроде же нет подобной команды...

iLavr

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Эта конструкция где-нибудь описана?Lavr wrote:Я просто просмотрел довольно много схем процессоров, в поисках оригинальных решений для своей конструкции. Так что многое в "районе АЛУ" повторяется у них...

У него есть rrd, она как раз полубайты вращает. Да и просто при вычислениях это может использоваться.Lavr wrote: По описанию - напоминает SWAPF от PIC... но у z80 вроде же нет подобной команды...

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Естественно... и даже на нашем форуме я эти материалы собирал, когда сам конструировал АЛУ.pfgx wrote:Эта конструкция где-нибудь описана?Lavr wrote:Я просто просмотрел довольно много схем процессоров, в поисках оригинальных решений для своей конструкции. Так что многое в "районе АЛУ" повторяется у них...

Другое дело, что в итоге XOR я не применил - поскольку было "спортивное" ограничение,

"всё - максимально на NAND"... хотя фактически там XOR из NAND-ов и сделан - в узле "B"MUX .

iLavr

-

pfgx

- Senior

- Posts: 137

- Joined: 20 Mar 2013 03:36

- Location: Ростов-на-Дону

Да на этом форуме столько всего написано!.. Надо будет потом отдельно заняться только чтением и конспектированиемLavr wrote:[Естественно... и даже на нашем форуме я эти материалы собирал, когда сам конструировал АЛУ.