Мне понравилась публикация!Shaos wrote:хм, я уже 34й с рейтингом 92,4Shaos wrote:Shaos wrote:Через сутки после публикации я 43й хабровчанин с рейтингом 79.4

Статья всё ещё первая за сутки и уже стала третьей за неделю с оценкой +99 - ещё немного и станет второй

Разработка и заказ троичной микросхемы

Moderator: haqreu

-

askfind

- Devil

- Posts: 896

- Joined: 04 Jan 2016 09:15

- Location: Russia, S.- Peterburg

Re: Разработка и заказ троичной микросхемы

"Ученье свет, а неученье — тьма. Дело мастера боится, и коль крестьянин не умеет сохою владеть — хлеб не родится." (С)

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Наверное поэтому я уже 31й с рейтингом 94,8askfind wrote:Мне понравилась публикация!Shaos wrote:хм, я уже 34й с рейтингом 92,4Shaos wrote:Shaos wrote:Через сутки после публикации я 43й хабровчанин с рейтингом 79.4

Статья всё ещё первая за сутки и уже стала третьей за неделю с оценкой +99 - ещё немного и станет второй

P.S. Попробовал залогиниться в мосис, а оно мне говорит фиг - account expired

P.P.S. Обратился в поддержку мосиса - ответили, что восстановить невозможно - надо новый аккаунт создавать и подтвердили, что с On-Semi они больше не работают - 0.5um через них больше будет сделать нельзя.

Значит смотрим в сторону europractice: https://europractice-ic.com/wp-content/uploads/2020/05/General-MPW-EUROPRACTICE-200505-v8.pdf (там и даты, и цены, и On-Semi тоже есть)

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Процесс C5 (который я использовал в первой своей троичной микросхеме 2015 года) если делать через europractice допускает использование только Cadence 5 или 6, но зато есть пара 0.35um mixed-signal процессов (ниже их описание скопированное с https://europractice-ic.com/mpw-prototyping/asics/on-semiconductor/), которые всё ещё можно разрабатывать в Tanner (тоже коммерческий, но сильно дешевле) плюс C5 для сравнения (с подсчитанной минимальной ценой для каждого):

Это за 30 штучек и без упаковки - упаковка отдельно: https://europractice-ic.com/packaging-integration/standard-packaging/ (все цены видны)

P.S. Подробнее про I3T50: https://www.onsemi.com/products/product-taxonomy/custom-foundry-services/i3t50-process-technology - там кроме PMOS и NMOS (обычных и высоковольтных) есть ещё биполярные транзисторы (NPN), диоды, стабилитроны, конденсаторы, резисторы и всякие библиотечные компоненты типа SRAM, ROM и даже OTP и EEPROM

Code: Select all

I3T50 The ON Semiconductor Intelligent Interface Technology I3T50 process is

the answer to the need for increased digital content in a mixed−signal

and/or high voltage environment. It provides the density of a 0.35µm

digital process, analog/mixed−signal capability and high voltage.

Featuring high voltage devices up to 40 V as well as digital and

analog operation at 3.3 V, the I3T50 process family is the first to

use deep trenches for isolating high voltage devices.

850EUR/mm^2 with min 10 mm^2 (min 8500 EUR)

I3T80 Providing the density of a 0.35µm digital process, analog/mixed−signal

capability and high voltage, the ON Semiconductor Intelligent Interface

Technology I3T80 process is the answer to the need for increased digital

content in a mixed−signal and/or high voltage environment. Featuring

high voltage devices up to 80 V as well as digital and analog operation

at 3.3 V, the I3T80 process family features a wide range of capabilities

in a single IC.

850EUR/mm^2 with min 10 mm^2 (min 8500 EUR)

C5 Optimized for 5 V mixed−signal applications, the C5 process family from

ON Semiconductor offers a medium−density, high−performance mixed−signal

technology capable of integrating complex analog functions, digital

content and 20 V capability. This process delivers the advantages of

a dedicated mixed−signal 0.5µm process without the costs associated

with the extra mask steps of a BCD process. Low−voltage transistors

are also available for the 0.5µm process making it well−suited for

low−power applications.

1150EUR/mm^2 with min 5 mm^2 (min 5750 EUR)

P.S. Подробнее про I3T50: https://www.onsemi.com/products/product-taxonomy/custom-foundry-services/i3t50-process-technology - там кроме PMOS и NMOS (обычных и высоковольтных) есть ещё биполярные транзисторы (NPN), диоды, стабилитроны, конденсаторы, резисторы и всякие библиотечные компоненты типа SRAM, ROM и даже OTP и EEPROM

-

askfind

- Devil

- Posts: 896

- Joined: 04 Jan 2016 09:15

- Location: Russia, S.- Peterburg

Re: Разработка и заказ троичной микросхемы

Будет ли возможность купить у Вас микросхемы?

"Ученье свет, а неученье — тьма. Дело мастера боится, и коль крестьянин не умеет сохою владеть — хлеб не родится." (С)

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

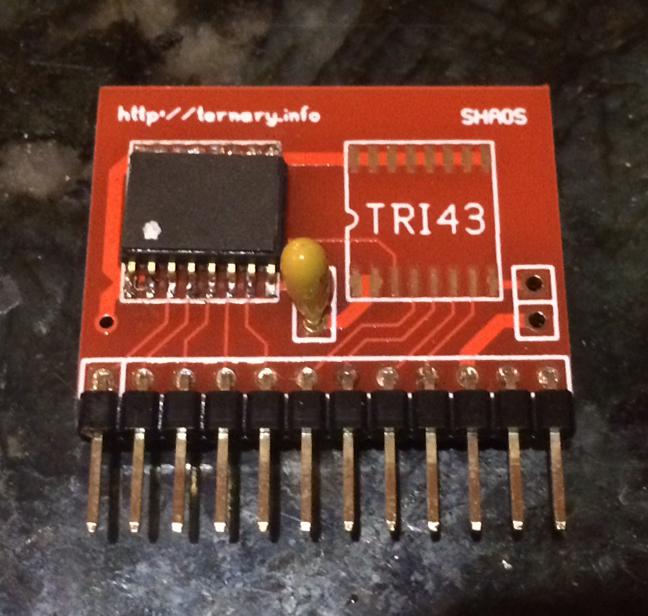

Она и сейчас есть - например вот эту сборку могу продать по себестоимости - три сотни баксовaskfind wrote:Будет ли возможность купить у Вас микросхемы?

Shaos wrote:Спаял одно-мухный вариант:

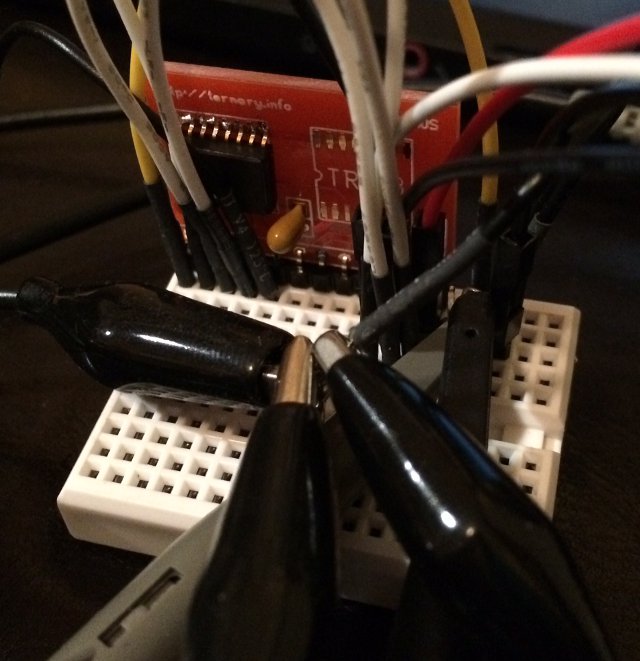

и потестил с помощью вот этой штуки:

В-принципе работает, но немножко медленно (10 кГц), на чуть большем напряжении (-5В...+5В) и пороги чуть съехали по сравнению с моделью:

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Разработка и заказ троичной микросхемы

Ты с такими порогами первую серию троичных микросхем и заказывал?Shaos wrote:Задал более реальные пороги у NMOS и PMOS транзисторов (как выяснилось они в LTspiceIV нулевые по умолчанию), ...

iLavr

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Микросхему я тестировал не в LTspiceIV, а в ngspice с настоящими моделями с техпроцесса OnSemi CMOS 0.5um (транзисторы описаны в BSIM3 с правильными порогами и т.д.)Lavr wrote:Ты с такими порогами первую серию троичных микросхем и заказывал?Shaos wrote:Задал более реальные пороги у NMOS и PMOS транзисторов (как выяснилось они в LTspiceIV нулевые по умолчанию), ...

И вообще в LTspiceIV невозможно симулировать произвольную SPICE-схему т.к. оно поддерживает только то, что нарисовано в ней мышкой (net-файл генерится временно в момент симуляции)

А я вытаскивал SPICE из топологии микросхемы на уровне Magic и затем скармливал в ngspice через интерфейс командной строки...

-

askfind

- Devil

- Posts: 896

- Joined: 04 Jan 2016 09:15

- Location: Russia, S.- Peterburg

Re: Разработка и заказ троичной микросхемы

Можно ли заказать где-нибудь микроконтроллеры типа серии 145ИК13 и 145ИК18 ?

Есть проект эмулятора калькуляторов на основании редизайна элементов схемы микросхем серии 145 https://github.com/BigEd/emu145

Идея: Использовать модели троичных ферритовых цифровых элементов. Редизайн последовательной вычислительной троичной машины "Сетунь".

Есть проект эмулятора калькуляторов на основании редизайна элементов схемы микросхем серии 145 https://github.com/BigEd/emu145

Идея: Использовать модели троичных ферритовых цифровых элементов. Редизайн последовательной вычислительной троичной машины "Сетунь".

"Ученье свет, а неученье — тьма. Дело мастера боится, и коль крестьянин не умеет сохою владеть — хлеб не родится." (С)

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Про опенсорцный процесс под крылом Гугла я уже слышал, а вот что они ещё и бесплатно предлагают микросхемы сделать - нетСегодня на синусе,

https://www.cnews.ru/news/top/2020-07-06_sozdano_pervoe_v_mire_polnostyu

Открыто первое в мире полностью бесплатное производство микросхем

Google и партнеры запустили первую за всю историю программу по бесплатному производству микросхем для тех, у кого нет финансовой возможности заказать их выпуск. Все расходы, берут на себя авторы проекта, а от участника требуется лишь наличие модели микросхемы, выложенной в открытом доступе, и принятие ряда ограничений, включая используемый при производстве 130-нанометровый техпроцесс.

-

askfind

- Devil

- Posts: 896

- Joined: 04 Jan 2016 09:15

- Location: Russia, S.- Peterburg

Re: Разработка и заказ троичной микросхемы

Интересная новость. надеюсь это будет тенденция и станет возможно заказывать микросхемы.rw6hrm wrote: Открыто первое в мире полностью бесплатное производство микросхем

Google и партнеры запустили первую за всю историю программу по бесплатному производству микросхем .

Будет ли FPGA конкурентом этого движения? Когда можно будет прошивать своё для выпуска на рынок своего "железа" в кристалл.

"Ученье свет, а неученье — тьма. Дело мастера боится, и коль крестьянин не умеет сохою владеть — хлеб не родится." (С)

-

Paguo-86PK

- Maniac

- Posts: 267

- Joined: 12 Apr 2011 20:43

- Location: Tashkent

Разработка и заказ троичной микросхемы

Бесплатное производство процессоров удачливым сорока разбойникам!

P.S.: А я оказался в пролёте: Ничего не готово!

(Не ожидал я столь стремительного развития технологий…)

P.S.: А я оказался в пролёте: Ничего не готово!

(Не ожидал я столь стремительного развития технологий…)

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Смотрю демку-презентацию на ремотиконе хакадея про этот процесс - они как и я таки юзают magic на нижнем уровне и у них есть skywater-pdk для него - так что я могу относительно быстро перетранслировать туда мои наработкиShaos wrote:Про опенсорцный процесс под крылом Гугла я уже слышал, а вот что они ещё и бесплатно предлагают микросхемы сделать - нет

P.S. Вот слайды с этой презентации: http://bit.ly/0-ASIC-slides

P.P.S. Опенсорцная библиотека компонентов:

https://cs.opensource.google/skywater-pdk/skywater-pdk/+/master:libraries/sky130_fd_sc_hd/latest/cells/

(говорят аналоговых компонентов у них пока нет совсем - надеются, что сообщество разработчиков им поможет)

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Вытаскиваю наверх свои выкладки по площади троичного чипа из 2015 года - чтобы потом долго не искатьShaos wrote:Короче расклад такой - я как-то вычислял, что для аналогичной двоичной схемы (с учётом количества состояний и скорректированного количества входов-выходов) транзисторов будет примерно в 2 раза меньше, нежели в троичной схеме, сделанной на CMOS (оно и понятно, т.к. один порог мы заменяем на два), НО если верить одной статье, то в среднем 70% площади кристалла уходит под соединения, 20% изоляцию и только 10% на транзисторы - т.е. имея в 2 раза больше транзисторов, но в log(3)/log(2)=1.585 меньше соединений, мы получаем 10%*2 + 20% + 70%/1.585 = 84.16% т.е. в этом смысле троичные CMOS-решения должны быть в среднем на 15.84% компактнееangry_troll wrote:И ещё, ты вот рисовал схемы 3-уровневой логики с 2 питаниями на кмоп, а насколько (и вообще получается ли) выигрыш или проигрыш по транзисторам, если то же самое сделать 2 проводами с кодами, например, 00, 01 и 10 в двоичной кмоп-логике?

P.S. Про 70% ещё Mac Buster писал в 2010 году: http://www.nedopc.org/forum/viewtopic.php?p=1680#p1680

-

Lavr

- Supreme God

- Posts: 17014

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Разработка и заказ троичной микросхемы

А есть ссылка или какая-либо ориентировка на эту "одну статью" ?Shaos wrote: НО если верить одной статье, то в среднем 70% площади кристалла уходит под соединения, 20% изоляцию и только 10% на транзисторы

...

P.S. Про 70% ещё Mac Buster писал в 2010 году: http://www.nedopc.org/forum/viewtopic.php?p=1680#p1680

"Пенсионер" Mac Buster в 2010 году никаких ссылок тоже не привёл...

iLavr

-

Shaos

- Admin

- Posts: 25050

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Разработка и заказ троичной микросхемы

Да вот я чото найти не могу никак первоисточникLavr wrote:А есть ссылка или какая-либо ориентировка на эту "одну статью" ?Shaos wrote: НО если верить одной статье, то в среднем 70% площади кристалла уходит под соединения, 20% изоляцию и только 10% на транзисторы

...

P.S. Про 70% ещё Mac Buster писал в 2010 году: http://www.nedopc.org/forum/viewtopic.php?p=1680#p1680

"Пенсионер" Mac Buster в 2010 году никаких ссылок тоже не привёл...

По идее площадь межсоединений сильно зависит от техпроцесса

Например если у нас 5 или 7 слоёв метализации, то они вообще поверх транзисторов могут идти и никак площади транзисторов мешать не будут...