Приступаю к реализации новой платы NedoPC-90 (серия B) с кодовым названием Xavroska-2009 "Triangle". Плата была задумана ещё в апреле (см. http://shaos.net/notes/33_01.jpg ), но руки до реализации дошли только сейчас.

Плата будет с AVR-ом ATMEGA8535 от Atmel (в PLCC-корпусе) и CPLD XC9572 от Xilinx (тоже в PLCC). Кроме того на плате будет 8К энергонезависимой памяти, последовательный порт (для общения с компьютером), а также некоторые разъёмы (включая порт NI-15), опциональные переключаетели и светодиоды (совмещенные красно-зленые либо обычные, но в два раза больше).

Плату можно будет собрать в двух вариантах:

1) NedoPC-90-B/T - плата для эмуляции троичного компьютера 3niti alpha с панелью управления как вот тут;

2) NedoPC-90-B/X - универсальная плата с AVR, CPLD, кучей I/O и тремя аналоговыми входами.

P.S. Плата будет программно совместима с оригинальной NedoPC-90 от SfS, а также NedoPC-90.AVROS (и соответственно Xavroska v1.0)

P.P.S. Пользуясь той же платой можно будет собрать 3.3-вольтовые варианты девайсов

P.P.P.S. топик закрыт - устарел, все идём сюда: viewtopic.php?t=9141

Xavroska-2009 "Triangle" (первое приближение)

Moderator: Shaos

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Xavroska-2009 "Triangle" (первое приближение)

Last edited by Shaos on 13 Sep 2009 12:02, edited 5 times in total.

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Подключение ATMEGA претерпело некоторые мелкие изменения (оставаясь при этом совместимым с NedoPC-90), кроме того придётся поставить один мультиплексор 74151 на чтение состояния четырёх троичных переключателей, т.к. логики не хватает:

Code: Select all

ATMEGA8535 (PLCC-44) for NedoPC-90-B:

Pin 01: GND Ground

Pin 02: PB0 (XCK/T0) Green LED 1

Pin 03: PB1 (T1) Red LED 1

Pin 04: PB2 (AIN0/INT2) Green LED 2

Pin 05: PB3 (AIN1/OC0) Red LED 2

Pin 06: PB4 (SS) Multiplexed input from switches 1,2,3,4

Pin 07: PB5 (MOSI) Prog MOSI

Pin 08: PB6 (MISO) Prog MISO

Pin 09: PB7 (SCK) Prog SCK

Pin 10: RESET Prog RESET + reset scheme

Pin 11: VCC +5 Volts

Pin 12: GND Ground

Pin 13: XTAL2 Optional crystal 8 MHz

Pin 14: XTAL1 Optional crystal 8 MHz

Pin 15: PD0 (RXD) Serial port RxD

Pin 16: PD1 (TXD) Serial port TxD

Pin 17: PD2 (INT0) External I/O (optional KeyPad)

Pin 18: PD3 (INT1) Green LED 3 | External I/O (optional)

Pin 19: PD4 (OC1B) Red LED 3 | External I/O (optional)

Pin 20: PD5 (OC1A) A0 for switch multiplexer

Pin 21: PD6 (ICP1) A1 for switch multiplexer

Pin 22: PD7 (OC2) A2 for switch multiplexer

Pin 23: VCC +5 Volts

Pin 24: GND Ground

Pin 25: PC0 (SCL) D0 (NI-15)

Pin 26: PC1 (SDA) D1 (NI-15)

Pin 27: PC2 D2 (NI-15)

Pin 28: PC3 D3 (NI-15)

Pin 29: PC4 D4 (NI-15)

Pin 30: PC5 D5 (NI-15)

Pin 31: PC6 (TOSC1) D6 (NI-15)

Pin 32: PC7 (TOSC2) D7 (NI-15)

Pin 33: AVCC +5 Volts

Pin 34: GND Ground

Pin 35: AREF +5 Volts

Pin 36: PA7 (ADC7) Switch 12 | Analog INPUT 3

Pin 37: PA6 (ADC6) Switch 11 | Analog INPUT 2

Pin 38: PA5 (ADC5) Switch 10 | Analog INPUT 1

Pin 39: PA4 (ADC4) _WR (NI-15) + _WE (RAM)

Pin 40: PA3 (ADC3) _RD (NI-15) + _OE (RAM)

Pin 41: PA2 (ADC2) M_IO (NI-15)

Pin 42: PA1 (ADC1) ALE (NI-15)

Pin 43: PA0 (ADC0) _CS (NI-15)

Pin 44: VCC +5 Volts

Last edited by Shaos on 12 Sep 2009 10:14, edited 7 times in total.

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Подключение CPLD:

MCU и CPLD будут общаться по шине NI-15 (через которую также будет доступна память). В варианте сборки NedoPC-90-B/X всего получается до 48 внешних контактов, которые можно запрограммировать как на вход, так и на выход (42 от XC9572 + 6 от ATMEGA8535, причём 3 из которых могут быть использованы как аналоговые входы). При использовании внешней шины NI-15 (для других внешних устройств), память может временно отключаться от шины - будет предусмотрен специальный внутренний регистр.

Code: Select all

XC9572 (PLCC84) for NedoPC-90-B:

Pin 01: 1-02 Green LED4 | External I/O (optional)

Pin 02: 1-05 Red LED4 | External I/O (optional)

Pin 03: 1-06 Green LED5 | External I/O (optional)

Pin 04: 1-01 Red LED5 | External I/O (optional)

Pin 05: 1-08 Green LED6 | External I/O (optional)

Pin 06: 1-03 Red LED6 | External I/O (optional)

Pin 07: 1-04 Internal _CS (NI-15)

Pin 08: (GND) Ground

Pin 09: 1-09 (GCK1) Switch 15+ | External I/O (optional)

Pin 10: 1-11 (GCK2) ALE (NI-15)

Pin 11: 1-07 Switch 15- | External I/O (optional)

Pin 12: 1-14 (GCK3) _WR (NI-15)

Pin 13: 1-10 Green LED7 | External I/O (optional)

Pin 14: 1-15 Red LED7 | External I/O (optional)

Pin 15: 1-17 M_IO (NI-15)

Pin 16: (GND) Ground

Pin 17: 3-02 Switch 14+ | External I/O (optional)

Pin 18: 1-12 Switch 14- | External I/O (optional)

Pin 19: 3-05 _RD (NI-15)

Pin 20: 1-13 Green LED8 | External I/O (optional)

Pin 21: 3-08 Red LED8 | External I/O (optional)

Pin 22: (VCCIO) +5 Volts | +3.3 Volts (optional)

Pin 23: 1-16 Green LED9 | External I/O (optional)

Pin 24: 1-18 Red LED9 | External I/O (optional)

Pin 25: 3-01 Green LED10 | External I/O (optional)

Pin 26: 3-09 Red LED10 | External I/O (optional)

Pin 27: (GND) Ground

Pin 28: (TDI)

Pin 29: (TMS)

Pin 30: (TCK)

Pin 31: 3-03 Green LED11 | External I/O (optional)

Pin 32: 3-04 Red LED11 | External I/O (optional)

Pin 33: 3-11 Green LED12 | External I/O (optional)

Pin 34: 3-06 Red LED12 | External I/O (optional)

Pin 35: 3-07 Green LED13 | External I/O (optional)

Pin 36: 3-14 Red LED13 | External I/O (optional)

Pin 37: 3-15 Green LED14 | External I/O (optional)

Pin 38: (VCCINT) +5 Volts

Pin 39: 3-17 Red LED14 | External I/O (optional)

Pin 40: 3-10 Green LED15 | External I/O (optional)

Pin 41: 3-12 Red LED15 | External I/O (optional)

Pin 42: (GND) Ground

Pin 43: 3-13 Switch 13+ | External I/O (optional)

Pin 44: 4-02 D0 (NI-15)

Pin 45: 3-16 Switch 13- | External I/O (optional)

Pin 46: 4-01 D1 (NI-15)

Pin 47: 4-05 D2 (NI-15)

Pin 48: 4-08 D3 (NI-15)

Pin 49: (GND) Ground

Pin 50: 4-09 D4 (NI-15)

Pin 51: 4-03 D5 (NI-15)

Pin 52: 4-04 D6 (NI-15)

Pin 53: 4-11 D7 (NI-15)

Pin 54: 4-06 Switch 5+ | External I/O (optional)

Pin 55: 4-07 Switch 5- | External I/O (optional)

Pin 56: 4-14 Switch 6+ | External I/O (optional)

Pin 57: 4-10 Switch 6- | External I/O (optional)

Pin 58: 4-12 Switch 7+ | External I/O (optional)

Pin 59: (TDO)

Pin 60: (GND) Ground

Pin 61: 4-13 Switch 7- | External I/O (optional)

Pin 62: 4-16 Switch 8+ | External I/O (optional)

Pin 63: 2-01 _CE (RAM)

Pin 64: (VCCIO) +5 Volts | +3.3 Volts (optional)

Pin 65: 4-15 Switch 8- | External I/O (optional)

Pin 66: 4-17 Switch 9+ | External I/O (optional)

Pin 67: 2-03 A0 (RAM)

Pin 68: 2-04 A1 (RAM)

Pin 69: 2-02 A2 (RAM)

Pin 70: 2-05 A3 (RAM)

Pin 71: 2-06 A4 (RAM)

Pin 72: 2-08 A5 (RAM)

Pin 73: (VCCINT) +5 Volts

Pin 74: 2-09 (GSR) Reset

Pin 75: 2-10 A6 (RAM)

Pin 76: 2-07 (GTS1) External _CS (NI-15) | External I/O (optional)

Pin 77: 2-11 (GTS2) Switch 9- | External I/O (optional)

Pin 78: (VCCINT) +5 Volts

Pin 79: 2-12 A7 (RAM)

Pin 80: 2-13 A8 (RAM)

Pin 81: 2-14 A9 (RAM)

Pin 82: 2-16 A10 (RAM)

Pin 83: 2-15 A11 (RAM)

Pin 84: 2-17 A12 (RAM)

Last edited by Shaos on 07 Sep 2009 10:10, edited 3 times in total.

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Вот первый рабочий вариант - продолжаю тестить в симуляторе:

Code: Select all

---------------------------------------------------------------------------------

-- Company: NedoPC.org

-- Engineer: Alexander A. Shabarshin

--

-- Create Date: 15:52:28 09/06/2009

-- Design Name: x2009r2

-- Module Name: top - Behavioral

-- Project Name: Xavroska 2009 "Triangle" (NedoPC-90-B/T)

-- Target Devices: XC9572

-- Tool versions: ISE 10.1.03

-- Description:

--

-- Dependencies: top.ucf must have pin list

--

-- Revision: 2

-- Revision 0.2 - working one...

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity top is

Port ( RGLED4 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED5 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED6 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED7 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED8 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED9 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED10 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED11 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED12 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED13 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED14 : out STD_LOGIC_VECTOR (1 downto 0);

RGLED15 : out STD_LOGIC_VECTOR (1 downto 0);

TRISW5 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW6 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW7 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW8 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW9 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW13 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW14 : in STD_LOGIC_VECTOR (1 downto 0);

TRISW15 : in STD_LOGIC_VECTOR (1 downto 0);

NI_DATA : inout STD_LOGIC_VECTOR (7 downto 0);

NI_I_CS : in STD_LOGIC;

NI_O_CS : out STD_LOGIC;

NI_ALE : in STD_LOGIC;

NI_M_IO : in STD_LOGIC;

NI_RD : in STD_LOGIC;

NI_WR : in STD_LOGIC;

MEM_CS : out STD_LOGIC;

MEM_ADDR : inout STD_LOGIC_VECTOR (12 downto 0);

RESET : in STD_LOGIC );

end top;

architecture Behavioral of top is

signal MEM_USE: STD_LOGIC;

begin

process (RESET,NI_I_CS,NI_ALE,NI_M_IO,NI_RD,NI_WR)

begin

if RESET = '0'

then -- Reset

RGLED4 <= "11";

RGLED5 <= "11";

RGLED6 <= "11";

RGLED7 <= "11";

RGLED8 <= "11";

RGLED9 <= "11";

RGLED10 <= "11";

RGLED11 <= "11";

RGLED12 <= "11";

RGLED13 <= "11";

RGLED14 <= "11";

RGLED15 <= "11";

NI_O_CS <= '1';

MEM_CS <= '1';

MEM_USE <= '0';

MEM_ADDR <= "0000000000000";

NI_DATA <= "ZZZZZZZZ";

else

if NI_I_CS = '0'

then -- Bus is ready to work

if NI_M_IO = '1' and MEM_USE = '1'

then -- Memory in use

NI_O_CS <= '1';

if NI_WR = '0' or NI_RD = '0'

then

MEM_CS <= '0';

else

MEM_CS <= '1';

end if;

else -- Memory is hidden

NI_O_CS <= '0';

end if;

if NI_ALE'event and NI_ALE = '1'

then -- Save lower address

MEM_ADDR(7 downto 0) <= NI_DATA;

end if;

if NI_ALE = '0'

then

if NI_WR'event and NI_WR='1'

then -- Write event ends

if NI_M_IO = '0'

then -- Register write

if MEM_ADDR(7 downto 0) = "10000000" -- 0x80

then -- Save higher address

MEM_ADDR(12 downto 8) <= NI_DATA(4 downto 0);

MEM_USE <= not NI_DATA(7);

else

if MEM_ADDR(7 downto 0) = "10000001" -- 0x81

then -- Change RGLEDs 4,5,6

RGLED4 <= NI_DATA(1 downto 0);

RGLED5 <= NI_DATA(3 downto 2);

RGLED6 <= NI_DATA(5 downto 4);

else

if MEM_ADDR(7 downto 0) = "10000010" -- 0x82

then -- Change RGLEDs 7,8,9

RGLED7 <= NI_DATA(1 downto 0);

RGLED8 <= NI_DATA(3 downto 2);

RGLED9 <= NI_DATA(5 downto 4);

else

if MEM_ADDR(7 downto 0) = "10000011" -- 0x83

then -- Change RGLEDs 10,11,12

RGLED10 <= NI_DATA(1 downto 0);

RGLED11 <= NI_DATA(3 downto 2);

RGLED12 <= NI_DATA(5 downto 4);

else

if MEM_ADDR(7 downto 0) = "10000100" -- 0x84

then -- Change RGLEDs 13,14,15

RGLED13 <= NI_DATA(1 downto 0);

RGLED14 <= NI_DATA(3 downto 2);

RGLED15 <= NI_DATA(5 downto 4);

end if;

end if;

end if;

end if;

end if;

end if;

end if;

if NI_RD'event and NI_RD='0'

then -- Read event

if NI_M_IO = '0'

then -- Register read

if MEM_ADDR(7 downto 0) = "10000000" -- 0x80

then -- Load higher address

NI_DATA(4 downto 0) <= MEM_ADDR(12 downto 8);

NI_DATA(6 downto 5) <= "00";

NI_DATA(7) <= not MEM_USE;

else

NI_DATA(7 downto 6) <= "00";

if MEM_ADDR(7 downto 0) = "10000001" -- 0x81

then -- Get states of TRISWs 5,6

NI_DATA(1 downto 0) <= "00";

NI_DATA(3 downto 2) <= TRISW5;

NI_DATA(5 downto 4) <= TRISW6;

else

if MEM_ADDR(7 downto 0) = "10000010" -- 0x82

then -- Get states of TRISWs 7,8,9

NI_DATA(1 downto 0) <= TRISW7;

NI_DATA(3 downto 2) <= TRISW8;

NI_DATA(5 downto 4) <= TRISW9;

else

if MEM_ADDR(7 downto 0) = "10000100" -- 0x84

then -- Get states of TRISWs 13,14,15

NI_DATA(1 downto 0) <= TRISW13;

NI_DATA(3 downto 2) <= TRISW14;

NI_DATA(5 downto 4) <= TRISW15;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

else -- Bus is disabled

MEM_CS <= '1';

NI_O_CS <= '1';

-- NI_DATA <= "ZZZZZZZZ";

end if;

if NI_RD='1'

then -- Read event ends

NI_DATA <= "ZZZZZZZZ";

end if;

end if;

end process;

end Behavioral;

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Xavroska-2009 "Triangle" (NedoPC-90-B)

Как вариант сборки можно предложить ещё NedoPC-90-B/D (dual), когда две треугольные половинки не распиливаются, а остаются в пределах одной квадратной платы - в результате мы имеем две идентичные схемы на одной плате, которые могут общаться по шине NI-15 - и туда же можно воткнуть третью плату сверху по диагонали...Shaos wrote:Приступаю к реализации новой платы NedoPC-90 (серия B) с кодовым названием Xavroska-2009 "Triangle". Плата была задумана ещё в апреле (см. http://shaos.net/notes/33_01.jpg ), но руки до реализации дошли только сейчас.

Плата будет с AVR-ом ATMEGA8535 (в PLCC-корпусе) и CPLD XC9572 от Xilinx (тоже в PLCC). Кроме того на плате будет 8К энергонезависимой памяти, последовательный порт (для общения с компьютером), а также некоторые разъёмы (включая порт NI-15), опциональные переключаетели и светодиоды (совмещенные красно-зленые либо обычные, но в два раза больше).

Плату можно будет собрать в двух вариантах:

1) NedoPC-90-B/T - плата для эмуляции троичного компьютера 3niti alpha с панелью управления как вот тут;

2) NedoPC-90-B/X - универсальная плата с AVR, CPLD, кучей I/O и тремя аналоговыми входами.

P.S. Плата будет программно совместима с оригинальной NedoPC-90 от SfS, а также NedoPC-90.AVROS (и соответственно Xavroska v1.0)

P.P.S. Пользуясь той же платой можно будет собрать 3.3-вольтовые варианты девайсов

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Поближе познакомился с Atmega-8515 и подумалось мне что на её основе надо хавроську делать (на форуме кстати уже обсуждалось) - там есть встроенное общение с внешней памятью данных до 64К и почти прямой (и опять же встроенный) интерфейс NI-15! Правда частично сломается совместимость с оригинальной платой NedoPC-90 от SfS (с NI-15 по другому работать надо будет - хотя последняя версия AVROS это уже поддерживает через дефайны) и аналоговые входы исчезнут...

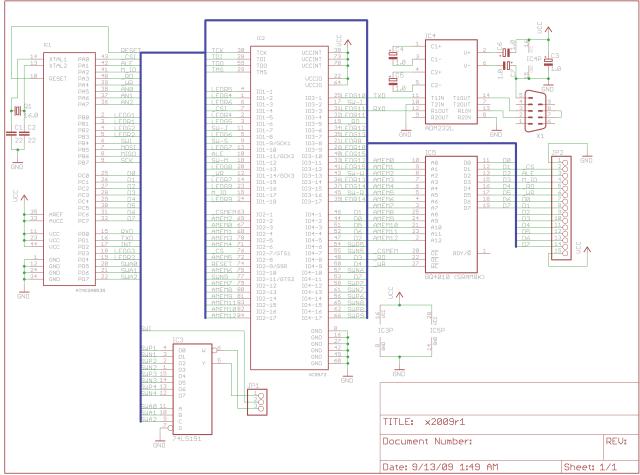

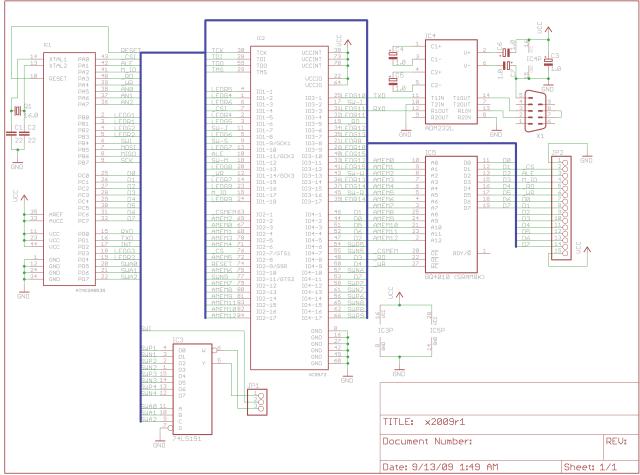

P.S. С атмегой-8535 пока остановился вот на этом (картинка кликабельна):

В схеме использованы компоненты из моей либы:

http://nedopc.org/nedopc/files/shaos_lbr.zip

P.S. С атмегой-8535 пока остановился вот на этом (картинка кликабельна):

В схеме использованы компоненты из моей либы:

http://nedopc.org/nedopc/files/shaos_lbr.zip

-

Shaos

- Admin

- Posts: 25067

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Топик закрыт, т.к. плата будет переработана под ATMEGA8515

Основной топик по теме теперь находится тут:

viewtopic.php?t=9141

Основной топик по теме теперь находится тут:

viewtopic.php?t=9141