На то она и базовая конфигурация, чтобы быть неоптимальной

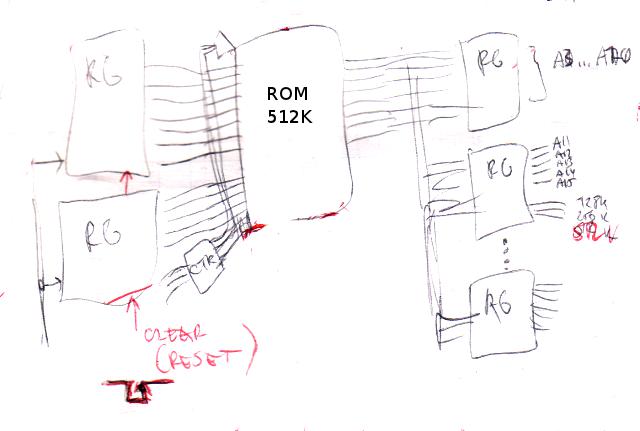

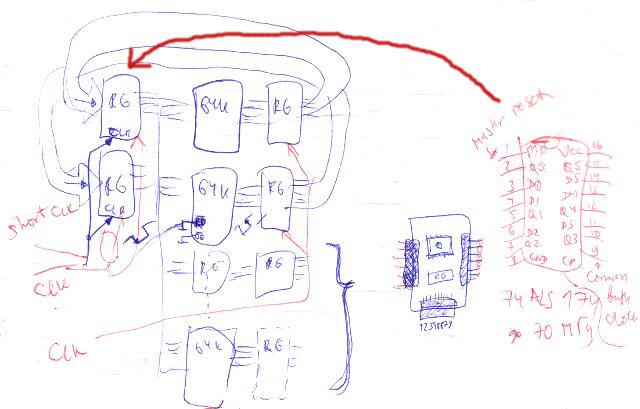

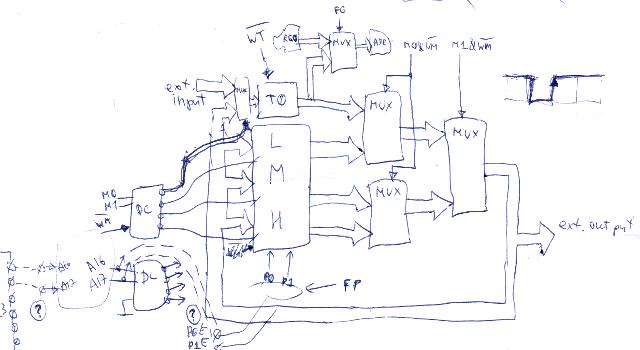

По сути железяки - в базовой конфигурации мы имеем 4 ПЗУ-хи, к выходам которых подключены 4 8-битных регистра - RM0, RM1, RM2 и RM3. Первые два - адрес следующей микрокоманды, RM2 - 8 битов управления (M0,M1,/WM,/WT,P0,P1,FP,FG), RM3 - 8 бит идущих на внешний разъём. Также есть регистр общего назначения RT0 и оперативная память, состоящая из 4 24-битных регистров, 8-битные части которых могут быть записаны значением из RT0, также как и RT0 может быть записан значением из любой 8-битной части этой памяти. Всего получается, что у нас имеется 13 однобайтных регистров для хранения данных.

По умолчанию мы имеем следующие входы:

- 8 внешних сигналов, которые могут идти на 8-битиный регистр RT0 (в базовой конфигурации можно перемычками подсоединить к RM3);

- 2 внешних сигнала, которые могут выбирать какой из 24-битных регистров подключен к выходу оперативной памяти (если FP=1);

- 2 сигнала, сохраняемых для следующего такта.

И выходы:

- 24 сигнала, которые выводят значения из выбранного 24-битного регистра оперативной памяти (может быть использовано как адрес внешней памяти);

- 8 сигналов, которые просто выводят внутреннюю шину данных наружу (сюда может быть подано значение с любого из 13 однобайтных регистров девайса);

- 2 сигнала, сохранённых на предыдущем такте;

- 4 сигнала выбора, дешифрованных из предыдущих двух (половинка дешифратора всё равно оставалась - так я её решил заюзать).

Описание битов управления:

биты 0 и 1 - сигналы M0 и M1, управляющие тем, какой из трёх 8-битных частей выбранного 24-битного регистра используется на чтение или запись (M0=0 M1=0 является специальным случаем, при котором RT0 запитывается от внешнего входа данных);

бит 2 - сигнал /WM, сигнализирующий о том, что оперативная память должна быть записана значением из RT0 по окончанию текущего такта (не для случая, когда M0=0 и M1=0);

бит 3 - сигнал /WT, сигнализирующий о том, что регистр RT0 должен быть записан значением с внутренней шины данных либо со внешнего входа данных (источник управляется сигналами M0 и M1) по окончанию текущего такта;

биты 4 и 5 - сигналы P0 и P1, управляющие тем, какой из 24-битных регистров подключен к выходам оперативной памяти (если FP=0);

бит 6 - сигнал FP, управляющий тем, какие два сигнала P0/P1 используются для выбора 24-битного регистра из четырёх - внутренние (0) или внешние (1);

бит 7 - сигнал FG, управляющий тем, откуда должен браться младший байт адреса следующей микрокоманды - из регистра RM0 (0) или из регистра RT0 (1).