Shaos wrote:Примерно так будет:

Code: Select all

_________________

/RST ______|

______ _ _ _ _

CLK |_| |_| |_| |_| |_ 6.666 MHz

______ ___ ___

CLK1 |___| |___| |_ 3.333 MHz

______ _______

CLK2 |_______| |_ 1.666 MHz

. . .

__________ _

/OE |___________| 450 ns

. ___ .

REGRD _____________| |_____ 150 ns

. . ___

REGWR _________________| |_ 150 ns

| 300ns | 300ns |

^ ^

| 450ns |

| \data ready

\address ready

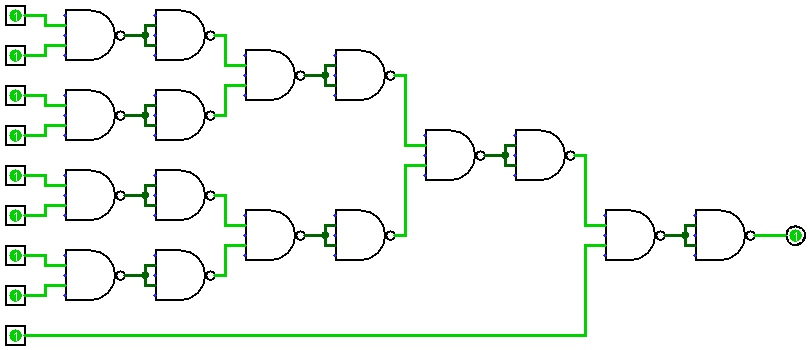

1st stage:

/OE

00 - 1 updated PC at this point (/CE=0 all the time)

01 - 0

10 - 0 strobe execute simple instruction (A=n, R=~R, R1=R2, RST n)

11 - 0 strobe result store (higher priority for accumulator) and PC increment (if enabled)

2nd stage - fast ALU function execution (RRC,RLC,NAN,XOR):

DMUX

00 - 1 connect 1st nibble

10 - 1 strobe accumulator store (1st nibble) / flags

10 - 2 connect 2nd nibble

11 - 2 strobe accumulator store (2nd nibble) / flags

2nd stage - slow ALU function execution (ADC,SBC,ADI,SBI):

00 - 1 connect 1st nibble

01 - 1

10 - 1

11 - 1 strobe accumulator store (low nibble) / flags

00 - 2 connect 2nd nibble

01 - 2

10 - 2

11 - 2 strobe accumulator store (high nibble) / flags

Видимо "slow ALU" небудет (во всяком случае пока), т.е. "fast ALU" уже достаточно медленный, чтобы вместить в себя операции сложения и вычитания:

Code: Select all

_________________

/RST ______|

______ _ _ _ _

CLK |_| |_| |_| |_| |_ 6.666 MHz

______ ___ ___

CLK1 |___| |___| |_ 3.333 MHz

______ _______

CLK2 |_______| |_ 1.666 MHz

1st stage:

__________ _

/OE |___________| 450 ns

. ___ .

REGRD _____________| |_____ 150 ns

. . ___

REGWR _________________| |_ 150 ns

| 300ns | 300ns |

^ ^

| 450ns |

| \data ready

|

\address ready

2nd stage:

_______ .

HALF1 _____| |_________ 300 ns

. ___ .

ASTO1 _________| |_________ 150 ns

. _______

HALF2 _____________| |_ 300 ns

. . ___

ASTO2 _________________| |_ 150 ns

| 300ns | 300ns |

Стробы второй ступени:

HALF1 - это подача на вход АЛУ младшего ниббла аргументов (в случае RRC - старшего);

ASTO1 - сохранение младшего ниббла аккумулятора (в случае RRC - старшего) и флага H;

HALS2 - это подача на вход АЛУ старшего ниббла аргументов (в случае RRC - младшего);

ASTO2 - сохранение старшего ниббла аккумулятора (в случае RRC - младшего) и флагов C,V,Z и S.

По результатам своей работы первая ступень должна сохранить для второй:

- 1 бит признака использования АЛУ (в случае регистровых операций вторая ступень должна простаивать);

- 3 бита кода операции АЛУ;

- 8 бит (прямых или инверсных) второго аргумента (регистр или часть инструкции).

Половинки регистра A всегда будут читаться или писаться как есть - т.е. если следом за A=A+1 идет скажем инструкция G=A, то в результате G получит не A+1, а старшие 4 бита из старого значения A и младшие 4 бита из нового (т.е. неправильное значение в случае переноса из младшего ниббла в старший)...

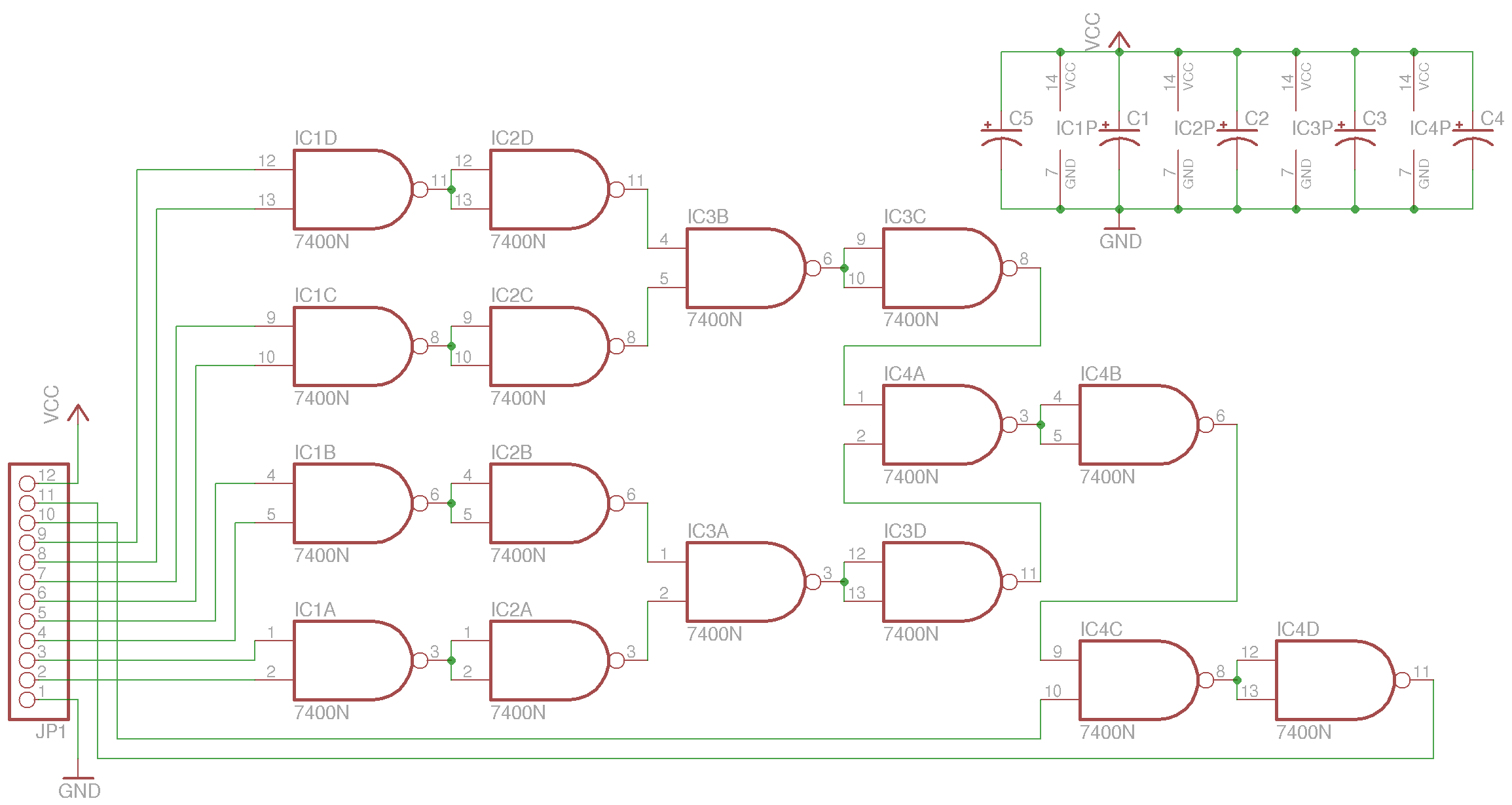

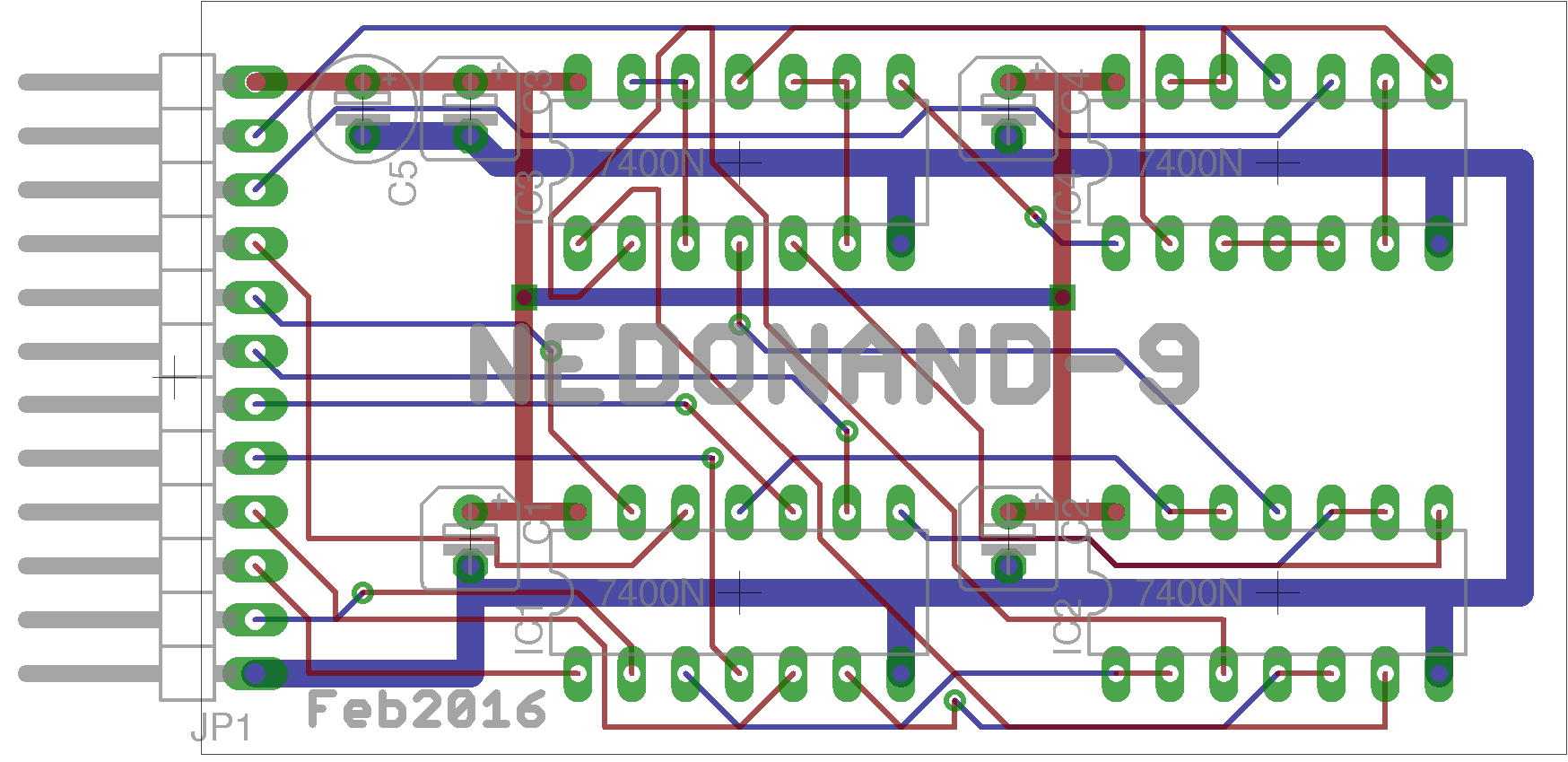

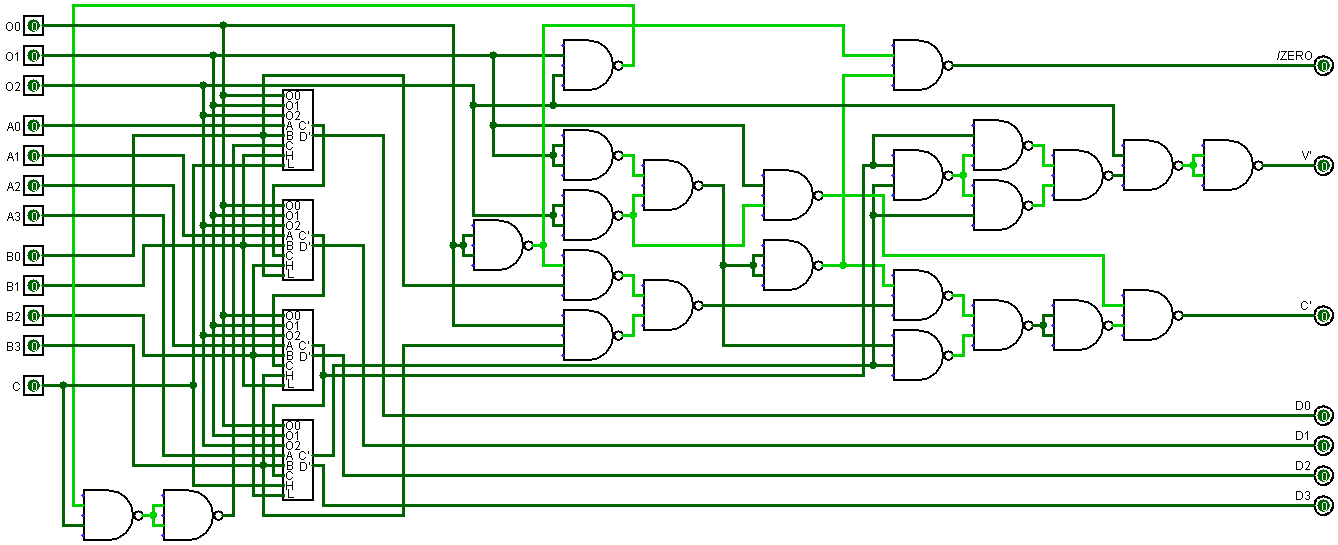

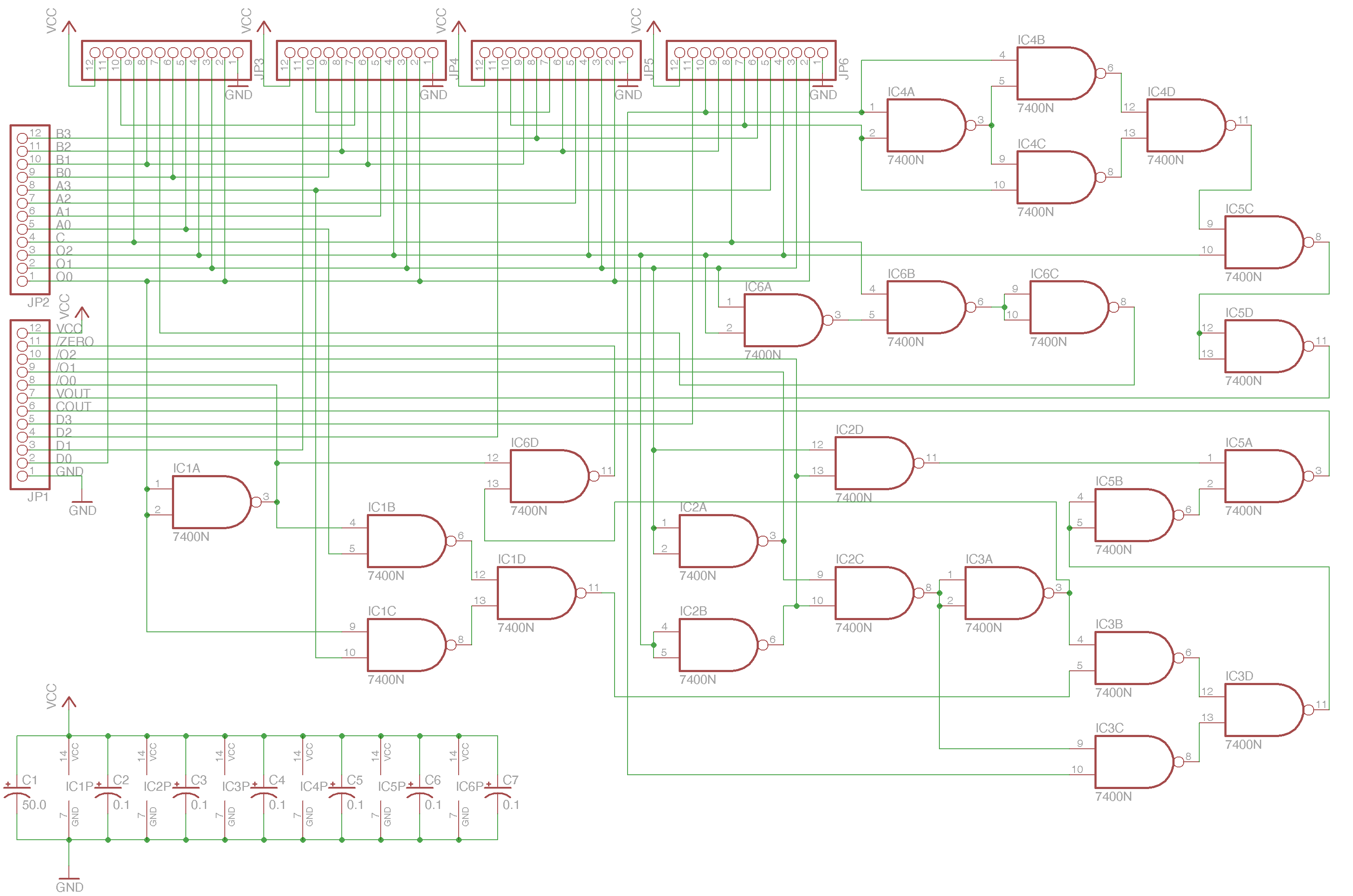

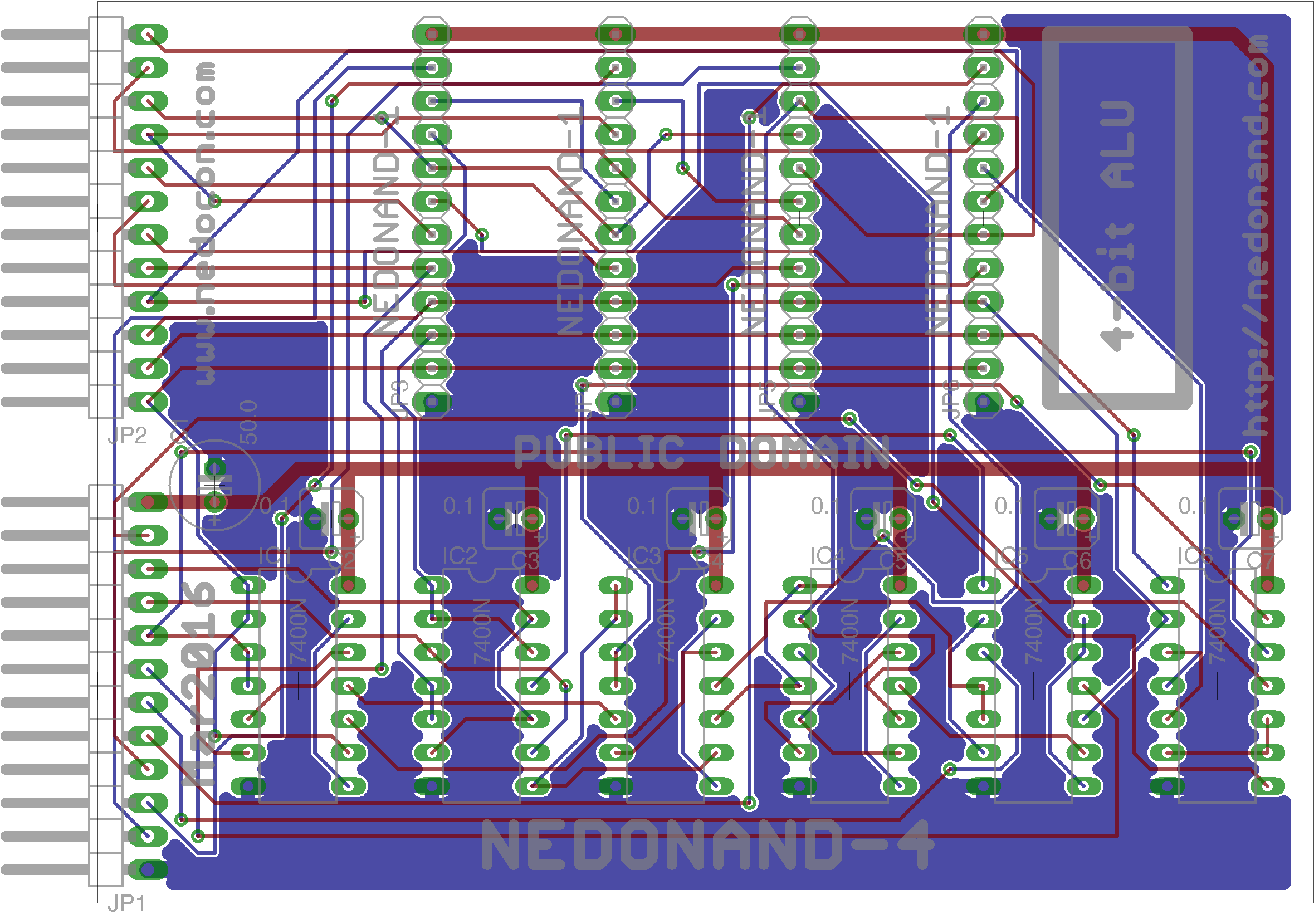

P.S. Блин, в случае операций сдвига (RRC/RLC) "второй аргумент" это "первый аргумент" т.е. первым аргументом не всегда является аккумулятор как я предполагал - придётся резать плату NEDONAND-4 либо переставлять аргументы логикой, зависящей от кода операции...

P.P.S. Решил в результате переделать плату NEDONAND-4 и перезаказать...