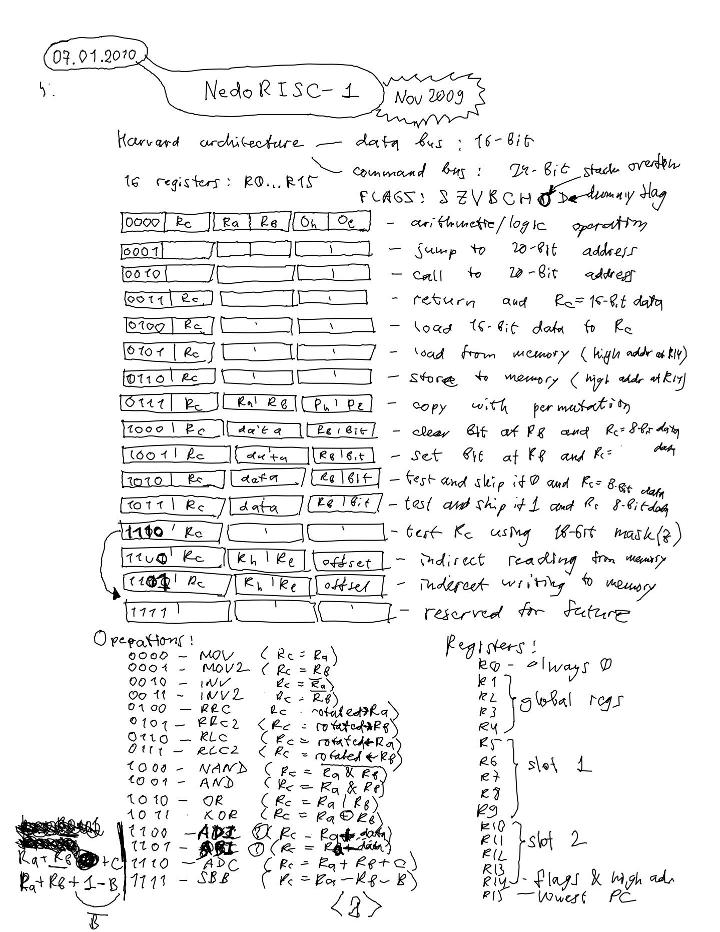

Самодельный процессор nedoRISC-1

Moderator: Shaos

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Robert777

- Junior

- Posts: 2

- Joined: 20 Sep 2010 07:00

- Location: 92.243.181.218

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Пока решил начать с более простого - микрокод в ПЗУ

P.S. Со странички http://www.mycpu.eu/ можно попасть на WebRing самодельных ЦПУ - там их МНОГО

-

jdigreze

- God

- Posts: 1388

- Joined: 02 Jan 2006 02:28

- Location: Abakan

-

d_wanderer

- Senior

- Posts: 180

- Joined: 28 Feb 2006 21:34

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

jdigreze wrote:На реле симпатичнее.

Ну еще проще - на жестянках от консервных банок амириканской оккупационной армии... как Конрад Цузе...d_wanderer wrote:Такую систему команд можно реализовать на шаговых искателях - получится меньше и проще чем на реле.

http://www.compinvent.ru/pervye-izobret ... nrad-cuze/

http://www.3dnews.ru/editorial/konrad_zuse/

http://chernykh.net/content/view/29/54/

PS. Вполне - если учитывать ядерную зиму...

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

2_Shaos

Поскольку он не везде обнуляется, в частности, в 6502 такого нетShaos wrote:теоретический вопрос - почему принято, чтобы логические операции обнуляли флаг C?

Code: Select all

AND

Processor Status after use :

C Carry Flag Not affected

Z Zero Flag Set if A = 0

I Interrupt Disable Not affected

D Decimal Mode Flag Not affected

B Break Command Not affected

V Overflow Flag Not affected

N Negative Flag Set if bit 7 setИ суть, как мне кажется, вот в чём - у меня это получилось, когда я по книжке, на которую ссылался,

http://www.ziddu.com/download/3469497/C ... c.rar.html

http://rapidshare.com/files/150715783/CompStruc.rar

взялся конструировать АЛУ.

После каждой операции надо защелкнуть результат и флаги.

Логические операции на флаг С не влияют, поскольку побитные. Вероятно, схемотехнически защелкнуть предыдущее значение неудобно - получится, что на входе регистра флагов надо защелкнуть состояние собственного выхода, поскольку регистра временного хранения для флагов нет.

А такая ситуация может привести к гонке. Я прикидывал этот вариант,

а потом подумал, что, возможно, из-за этого в С для определённости

защелкивают 0. Можно защелкнуть в С единицу - но это не даст побочного

эффекта, который, на мой взгляд, вот какой.

Есть команда STC: C=1, есть CMC: C=/C; но команды CLC: C=0 непосредственно нет.

Но CLC считается псевдокомандой суть которой выполняет ORA A - на A не влияет, но C=0. (для i8080, конечно же...)

Электронные промышленные устройства. Учебник для вузов. Авторы: Васильев В.И., Гусев Ю.М., Миронов В.Н., издательство "Высшая школа", 1988 г., 303 с.

http://book.tr200.net/v.php?id=430884

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

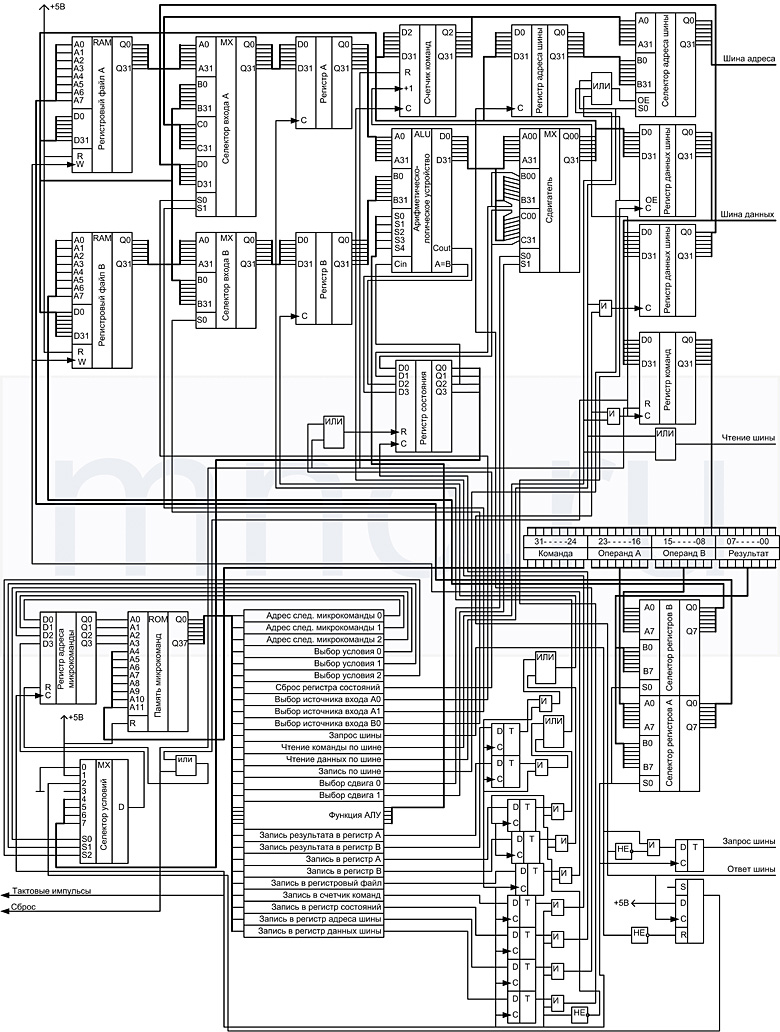

Тут у нас всё потихонечку завяло... но неожиданно конструкция CPU с широкой шиной мне вот тут попалась.Shaos wrote:Кстати эта архитектура "с лёгкостью" расширяется до 32-разрядной...

Схемотехнические решения мне показались интересными, и, надеюсь, будут интересны не только мне.

Проект судя по всему преследует учебные цели и к этой схеме автор подходит через

ряд последовательных шагов.

Думаю этот материал заинтересует всем, кому нравится конструировать процессоры

на мелкой логике.

С точки зрения схемотехники материал представляется мне более полезным, чем

Simulator (Computer Architecture)...

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Мне понравилась довольно весьма детальная проработка схемотехники...Shaos wrote:У чувака микрокод, а я надеялся без микрокоманд обойтись...

Обычно ограничиваются бла-бла-бла-блок-схемами...

А тут - приятно читаемая схема, а уж если ты изволишь желать HardWared RISC CPU,

то хозяин - барин.

Хотя если взглянуть вглубь схемотехники ПЗУ (микрокоманд), то это примерно эквивалентно.

Ну понятно, что HardWared RISC будет шустрее, но и схемотехника более неудобная,

как мне представляется из анализа Машины Мано.

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

На всякий случай - книжка была вот эта:"Любительские телевизионные игры".Shaos wrote:Вспоминаю лишь книжку где на мелкой логике строились видеоигры - лошади какие-то и вроде хоккеисты - я на начальных курсах института был когда её читал - меня впечатлила простота логики отображения прямоугольников на экран телевизора...

iLavr