Как "заюзать" 486

Moderator: Shaos

-

HardWareMan

- Banned

- Posts: 2139

- Joined: 20 Mar 2005 13:41

- Location: От туда

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Спасибо за доки i486 по-любому, но ткни носом в номера страниц конкретных схем, pls.

Листал-листал... то ли "слишкомногабукв", то ли "слишкомногастраниц" - но что-то

схожие с картинкой схемы не попались...

iLavr

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Прозвучало на форуме, что мы ничего не добились по этой конструкции: i486 Homemade Computer

Ну во-первых, вот в этом документе действительно есть типовые схемы включения i486:

i486_Microprocessor_Hardware_Reference_Manual

Если по документу .pdf: pp.466-477, по страницам В30-В41.

Но у автора схема попроще мне представляется... вроде как он не напирал на буферирование шин и т.п.

Что видно из представленных автором фотографий плат:

i486DX 20 МГц и задающий генератор к нему;

NEC D8255AC-2 (1 шт.)

NEC D8251AC (2 шт.)

ADC0809CCN (JM106AT) (1 шт.)

RAM: TOSHIBA TC5565APL-12 (4 шт.) в мануале - TC55257APL

ROM: 27C64 (4 шт.) в мануале - 27C512

Powered serial port to interface serial display - похож на MAXIM MAX202E - 2/2

Из мелочевки я рассмотрел:

74LS161

74LS164

74LS139

74LS74

74LS32

74LS04

74LS00

Может быть постараемся рассмотреть оставшееся и отрисуем эту схему?

Ну во-первых, вот в этом документе действительно есть типовые схемы включения i486:

i486_Microprocessor_Hardware_Reference_Manual

Если по документу .pdf: pp.466-477, по страницам В30-В41.

Но у автора схема попроще мне представляется... вроде как он не напирал на буферирование шин и т.п.

Что видно из представленных автором фотографий плат:

i486DX 20 МГц и задающий генератор к нему;

NEC D8255AC-2 (1 шт.)

NEC D8251AC (2 шт.)

ADC0809CCN (JM106AT) (1 шт.)

RAM: TOSHIBA TC5565APL-12 (4 шт.) в мануале - TC55257APL

ROM: 27C64 (4 шт.) в мануале - 27C512

Powered serial port to interface serial display - похож на MAXIM MAX202E - 2/2

Из мелочевки я рассмотрел:

74LS161

74LS164

74LS139

74LS74

74LS32

74LS04

74LS00

Может быть постараемся рассмотреть оставшееся и отрисуем эту схему?

Last edited by Lavr on 23 Feb 2014 19:39, edited 1 time in total.

iLavr

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Я видел этот ракурс, но при всех манипуляциях с рисунком: яркость, контраст, насыщенность,

гамма-коррекция и др., я на нём ничего не увидел точнее, чем на двух других.

Но учтём, что "правая верхняя похожа на 74LS32".

Кстати, что интересно, 486-й долго использовался во встраиваемых системах но схемотехники

нигде практически нет!

Также я искал, но нигде не нашел какой-либо 486-й тулкит... или трейнер, как будто их тоже нет...

Это которая GoldStar? Мне уже позже показалось, что это дешифратортам видно нижнюю микросхему

74LS139_КР555ИД14, но смущает, что в мануале юзают 74LS138...

А тебе что видно в этой позиции?

iLavr

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

А с изнанки платы - мне так почему-то не кажется...Shaos wrote:хм, в перспективном ракурсе отчётливо видно, что нижняя GoldStar это 74LS00 -

или у меня глаза другой конструкции?

Дело не в глазе - на разных мониторах видно по разному, как ни странно.

Поэтому я и попросил всех глянуть - что им видно. Может и я где-либо ошибся,

хотя смотрел на 3-х мониторах.

iLavr

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Ну хорошо - не будем сомневаться. А с остальной моей расфасовкой ты согласен?

Или где-то есть сомнения?

У меня сомнения с Maximom - хотя он и не имеет принципиальной важности...

У Maxim-а явно видно 02 в конце маркировки, я просто прогуглил "Powered serial

port Maxim 02" и выбрал похожий из списка.

И "правая верхняя похожая на 74LS32" - это какая? Что-то не сориентируюсь никак.

Или где-то есть сомнения?

У меня сомнения с Maximom - хотя он и не имеет принципиальной важности...

У Maxim-а явно видно 02 в конце маркировки, я просто прогуглил "Powered serial

port Maxim 02" и выбрал похожий из списка.

И "правая верхняя похожая на 74LS32" - это какая? Что-то не сориентируюсь никак.

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

правая верхняя из твоих трёх обведенныхLavr wrote:Ну хорошо - не будем сомневаться. А с остальной моей расфасовкой ты согласен?

Или где-то есть сомнения?

У меня сомнения с Maximom - хотя он и не имеет принципиальной важности...

У Maxim-а явно видно 02 в конце маркировки, я просто прогуглил "Powered serial

port Maxim 02" и выбрал похожий из списка.

И "правая верхняя похожая на 74LS32" - это какая? Что-то не сориентируюсь никак.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

К сожалению, качество фотографии разводки не позволяет срисовать схему включения

i486DX просто один к одному, поэтому к процессу придется подойти более творчески.

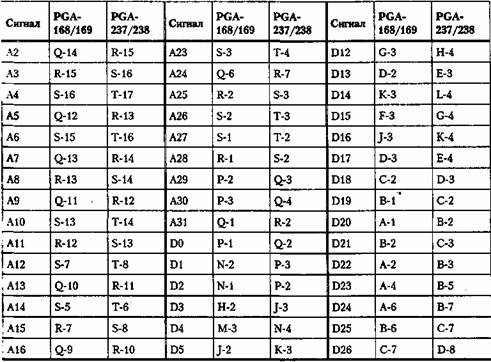

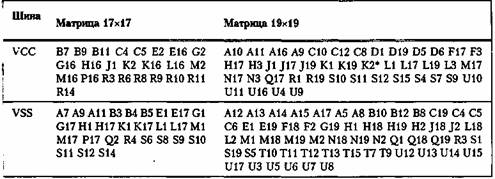

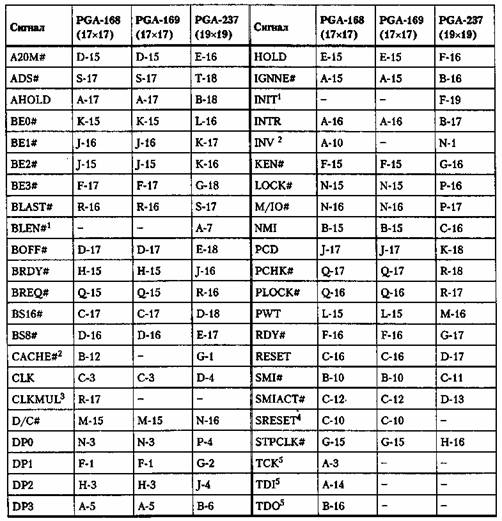

Вот это распиновка процессора i486DX, где я цветом уже пометил большинство нужных

нам выводов.

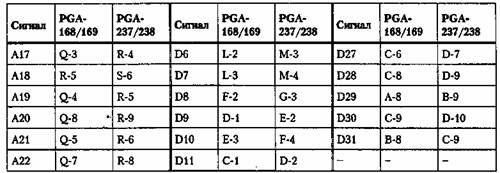

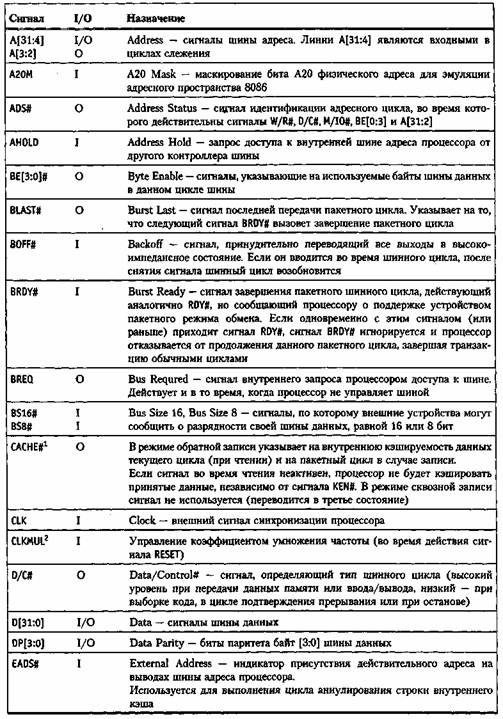

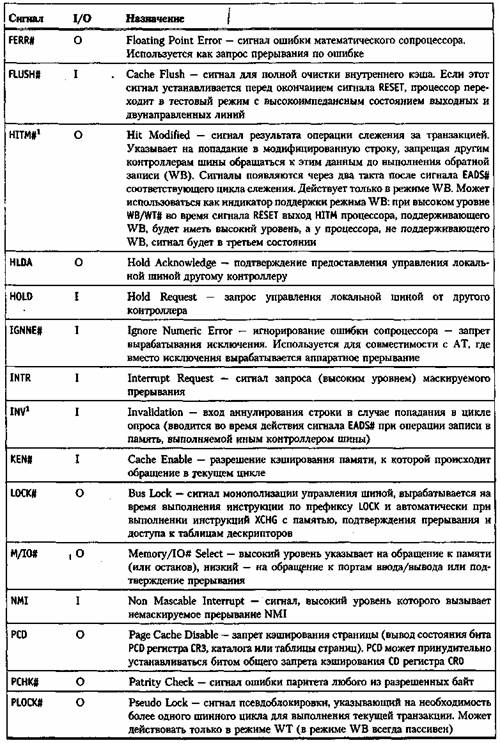

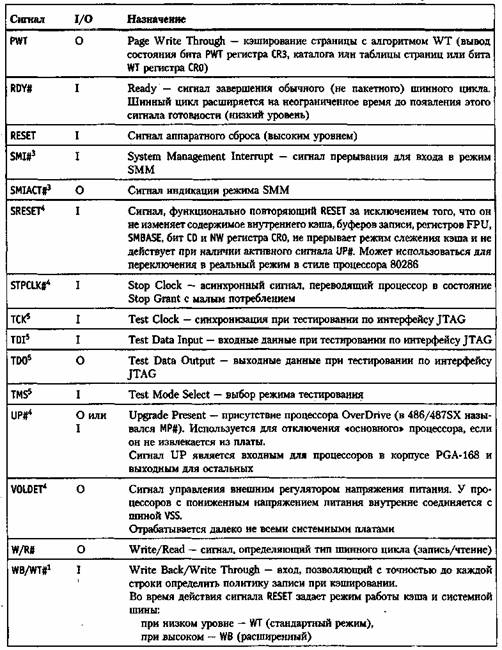

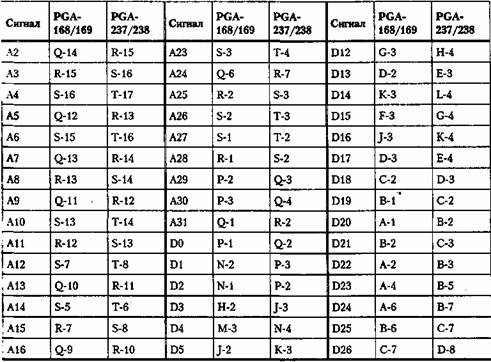

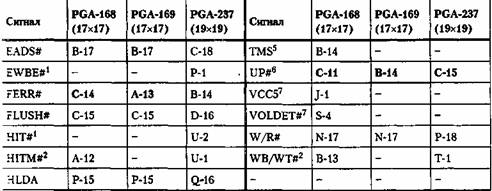

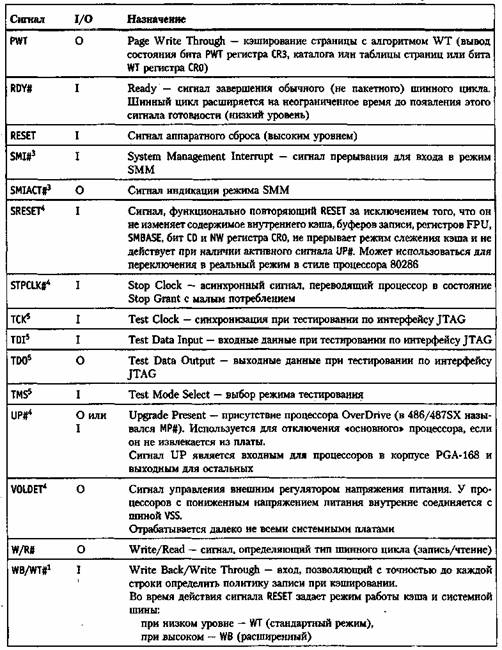

Сигналы шин адреса и данных процессоров 486:

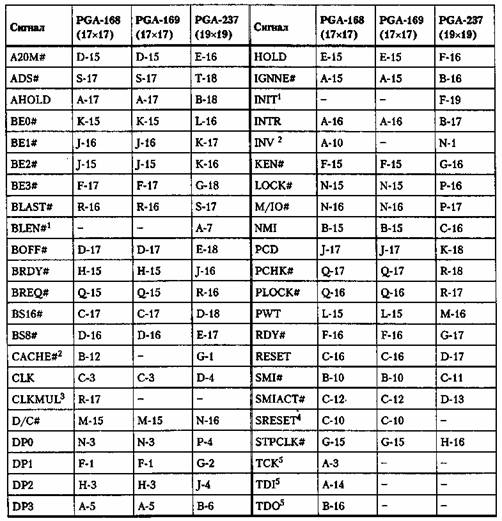

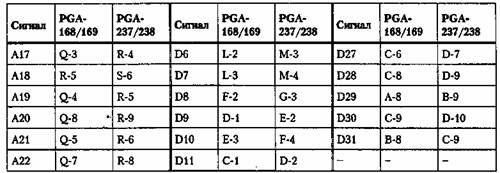

Сигналы управления шины процессоров 486:

1 Имеется только у Pentium OverDrive.

2 Имеется только у процессоров с WT-кэшем.

3 Имеется только у процессоров DX2 и DX4 AMD.

4 У процессора Pentium OverDrive близким по назначению является сигнал INIT.3

Имеется только у процессоров, поддерживающих JTAG.

6 Сигнал UP является входным для процессоров в корпусе PGA-168 и выходным для остальных.

'Имеется только у процессоров с пониженным питанием (3,3 В).

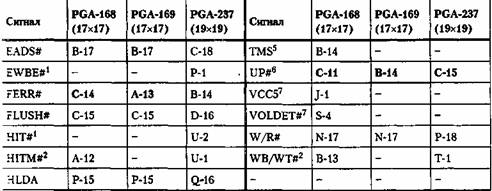

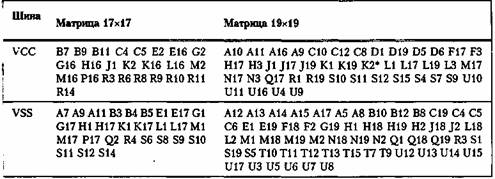

Выводы питания процессоров с шиной 486:

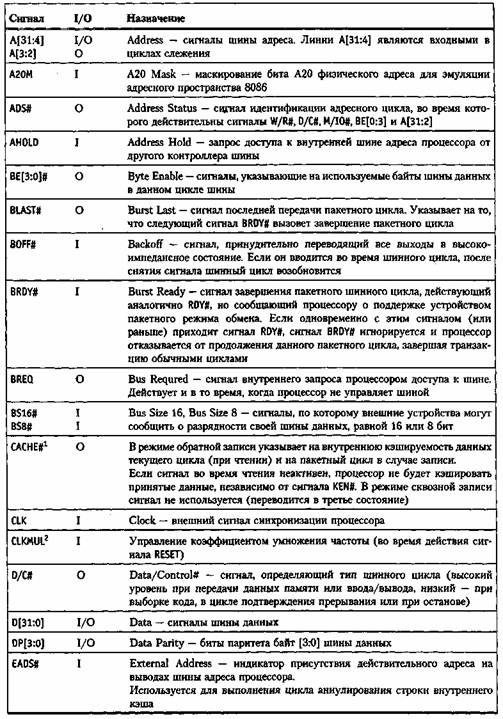

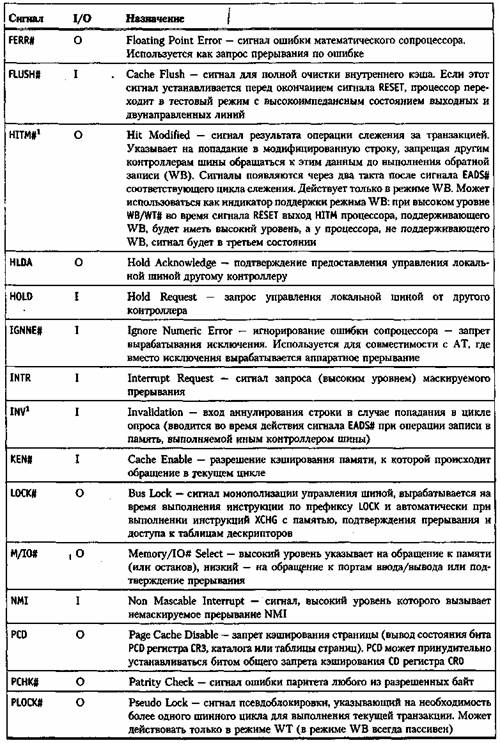

Назначение сигналов процессора 486:

1 Имеется только у процессоров с поддержкой WB-кэша

2 Имеется только у процессоров с умножением частоты.

3 Имеется только у процессоров с поддержкой SMM.

4 Имеется не у всех процессоров.

5 Имеется только у процессоров с поддержкой интерфейса JTAG.

Шина адреса позволяет адресовать 4 Гбайт физической памяти (00000000-FFFFFFFFh) в защищенном режиме и 1 Мбайт из области младших адресов — в реальном режиме.

Сигналом А20М# можно включить принудительное обнуление линии А20 (как для внутреннего кэша, так и для внешних операций). Таким образом эмулируется циклический возврат адреса процессора 8086/88 (сигнал воспринимается только в реальном режиме). При выполнении инструкций ввода/вывода процессор адресуется к области в 64 Кбайт пространства ввода/вывода (00000000-0000FFFFh).

Линии А[31:2] идентифицируют адрес с точностью до двойного слова, а в пределах этого слова сигналы ВЕ[0:3] непосредственно указывают, какие байты используются в данном цикле.

Линии А[31:4], определяющие адрес строки внутреннего кэша, в циклах аннулирования работают на ввод.

Шина данных D[31:0] допускает как 32-разрядный режим обмена, так и 16-и 8-раэрядный в зависимости от состояния входных сигналов BS16# и BS8#.

Сигналы BS16# или BS8# вводятся внешней схемой, если текущий цикл адресуется к 16- или 8-битному устройству, подключенному к младшей части шины данных, BS8# имеет более высокий приоритет.

Для связи с системной шиной, имеющей возможность подключения 8-, 16- и 32-битных устройств (шины ISA и EISA) и полную шину адреса, включающую сигналы А0, А1 и SBHE#, недостающие сигналы генерируются из сигналов ВЕ[0:3]#.

8-битные устройства, наконец, могут подключаться к шине данных без «косого» буфера.

Каждый байт шины данных имеет бит паритета DP[3:0]. Схемы паритета генерируют корректные контрольные биты в циклах записи, а в циклах чтения в случае ошибки паритета только вырабатывается сигнал ошибки на выходе РСНК#, никак не влияющий на работу процессора . Он может использоваться внешними схемами по усмотрению разработчика системной платы. Контроль четности (количество единиц в байте вместе с битом паритета должно быть четным) выполняется для всех байт, участвующих в конкретном цикле.

. Он может использоваться внешними схемами по усмотрению разработчика системной платы. Контроль четности (количество единиц в байте вместе с битом паритета должно быть четным) выполняется для всех байт, участвующих в конкретном цикле.

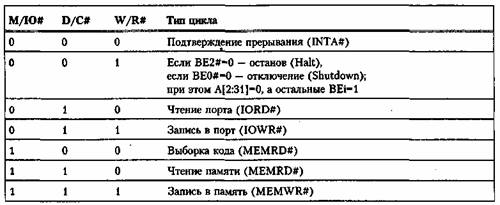

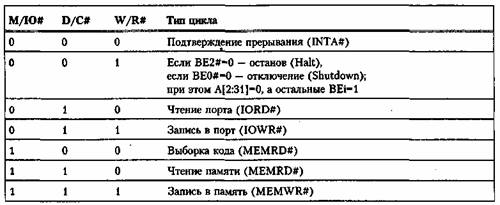

Тип цикла локальной шины определяется сигналами M/IO#, D/C#, W/R#,

...LOCK# во время активности сигнала ADS# :

i486DX просто один к одному, поэтому к процессу придется подойти более творчески.

Вот это распиновка процессора i486DX, где я цветом уже пометил большинство нужных

нам выводов.

Сигналы шин адреса и данных процессоров 486:

Сигналы управления шины процессоров 486:

1 Имеется только у Pentium OverDrive.

2 Имеется только у процессоров с WT-кэшем.

3 Имеется только у процессоров DX2 и DX4 AMD.

4 У процессора Pentium OverDrive близким по назначению является сигнал INIT.3

Имеется только у процессоров, поддерживающих JTAG.

6 Сигнал UP является входным для процессоров в корпусе PGA-168 и выходным для остальных.

'Имеется только у процессоров с пониженным питанием (3,3 В).

Выводы питания процессоров с шиной 486:

Назначение сигналов процессора 486:

1 Имеется только у процессоров с поддержкой WB-кэша

2 Имеется только у процессоров с умножением частоты.

3 Имеется только у процессоров с поддержкой SMM.

4 Имеется не у всех процессоров.

5 Имеется только у процессоров с поддержкой интерфейса JTAG.

Шина адреса позволяет адресовать 4 Гбайт физической памяти (00000000-FFFFFFFFh) в защищенном режиме и 1 Мбайт из области младших адресов — в реальном режиме.

Сигналом А20М# можно включить принудительное обнуление линии А20 (как для внутреннего кэша, так и для внешних операций). Таким образом эмулируется циклический возврат адреса процессора 8086/88 (сигнал воспринимается только в реальном режиме). При выполнении инструкций ввода/вывода процессор адресуется к области в 64 Кбайт пространства ввода/вывода (00000000-0000FFFFh).

Линии А[31:2] идентифицируют адрес с точностью до двойного слова, а в пределах этого слова сигналы ВЕ[0:3] непосредственно указывают, какие байты используются в данном цикле.

Линии А[31:4], определяющие адрес строки внутреннего кэша, в циклах аннулирования работают на ввод.

Шина данных D[31:0] допускает как 32-разрядный режим обмена, так и 16-и 8-раэрядный в зависимости от состояния входных сигналов BS16# и BS8#.

Сигналы BS16# или BS8# вводятся внешней схемой, если текущий цикл адресуется к 16- или 8-битному устройству, подключенному к младшей части шины данных, BS8# имеет более высокий приоритет.

Для связи с системной шиной, имеющей возможность подключения 8-, 16- и 32-битных устройств (шины ISA и EISA) и полную шину адреса, включающую сигналы А0, А1 и SBHE#, недостающие сигналы генерируются из сигналов ВЕ[0:3]#.

8-битные устройства, наконец, могут подключаться к шине данных без «косого» буфера.

Каждый байт шины данных имеет бит паритета DP[3:0]. Схемы паритета генерируют корректные контрольные биты в циклах записи, а в циклах чтения в случае ошибки паритета только вырабатывается сигнал ошибки на выходе РСНК#, никак не влияющий на работу процессора

Тип цикла локальной шины определяется сигналами M/IO#, D/C#, W/R#,

...LOCK# во время активности сигнала ADS# :

iLavr

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Теперь пару слов о том, в какую типовую схемотехнику это описание 80486 выливается:

Организация интерфейса с 32-битными устройствами ввода-вывода

Организация интерфейса с переменным размером шины данных: 16 бит

Организация интерфейса с 8-битными устройствами ввода-вывода

Построение дешифратора сигналов A1, BHE# и BLE#

Построение дешифратора адреса

Поскольку в номенклатуре схем мелкой логики мы не обнаружили буферных элементов,

авторская схема включения 80486, по-видимому, сильно упрощена, и похоже, что упор

сделан на полную 32-разрядность.

Что ж... будем посмотреть!

Организация интерфейса с 32-битными устройствами ввода-вывода

Организация интерфейса с переменным размером шины данных: 16 бит

Организация интерфейса с 8-битными устройствами ввода-вывода

Построение дешифратора сигналов A1, BHE# и BLE#

Построение дешифратора адреса

Поскольку в номенклатуре схем мелкой логики мы не обнаружили буферных элементов,

авторская схема включения 80486, по-видимому, сильно упрощена, и похоже, что упор

сделан на полную 32-разрядность.

Что ж... будем посмотреть!

iLavr

-

Bill

- Fanat

- Posts: 92

- Joined: 25 Jan 2014 21:54

- Location: 37.113.169.14

А какие именно буферы нужны? По-моему их много всяких, хороших и разных. Или я чего-то не понял?Lavr wrote:Поскольку в номенклатуре схем мелкой логики мы не обнаружили буферных элементов,

авторская схема включения 80486, по-видимому, сильно упрощена, и похоже, что упор

сделан на полную 32-разрядность.

Что ж... будем посмотреть!