Тема с компьютером на 86/88 меня заинтересовала, но я уже удовлетворил свои желания попробовать разные способы макетирования - МГТФ, беспаечная макетная плата, монтаж накруткой (вообще не пошел - наверное, руки совсем кривые).

Соответственно, решил одним махом двух зайцев убить - во первых, научиться разрабатывать печатные платы и, во вторых, получить способ очень быстрого экспериментирования вообще без проводов.

В принципе, я подобное уже делал - viewtopic.php?t=10688&start=15#113957 , однако обилие МГТФ и там у меня быстро сбило энтузиазм.

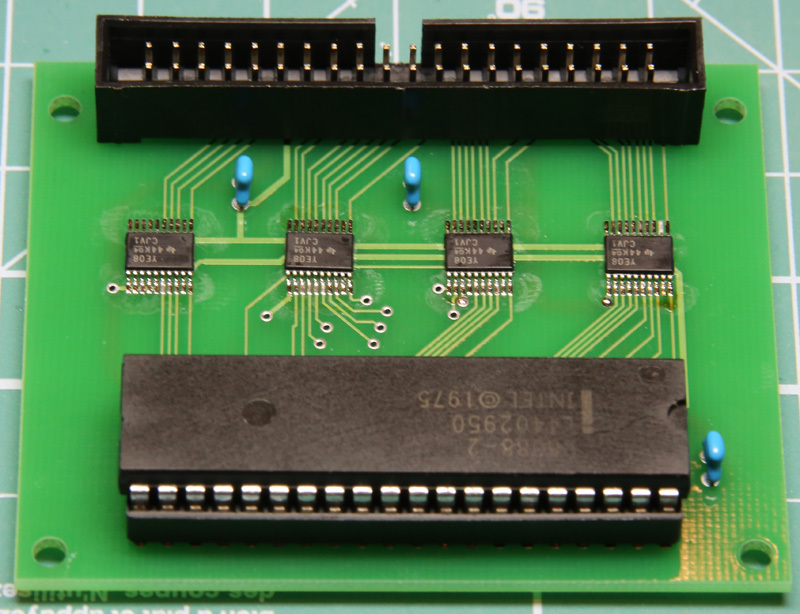

А тут помучил пару дней Eagle и на выходе родилось следующее:

Эта конструкция подключается к GPIO разъему отладочной платы от Altera, и дальше можно творить, чего душа пожелает.

Так как это был первый опыт разработки печатной платы, то решил обойтись самым минимумом - процессор (можно вставить как 8086, так и 8088) плюс преобразователи уровней (отладочная плата работает максимум с 3.3В).

Причем преобразователи уровней попробовал новые - в отличие от использованных ранее в плате для 8080, эти не требуют сигнала направления для двунаправленных сигналов, все определяется автоматически. Есть там, правда, из-за этого некоторые ограничения, но в данном случае они роли не играют.

Так как все еще раздумываю насчет среды программирования, то в очередной раз просто помигал светодиодом для проверки работоспособности.

Что дальше - не уверен. Если интерес у меня не начнет плавно угасать (что вполне может быть), то подумаю, в какую сторону двинуться - остальное все внутри FPGA, или все-таки сделать новую платку с бОльшим количеством корпусов (типа 59, 37 и т.д.).