Попробовал нарисовать схему подключения регистров к шине данных, вроде получилось. http://yadi.sk/d/-4nYjbYf5Voxa

Дальше будет управление регистрами, а потом попробую АЛУ, но там вообще жесть. Или может вас что-то другое в первую очередь интересует?

Moderator: Shaos

А на уровне логических элементов и вентилей это никак не получается?pfgx wrote:Дальше будет управление регистрами, а потом попробую АЛУ, но там вообще жесть.

Или может вас что-то другое в первую очередь интересует?

Пока на уровне логических элементов никак не получается, потому что не понимаю как это работает целиком. Полезно в первую очередь мне самому, в любом виде.Lavr wrote:А на уровне логических элементов и вентилей это никак не получается?

А то ты тратишь время и работу делаешь интересную, но только сколь это полезно кому-либо в виде транзисторов?

Наш Хардыч, помнится, где-то участвовал в аналогичном проекте и они там вроде какpfgx wrote:Пока на уровне логических элементов никак не получается, потому что не понимаю как это работает целиком.

Один разряд: 12 регистров по 4 транзистора на бит плюс 2 на выборку - 72, на чтение-запись ещё 18, итого 90 на разряд. Разрядов 16, 90*16=1440 транзисторов уже "отрисовано"Lavr wrote:Всё же отрисовать 8500 транзисторов - не многовато ли будет?

Слушай, мне вот кажется, что АЛУ потрясающих открытий нам не даст, т.к. мы неплохоpfgx wrote:Дальше будет управление регистрами, а потом попробую АЛУ, но там вообще жесть.

Или может вас что-то другое в первую очередь интересует?

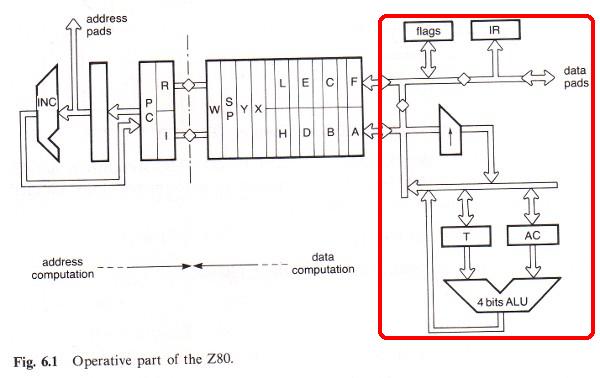

Интересный рисунок. Откуда он? Очень похож, по-моему даже порядок регистров совпадает с кристаллом.Lavr wrote:А вот весь участок, выделенный на рисунке, ты не мог бы срисовать и объяснить?

pfgx wrote:Интересный рисунок. Откуда он? Очень похож, по-моему даже порядок регистров совпадает с кристаллом.

Собственно, видимо, это пока единственный найденный нами печатный источник,Shaos wrote:Вот блок-схема из книжки F. Anceau. The Architecture of Microprocessors. Workingham, England: Addison-Wesley, 1986.

Головы не хватает всё удерживать, я уже стал за собой замечать что и читаю через строчку, особенно когда чем-то занят... чем-то вроде срисовывания схемы микропроцессораShaos wrote:Вот тут обсуждалось же:

Да? А я о другом подумал. У схемы inc/dec чёткая структура, I и R хранятся как 16-битное значение, а блокировку переноса было очень удобно сделать именно в этом разряде, потому что на нём как раз схема ускоренного переноса. Или наоборот, ускоренный перенос сделали в этом разряде, чтобы блокировку добавить? Или просто так совпало?Mixa64 wrote: А что тут думать, DRAM того времени не более 128 усилителей строк имели.