Ну а теперь перейдём к самому "

вкусному", к тому, где нам этот одновибратор понадобится,

а, собственно, это "

вкусное" и было основной причиной того, что я взялся воплотить этот

совершенно не нужный мне проект с процессором

КР1810ВМ86.

Скажем так, что ситуация это довольно частая - собрали проект на каком-либо процессоре,

хочется попробовать его работу, но тут надо "

прошить" ПЗУ, а "

прошивать" в ПЗУ пока ещё

и нечего, а у кого-то и "

прошивалки" нет, а, может быть, и ПЗУ подходящей нет...

В этом случае и может оказаться полезным способ, который здесь на форуме как-то обсуждали,

но никто не решился его воплотить. А способ мне понравился, и я решил его в значительной мере

улучшить, чтобы он не нуждался ни в каких дополнительных переключениях, а работал в качестве

"

эмулятора ПЗУ", хотя и с некотороми ограничениями.

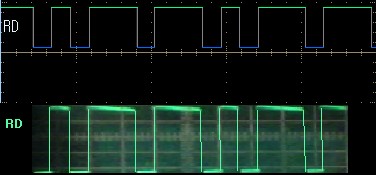

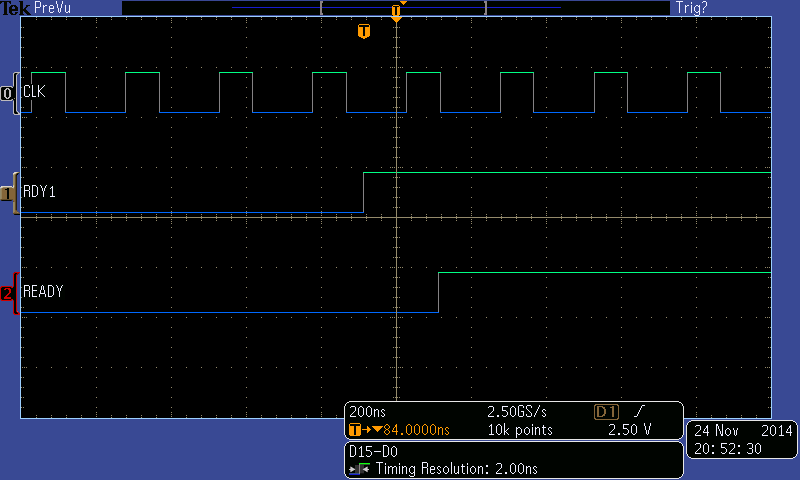

Основная идея следующая: раз уж у нас есть схема пошагового режима, управляемая кнопкой

STEP,

и мы можем выполнять коды, выставляемые резисторами на шине данных, то почему бы не поручить

эту операцию выполнять параллельному порту другого коппьютера?

Всё равно в конструкции таких SBC-поделок обычно закладывается отладочный последовательный

интерфейс, через который идёт обычно загрузка программ пользователя. Но этот интерфейс нуждается

в программной поддержке, а у нас будет загрузка и исполнение кодов безо всякого ПО на плате.

Смотрим принципиальную схему:

Увеличить

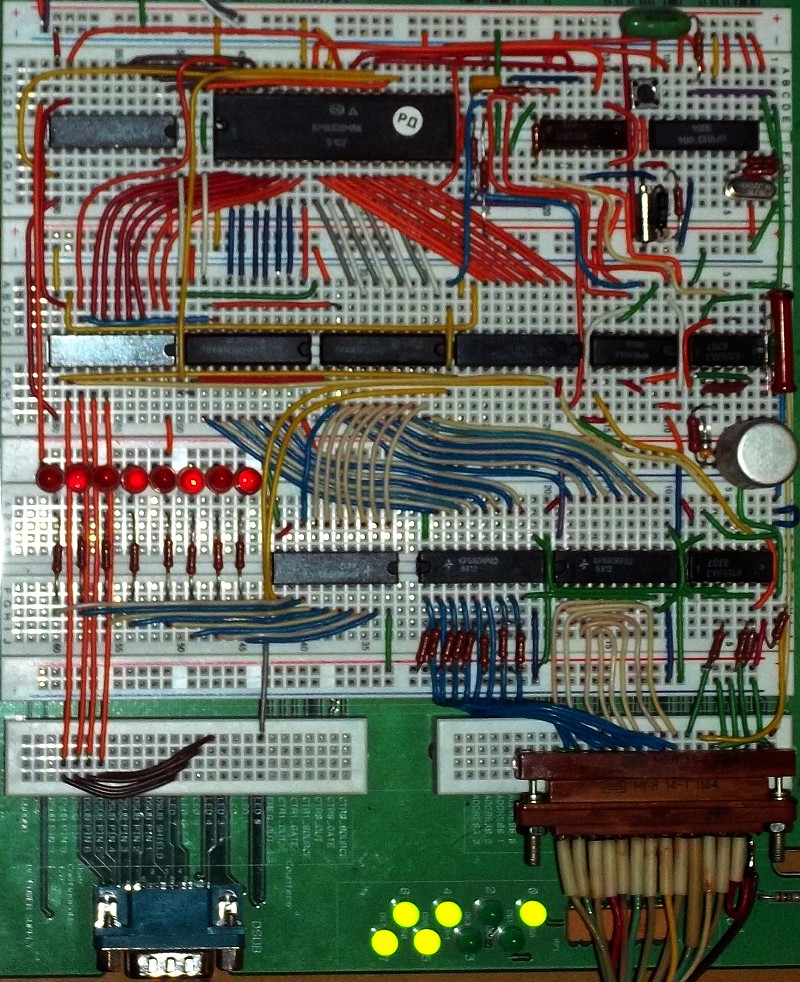

Я ввёл

2 дополнительных регистра типа

580ИР82, которые своими тристабильными выходами подключены

к

шине данных системы, а на входы их

через разряды данных LPT-коннектора можно выдавать байты и

фиксировать их отдельными стробами -

/AUTOF и

/STROBE, соответственно.

После того, как

старший и

младший байты кода операции зафиксированы в регистрах, подается

сигнал INIT в виде

строба низкого уровня, который выводит процессор из

состояния WAIT,

процессор считывает из регистров

2 байта кода, исполняет их, если их достаточно, и снова

обращется к памяти за новым кодом или продолжением предыдущего кода. Этим он снова загоняет

себя в

состояние WAIT, перебросив

RS-триггер, но этот же триггер снимает

активный сигнал

BUSY для

LPT-порта.

Теперь снова можно подать процессору через регистры

младший и

старший байты нового кода, и снова

разрешить его работу

стробом INIT, управляющим через одновибратор пошаговым

RS-триггером.

Вся прелесть решения заключается в том, что я использовал

адресную линию А15 в качестве селектора

адресного пространства в сегменте.

По адресам

8000H-0FFFFH А15 = "1" и эта

логическая "1" пропускает

сигнал /MRD на пошаговый

RS-триггер.

А в диапазоне

0000H-7FFFH процессор этим триггером не тормозится, поскольку

А15 = "0" и

/MRD не

командует триггером, а значит не загоняет себя в

состояние WAIT.

Значит, получается следующая

карта памяти в пределах одного сегмента:

В нижних 32 КБайт можно расположить

ОЗУ, которое будет работать самым обычным образом.

В верхних 32 КБайт процессор натыкается на "

псевдо-ПЗУ" и работает в старт-стопном режиме.

В принципе такую дешифрацию можно изменить, применив дополнительные схемы селекции, но я

был очень ограничен местом на макетке.

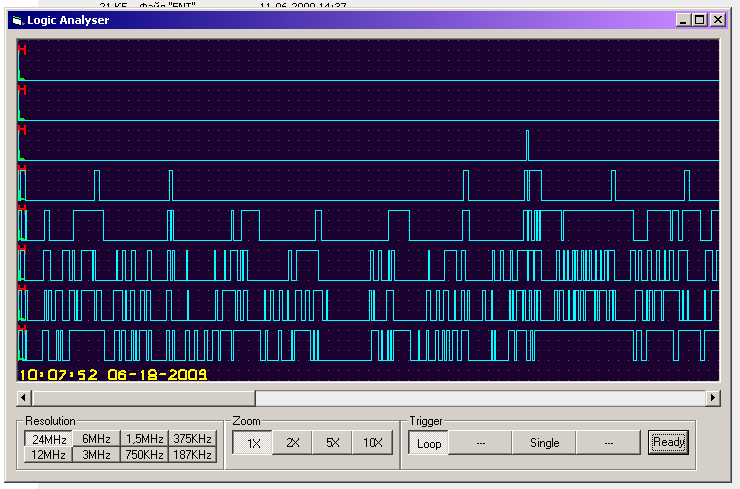

Итак,

процессор КР1810ВМ86 стартует с адреса 0FFF0H в старшем сегменте и там он сразу попадает

в

режим чтения-исполнения команд по интерфейсу LPT, которыми мы можем загрузить программу

в

нижние 32 КБайт ОЗУ и передать на них управление, где программа выполняется самым обычным образом.

Для того, чтобы выполнение команд было как-то визуально заметно, я временно добавил в систему

один единственный

порт вывода на регистре типа

580ИР82, в который мы попадаем

командами OUT

по любому адресу из 65536 возможных.

На выходе этого порта визуализацию записанных в него данных осуществляют 8 светодиодов.

И тут выяснилась весьма интересная и забавная вещь, что сконструированная мной система и безо

всякого ОЗУ позволяет выполнять программы, хотя и с некоторыми ограничениями, но позволяющие

вынести суждение об исправности уже собранной микропроцессорной системы.

Но о программах я расскажу далее...