Читай далее:Lavr wrote:А поподробней насчет "с 3-битным числом которые не используют входной флаг C" - а то как-тоShaos wrote:A=A+1 и A=A-1 (это ADI и SBI с 3-битным числом которые не используют входной флаг C)

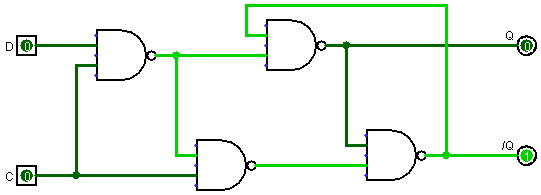

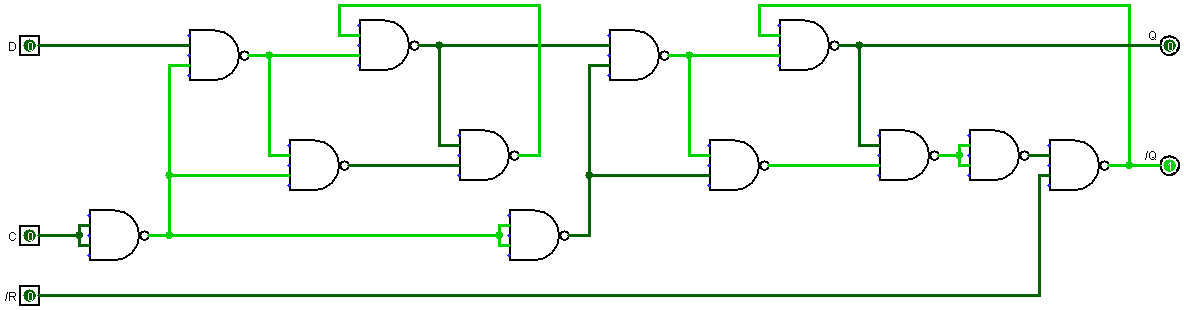

не совсем понятно в рамках твоей системы команд АЛУ:ADC: сложение A с регистром и C - младший ниббл, затем старший ниббл

SBC: сложение A с инвертированным регистром и C - младший ниббл, затем старший ниббл

Это про вот это:A=A+N и A=A-N: детектируется как одно и тоже - сложение A с числом без учёта C

Code: Select all

---------------------------------------------------------------------------------------------------

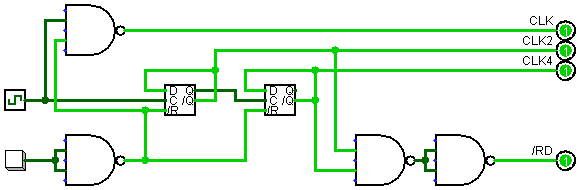

Fx|A=A+0|A=A+1|A=A+2|A=A+3|A=A+4|A=A+5|A=A+6|A=A+7|A=A-8|A=A-7|A=A-6|A=A-5|A=A-4|A=A-3|A=A-2|A=A-1|

---------------------------------------------------------------------------------------------------

- сначала складываем млаший ниббл из A и млаший ниббл кода операции, предварительно установив C в 0

- далее складываем старший ниббл из A и 0000 или 1111 в зависимости от бита 3 кода операции (с учётом C от предыдущего шага)

P.S. A=A+0 (ADI 0) может иметь алиас CLC т.к. она сбрасывает флаг C не меняя содержимое регистра A