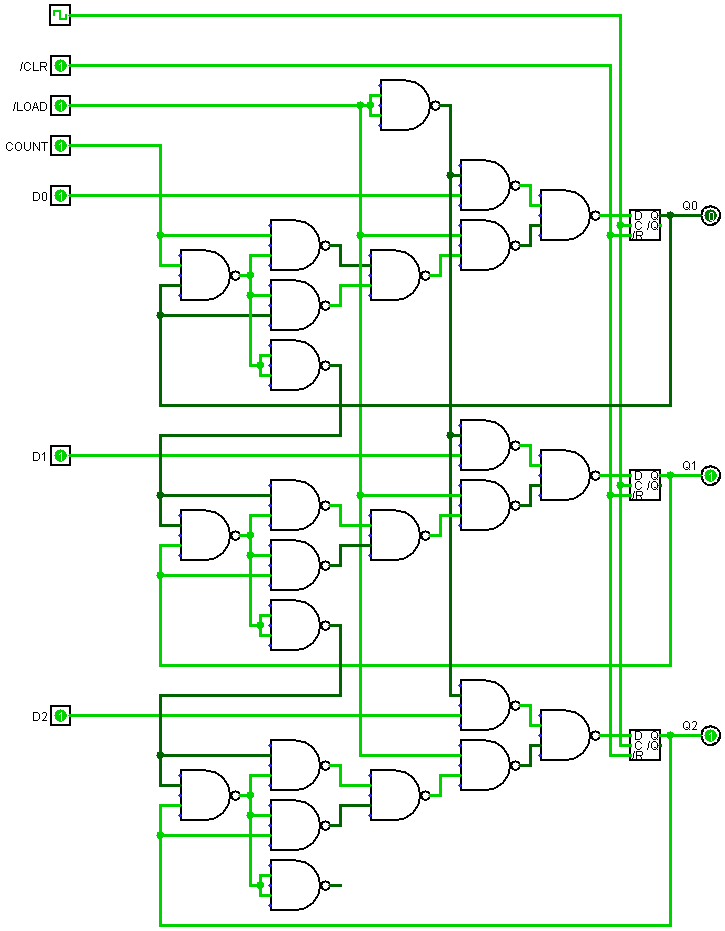

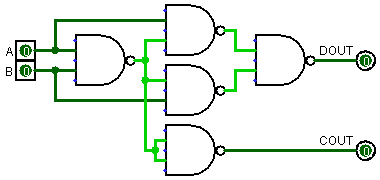

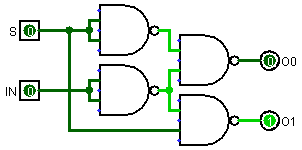

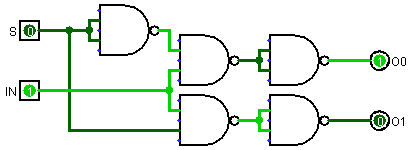

В том то и дело что не совсем... Вот, вроде нашёл как попроще сделать так, чтобы все триггеры меняли состояние одновременно:Lavr wrote:Счетчик-делитель твой должен быть синхронным, как ИЕ7, чтобы не возникли "иголки и всякая другая фигня".Shaos wrote:Осталось проверить в реальности будут ли тут иголки и всякая другая фигня с гонками...

А он у тебя синхронный?

http://vhdlverilog.blogspot.com/2013/07/synchronous-counter-using-d-flipflop.html

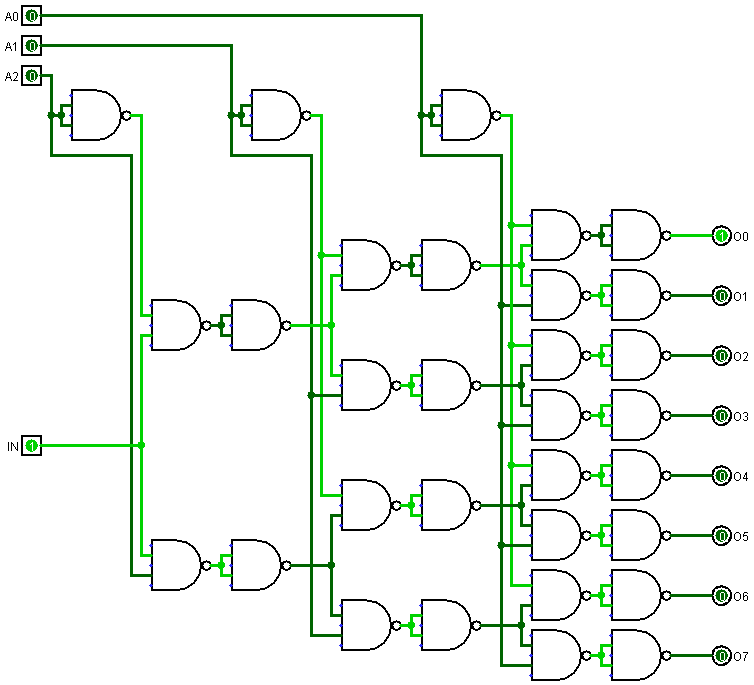

P.S. Похоже это тоже самое, что я для модели своих троичных часов в своё время "изобрёл" - синхронный инкрементатор на полусумматорах

viewtopic.php?f=79&t=60&start=15

viewtopic.php?f=79&t=11076#p119749

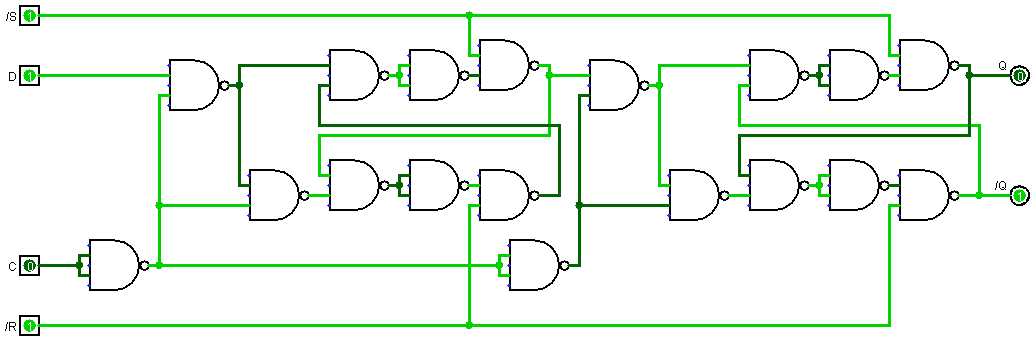

P.P.S. Либо можно попрбовать на JK-триггерах нагородить...

P.P.P.S. Вроде пишут, что если J и K подтянуты к "1", то оно превращается в T-триггер, так что правильнее было бы сказать "на T-триггерах нагородить"...

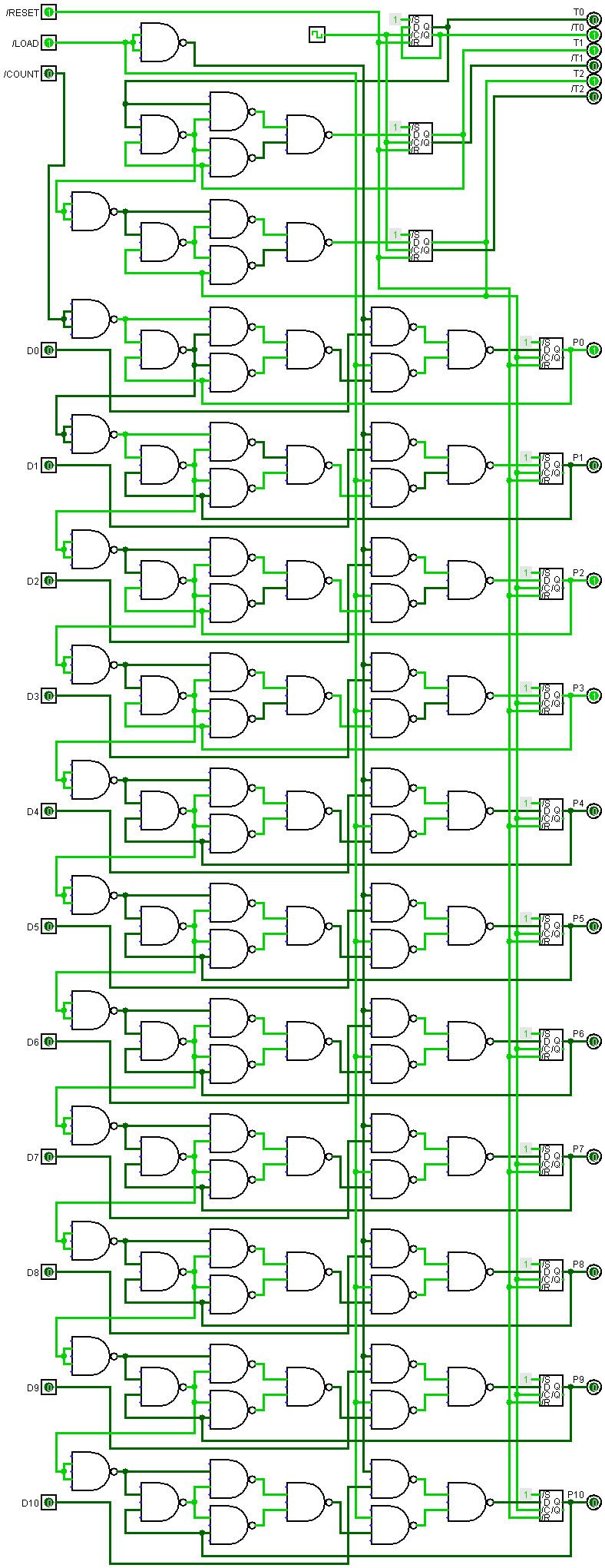

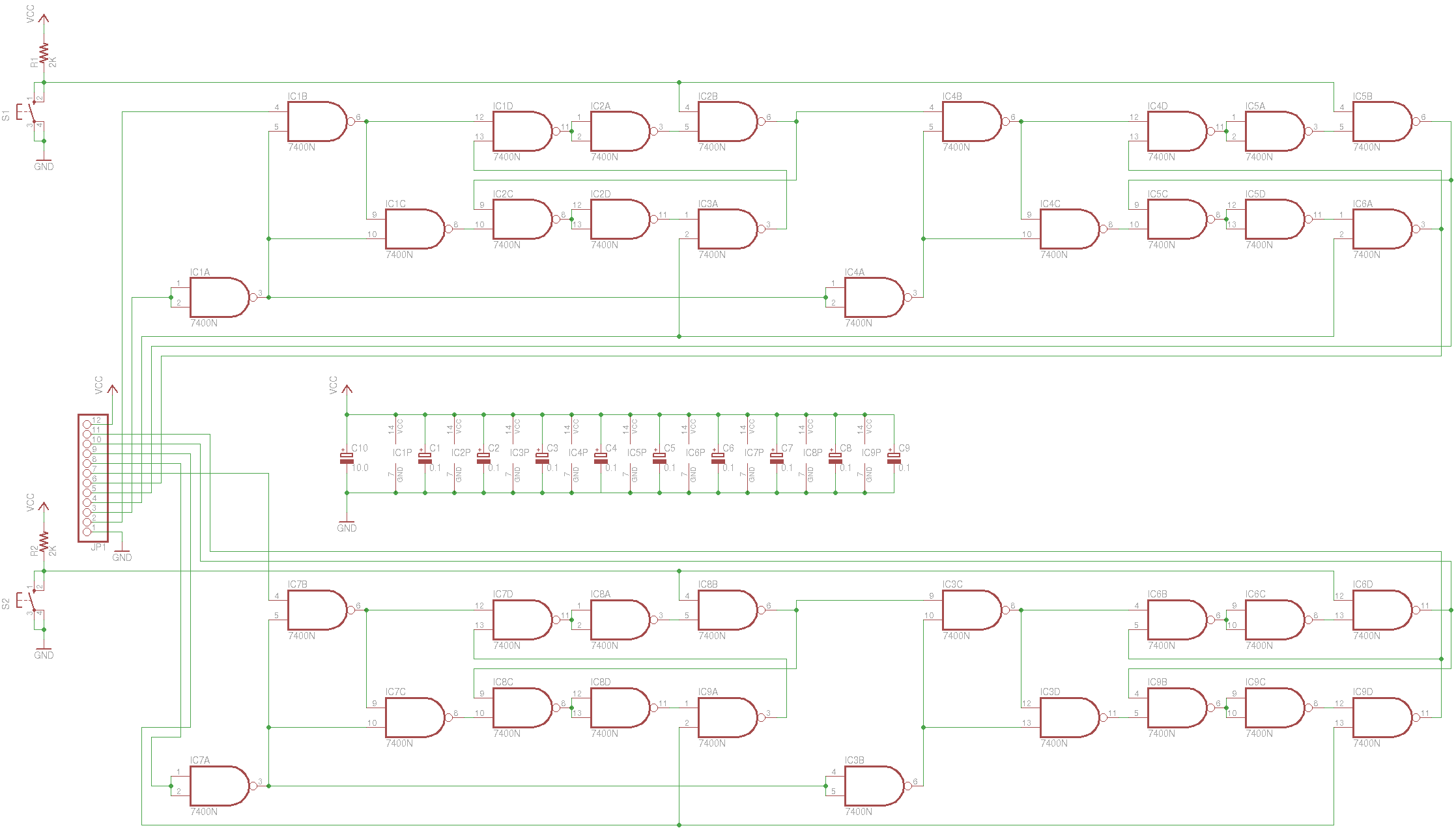

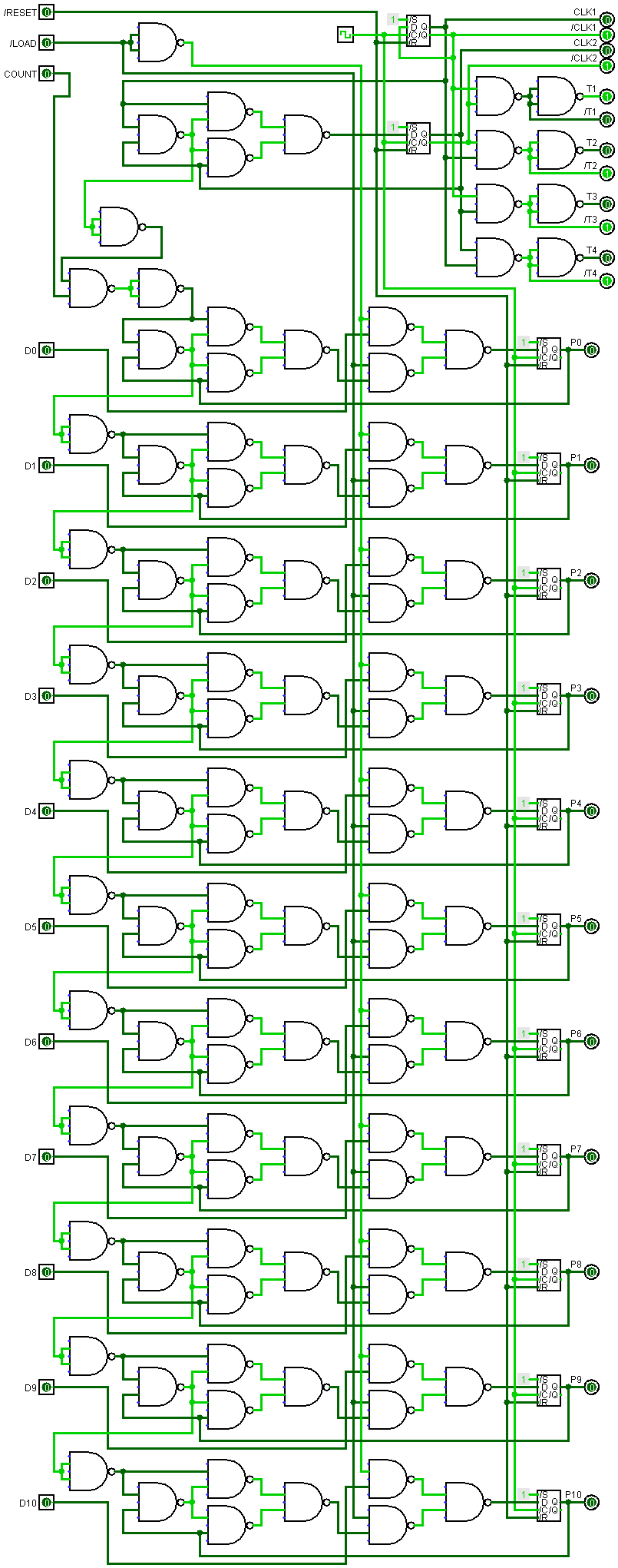

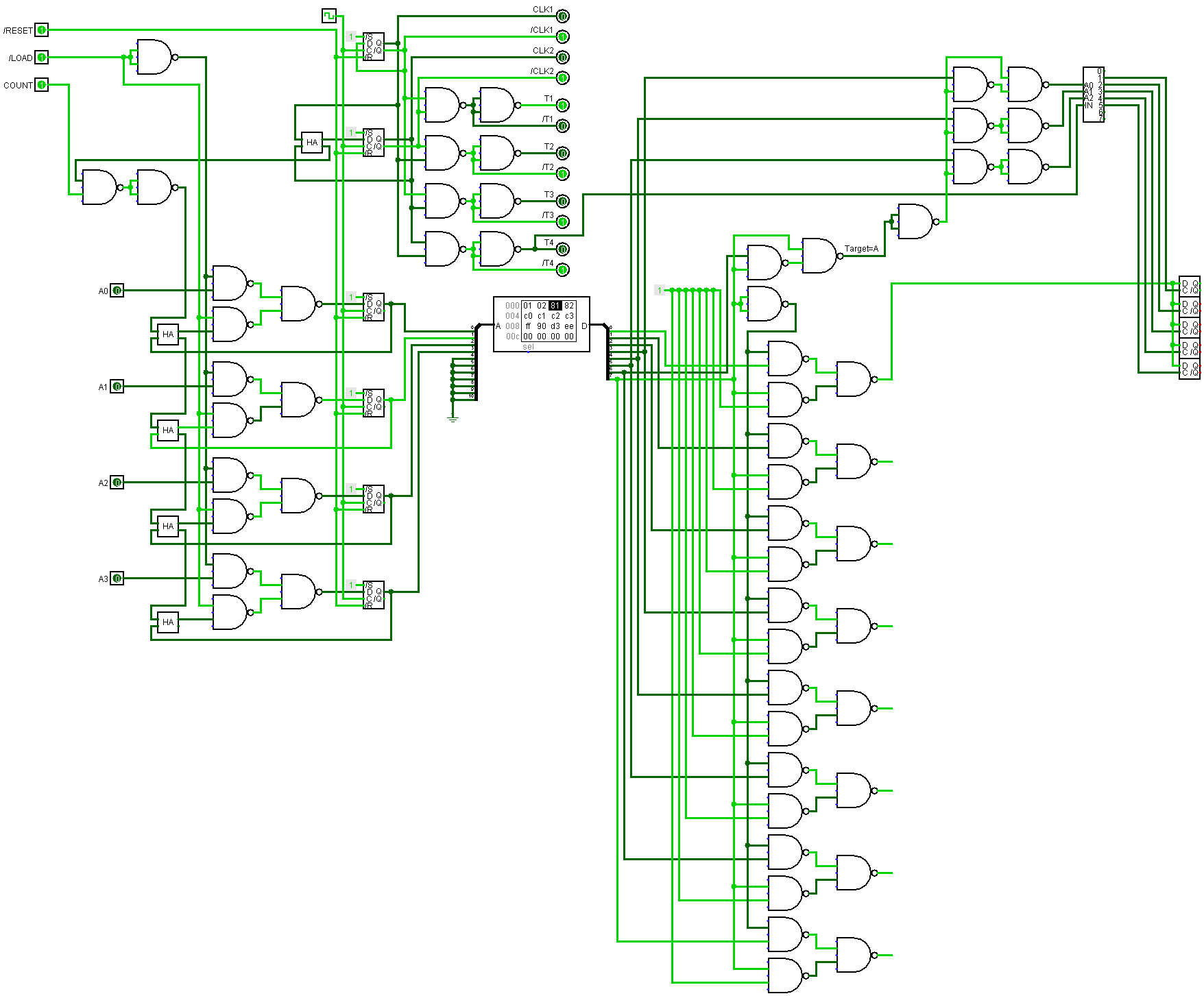

P.P.P.P.S. Согласно ТТЛ-библии ИЕ7 устроено так: