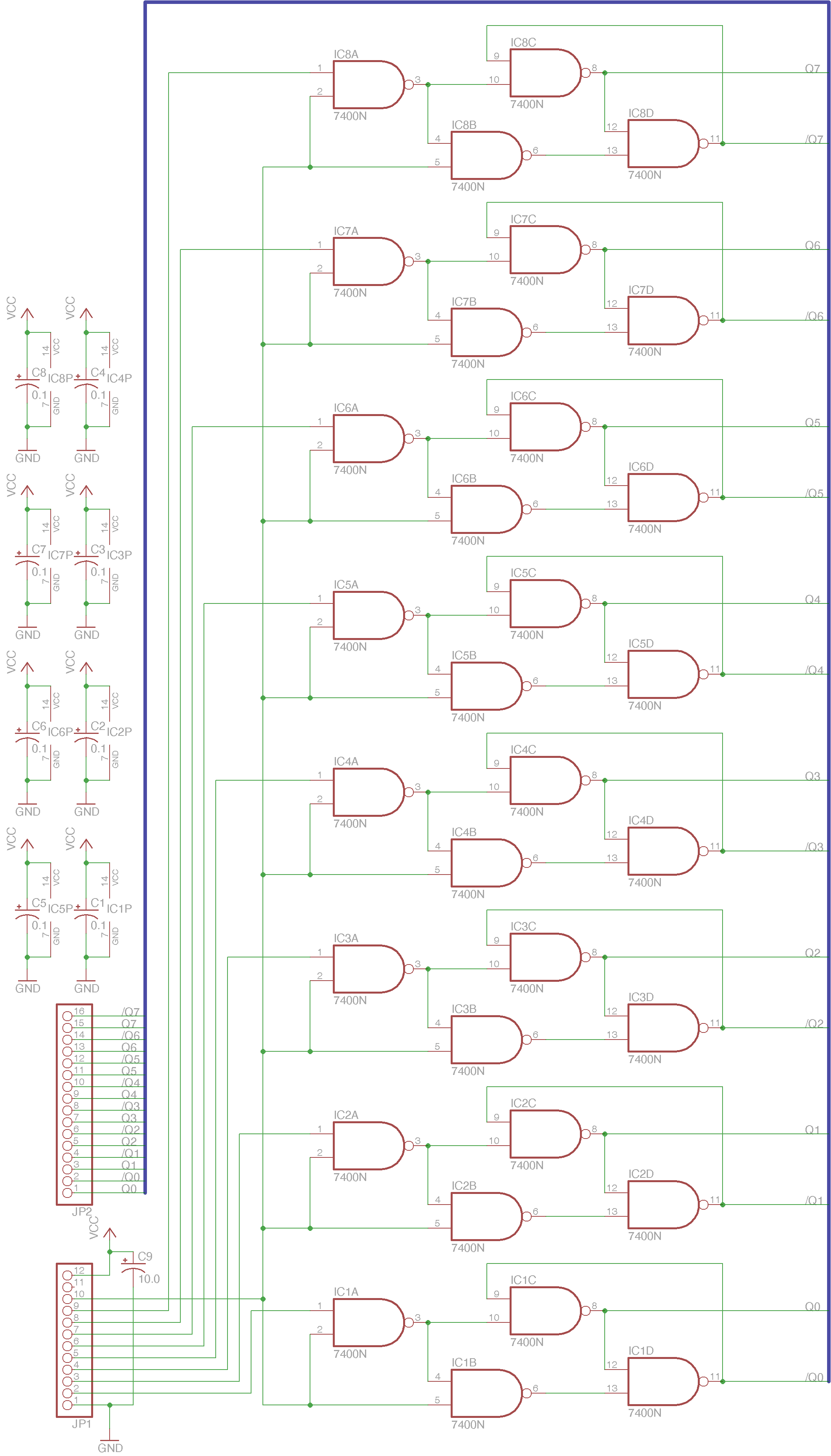

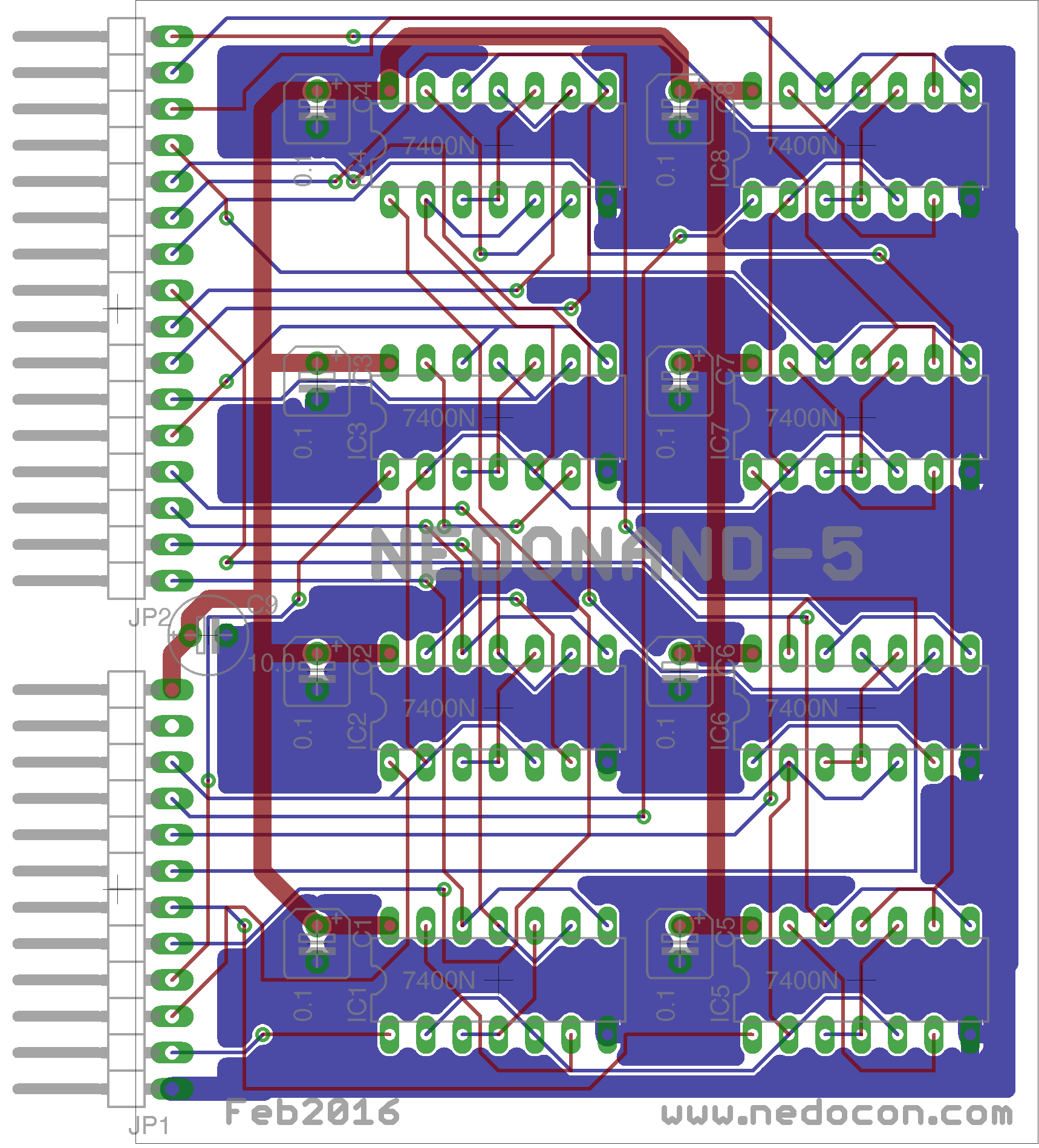

- восьмибитный регистр-защёлка для построения регистров с прямыми и инверсными выходами NEDONAND-5 (2+1+8+16=27 ног);

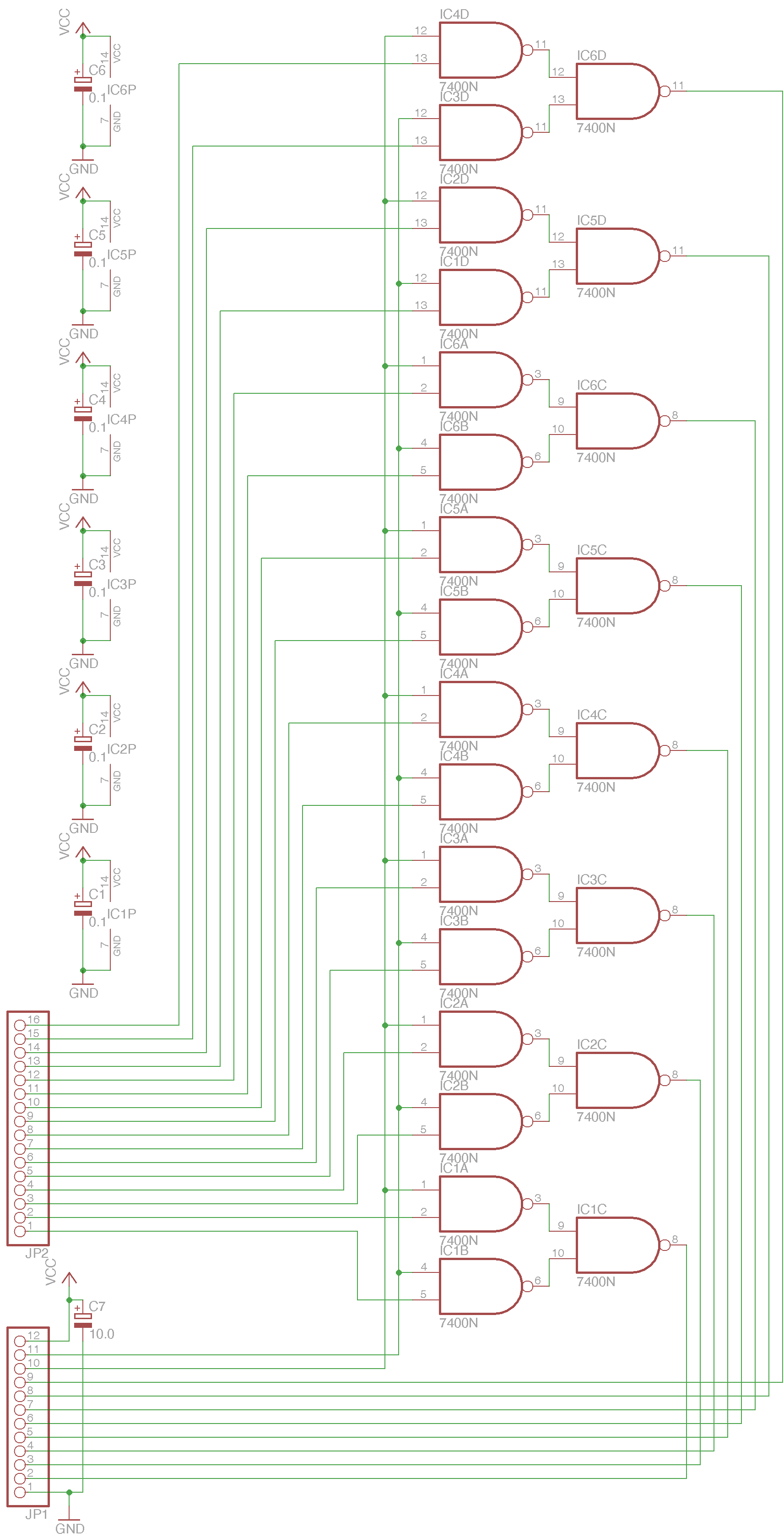

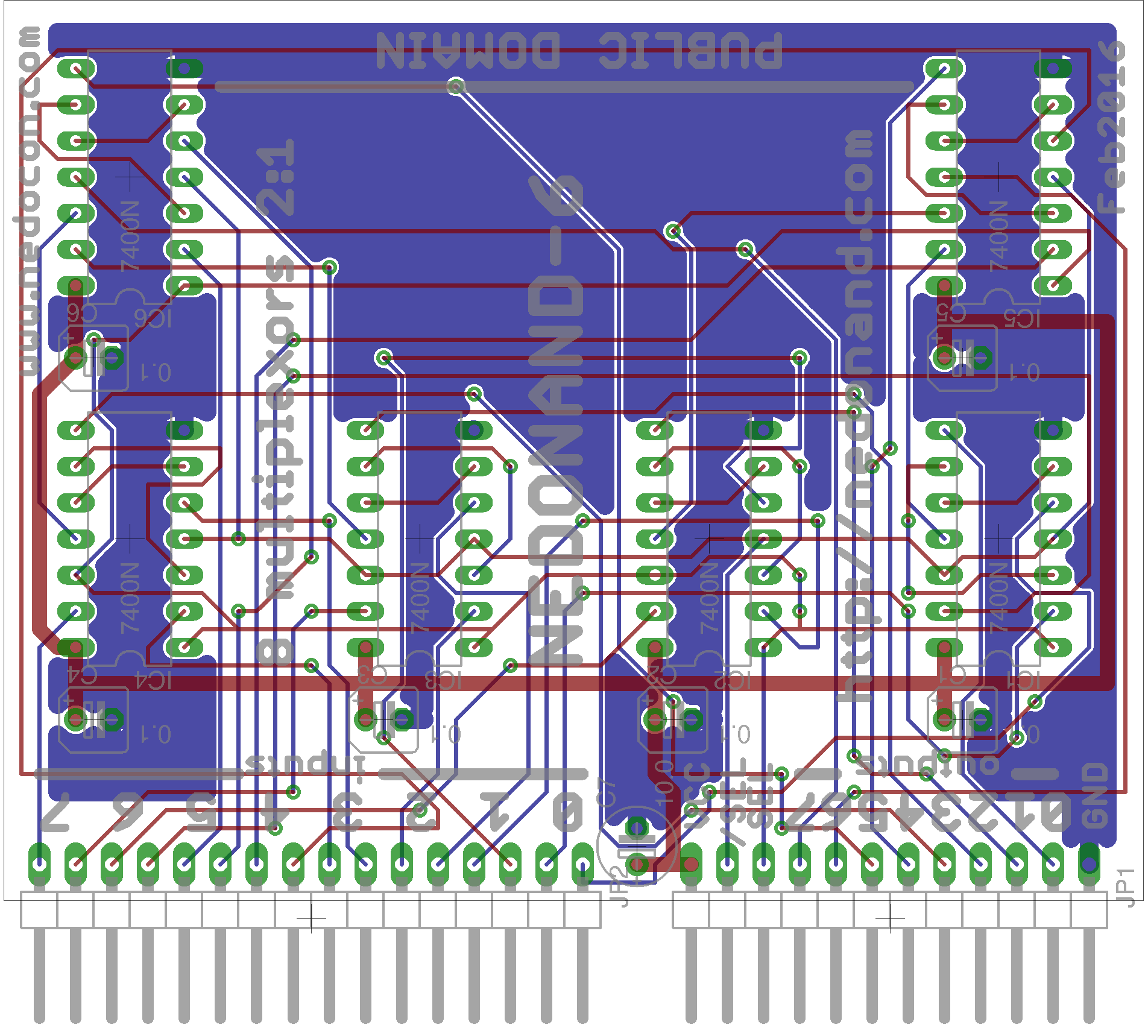

- восемь мультиплексоров 2:1 с общим управлением NEDONAND-6 (2+1+16+8=27 ног);

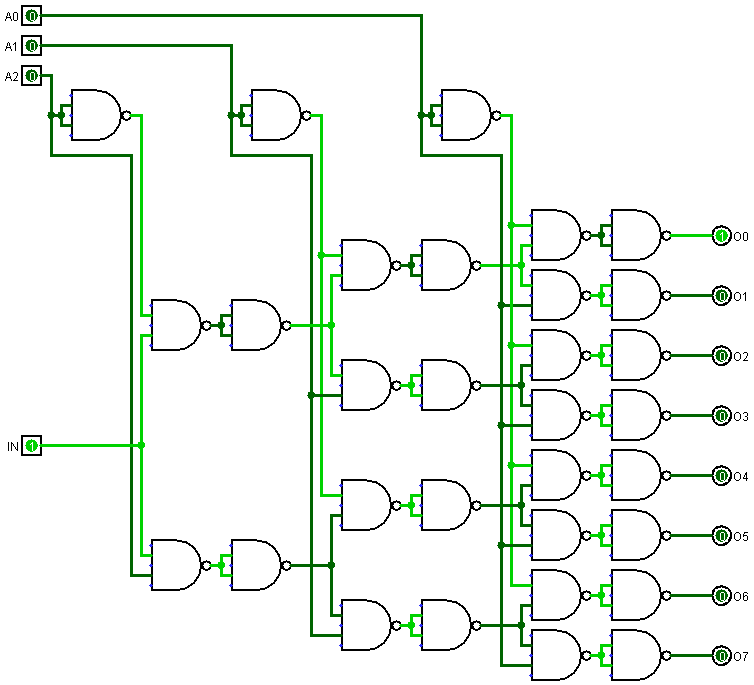

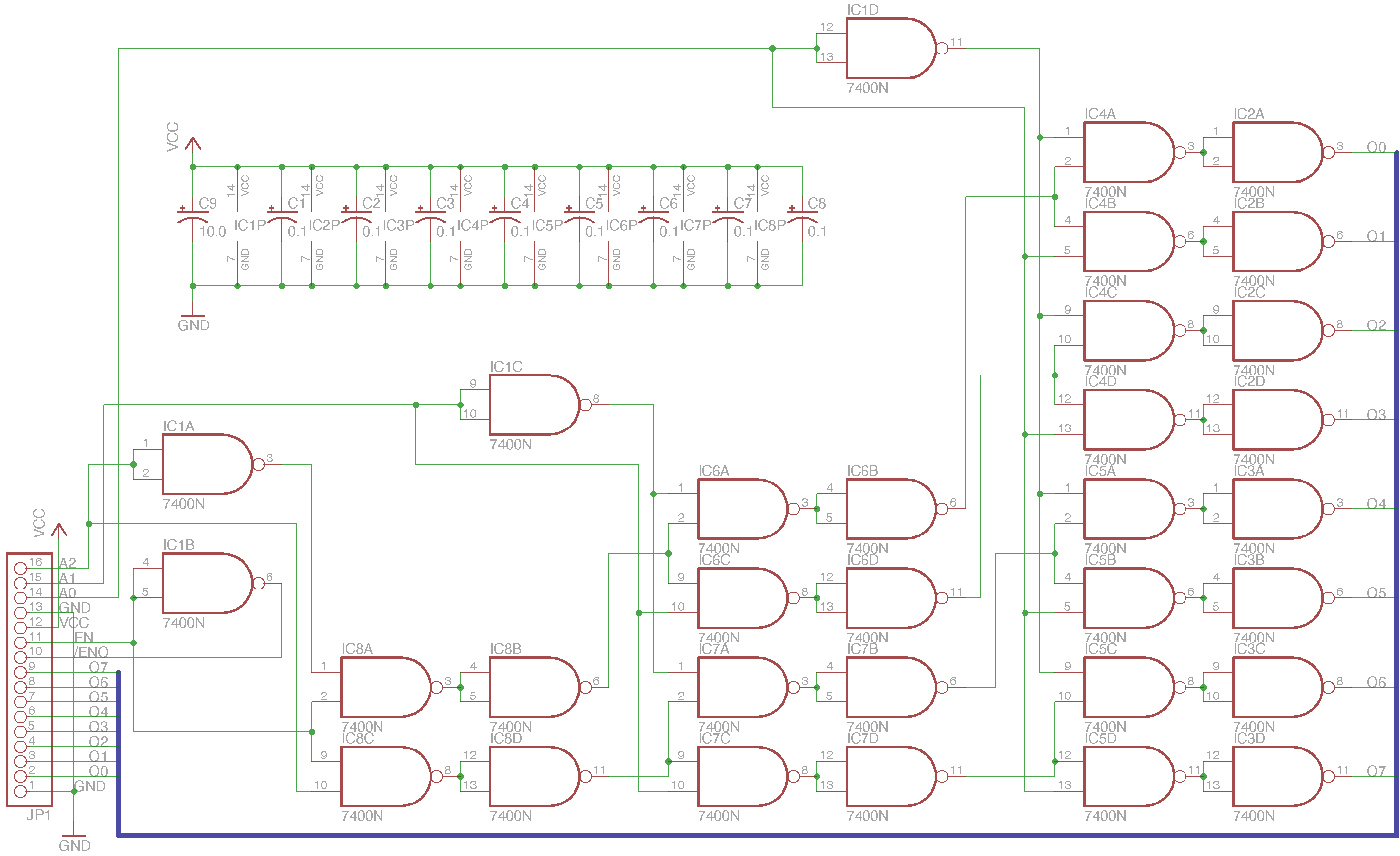

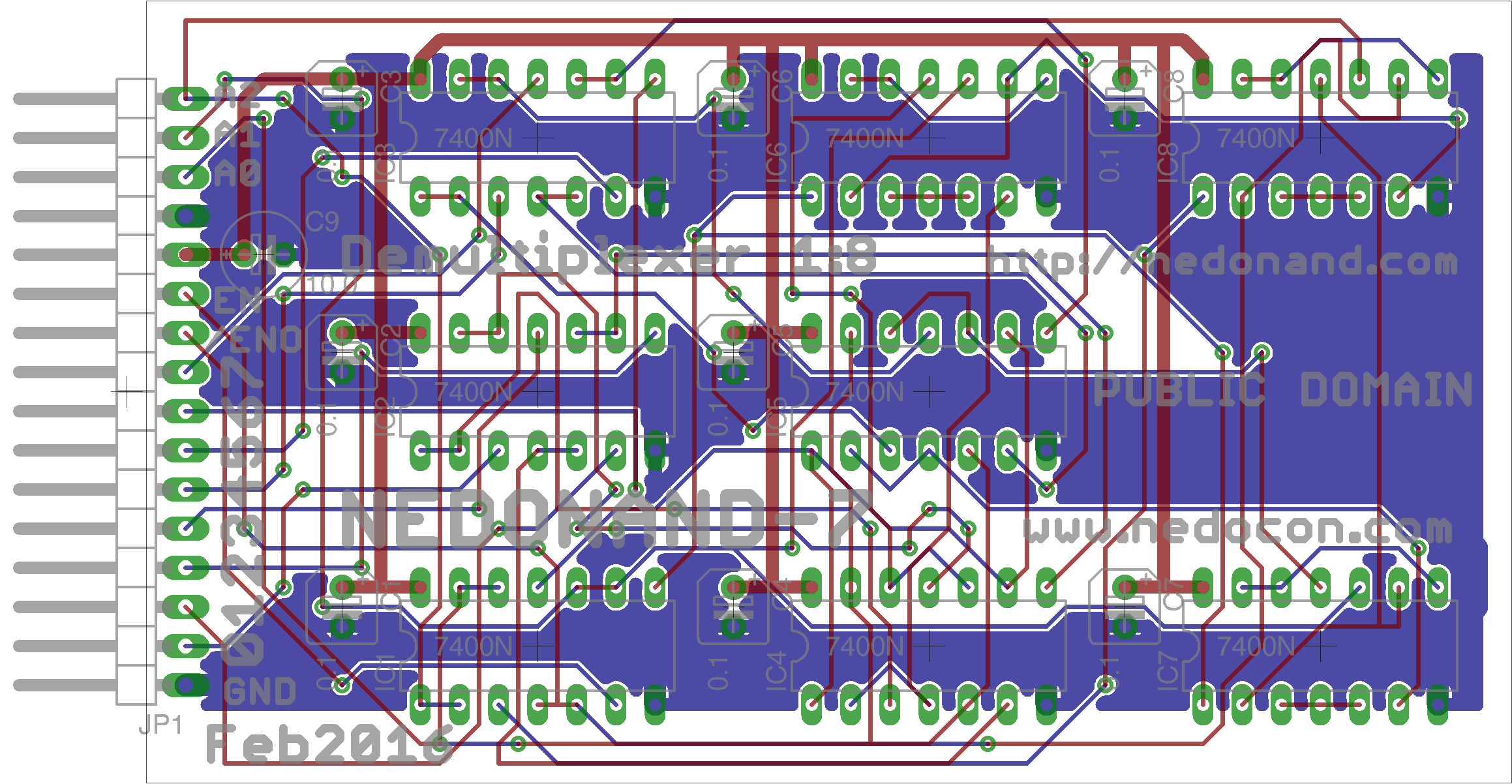

- демультиплексор 1:8 распостраняющий единичку NEDONAND-7 (2+3+1+8=14 ног);

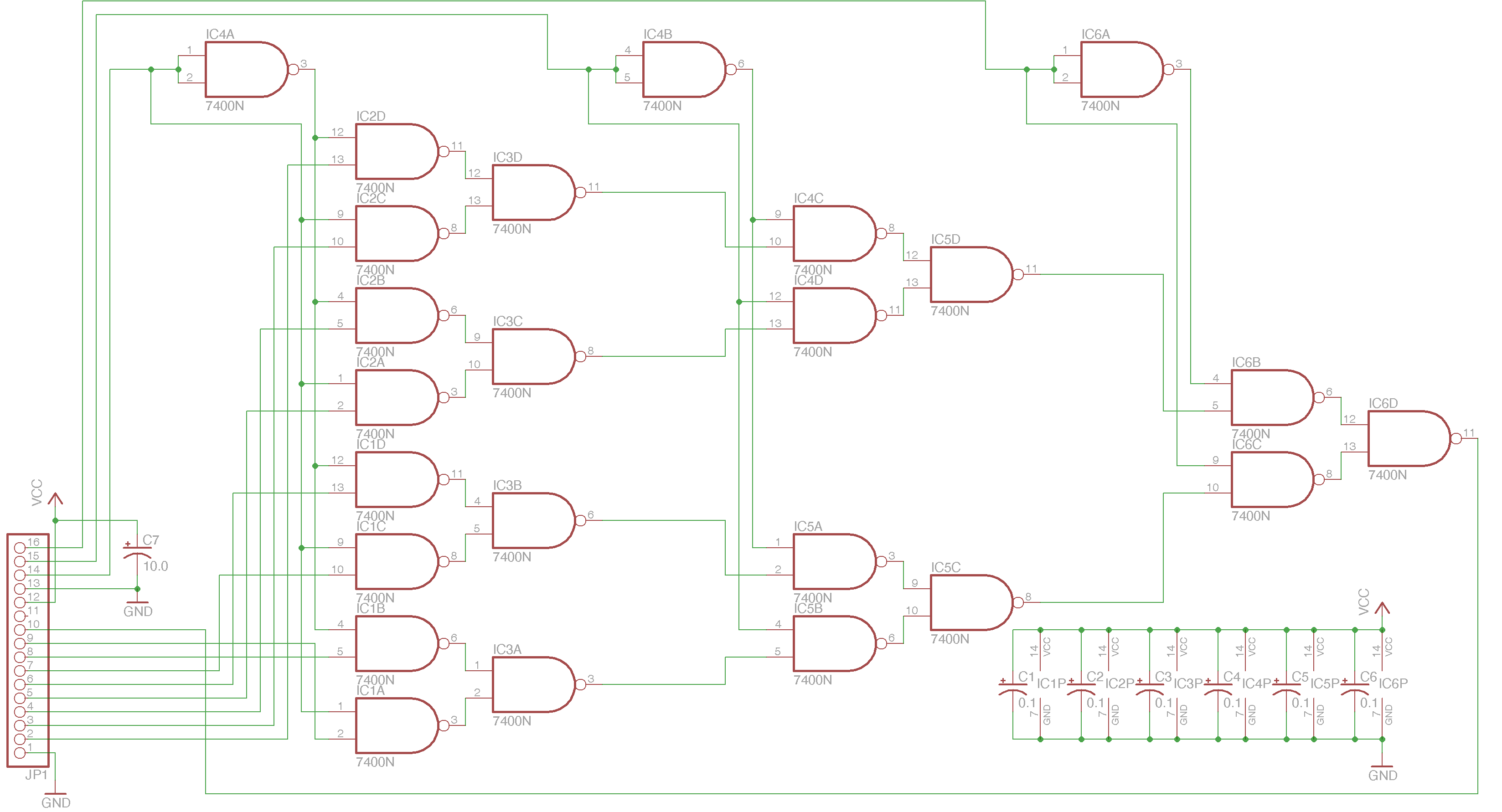

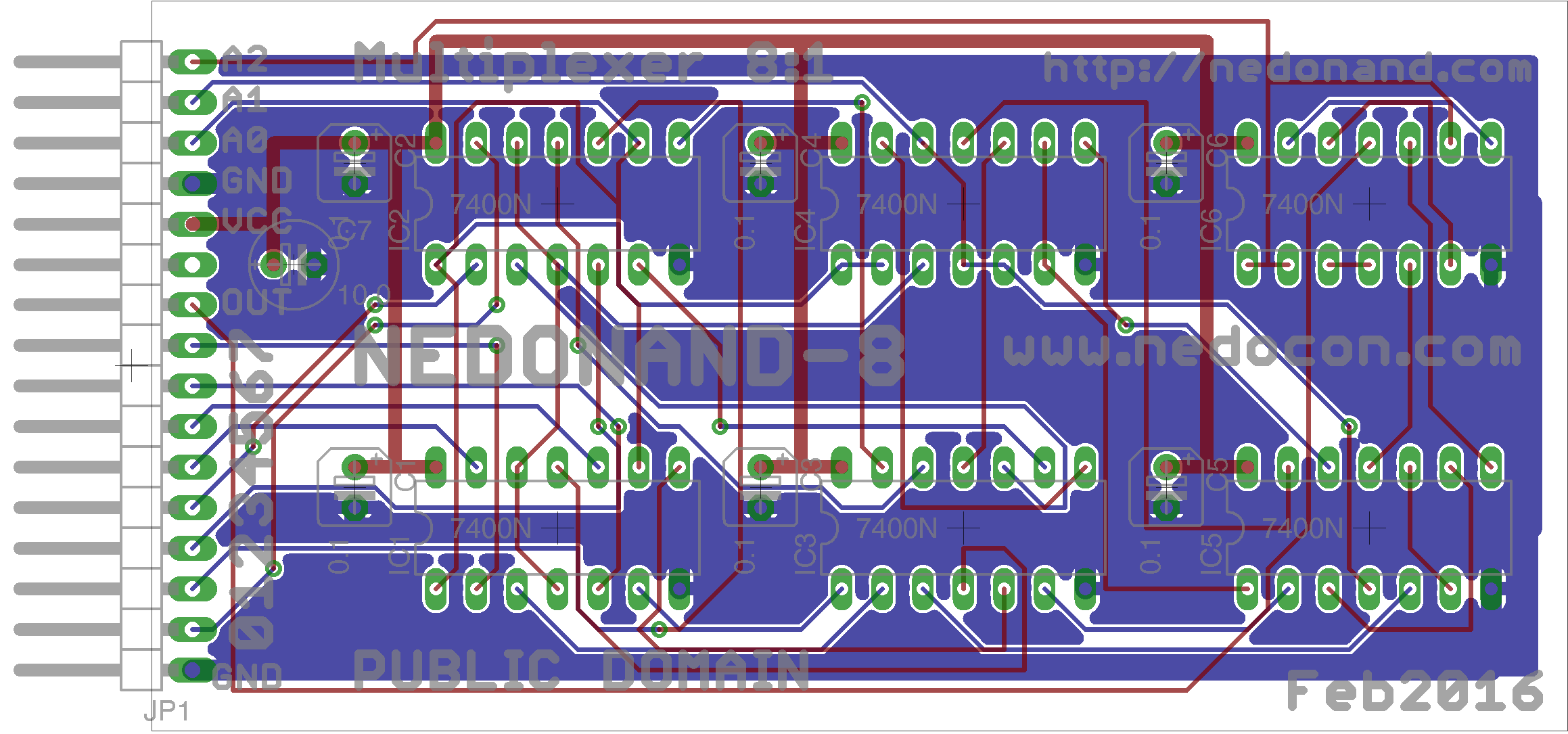

- мультиплексор 8:1 под названием NEDONAND-8 (2+3+8+1=14 ног);

- девятивходовый логический элемент AND под названием NEDONAND-9 (2+9+1=12 ног).

Планирую для начала построить версию которая щас есть в логисиме - только первая ступень конвейера (и только 16 байт ПЗУ).

Далее будет 128-байтовая версия (тоже память на диодах), и только потом полноценная версия с 2К на РФ2.

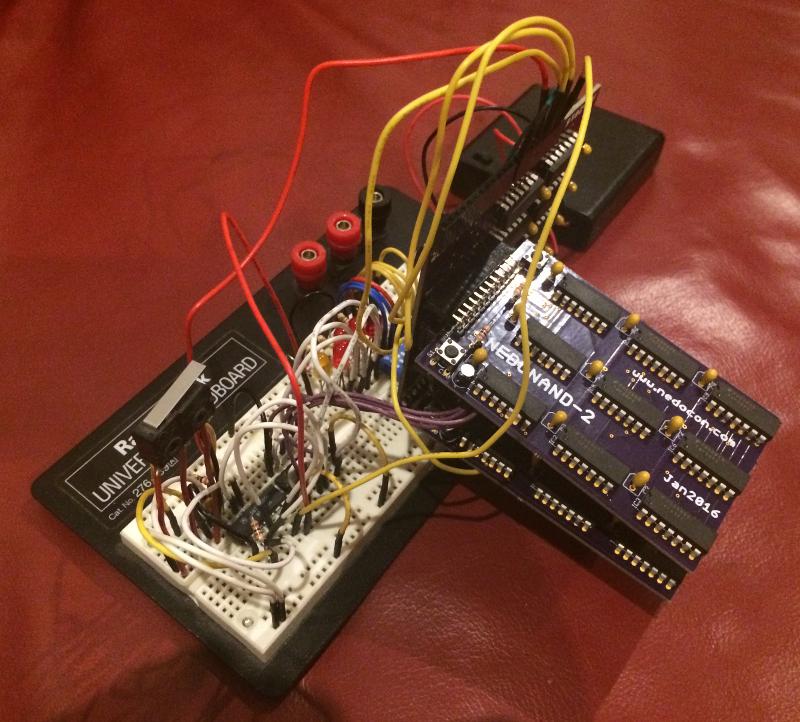

P.S. Вот так их можно тестировать, подключая поочерёдно в один 30-дырчатый разъём, с другой стороны которого будет большой PIC16:

Code: Select all

NN1 NN2 NN3 NN4 NN5 NN6 NN7 NN8 NN9 NN16

--------------------------------------------------------

1) GND GND --- GND GND GND GND GND GND GND

2) O0 D1 ~Q0 D0 D0 O0 O0 I0 A D0

3) O1 ^C1 ~Q1 D1 D1 O1 O1 I1 B D1

4) O2 /R1 ~Q2 D2 D2 O2 O2 I2 C D2

5) A Q1 ~Q3 D3 D3 O3 O3 I3 D D3

6) B /Q1 IN COUT D4 O4 O4 I4 E D4

7) C D2 ACT0 VOUT D5 O5 O5 I5 F D5

8) H ^C2 ACT1 /O0 D6 O6 O6 I6 G D6

9) L /R2 /RESET /O1 D7 O7 O7 I7 H D7

10) COUT Q2 CLK /O2 STB SEL /ENO OUT I NC (/OE)

11) DOUT /Q2 NC /ZERO NC /SEL EN NC AND NC (/CS)

12) VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

13) --- --- GND --- --- --- GND GND --- ---

14) A0 A0 ~A0

15) D0 O0 Q0 A0 A1 A1 ~A1

16) D1 O1 /Q0 B0 A2 A2 ~A2

17) D2 O2 Q1 A1 ~A3

18) D3 C /Q1 B1

19) D4 A0 Q2 A2

20) D5 A1 /Q2 B2

21) D6 A2 Q3 A3

22) D7 A3 /Q3 B3

23) D8 B0 Q4 A4

24) D9 B1 /Q4 B4

25) D10 B2 Q5 A5

26) D11 B3 /Q5 B5

27) Q6 A6

28) /Q6 B6

29) Q7 A7

30) /Q7 B7

P.P.S. Если любую плату NEDONAND повернуть к себе лицом и разъёмом вниз, то ноги будут нумероваться справа-налево...