Самодельный процессор nedoRISC-0 (NEDONAND)

Moderator: Shaos

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Shaos, а проверь на осциллографе, что у тебя там с самой длинной цепью -

сигнал действительно запаздывает, на столько, на сколько ты прикидывал теоретически,

или, может быть, реальный результат лучше?

сигнал действительно запаздывает, на столько, на сколько ты прикидывал теоретически,

или, может быть, реальный результат лучше?

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Я уже почти подобрался к этой задаче - обязательно отпишусь тут (надеюсь что с картинками сигналов), как разберусь вот с этой фиговинойLavr wrote:Shaos, а проверь на осциллографе, что у тебя там с самой длинной цепью -

сигнал действительно запаздывает, на столько, на сколько ты прикидывал теоретически,

или, может быть, реальный результат лучше?

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

У тебя ж вроде нормальный ослик есть... или полосы не хватает?Shaos wrote:обязательно отпишусь тут (надеюсь что с картинками сигналов), как разберусь вот с этой фиговиной

Моя "эта фиговина" попроще вроде, но в действии мне почему-то не понравилась...

"Неживая" какая-то....

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Да есть 2-лучевой 30-МГц старичок, но проблема если разрешение делать мелким, лучей почти не видно будет - до 2 МГц он ничё показывает, а всё что мельче - уже почти неразличимо...

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

А если на ждущей развертке с запуском от исходного сигнала?

Исходный - на первый луч, после задержки - на второй, аккурат задержку и должны увидеть...

Исходный - на первый луч, после задержки - на второй, аккурат задержку и должны увидеть...

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Ну опять же - надо подкручивать разрешение по времени, чтобы была видна задержка - а она менее 200 нс судя по всему (тестю пиком щас и пока на следующем шаге пика АЛУ уже всё посчитал, а это 200 нс в верхнем пределе), что значит надо гнать сигнал раза в два более быстрый чем 5 МГц, т.е. 10, а в 10 луч будет слабенький...Lavr wrote:А если на ждущей развертке с запуском от исходного сигнала?

Исходный - на первый луч, после задержки - на второй, аккурат задержку и должны увидеть...

P.S. Ха, поподавал входные воздействия не подряд, а в разнобой (то 0x00, то 0xFF) и обнаружил, что в некоторых случаях 200 нс недостаточно чтобы АЛУ отработал и зафиксировал значения на выходах, но вот 400 нс похоже достаточно всегда! Выходит, что моя первоначальная оценка "на всём АЛУ - 4*31.5+4*3.5=140 нс (в худшем случае 180+20=200)" оказалась излишне оптимистичной и реальность несколько хуже худшего случая, но мне сейчас важно, чтобы оно не было хуже 300 нс, но проверить я это смогу только с помощью цифрового осциллоскопа...

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Вот программка для nedoCPU-16, которая перебирает все 4096 вариантов входных воздействий для 4-битного АЛУ и фиксирует по 5 значений на выходах со смещением по времени в 200 нс, 600 нс, 1000 нс, 1400 нс и 1800 нс (можно также пересобрать так, чтобы было 400 нс, 800 нс, 1200 нс и т.д. т.е. с первоначальным сдвигом в 200 нс - надо просто раскомментировать nop между записью в PORTB и первым чтением из PORTA):

P.S. Вот пример того, что программа выводит в терминал:

Сначала идёт 12-битный код входного воздействия, а потом 5 шестнадцатиричных значений с выходов со смещением 0.2мкс, 0.6мкс, 1.0мкс, 1.4мкс и 1.8мкс...

P.S. Вот пример того, что программа выводит в терминал:

Code: Select all

16C:00,22,22,22,22

16D:00,22,22,22,22

16E:00,22,22,22,22

16F:02,22,22,22,22

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0

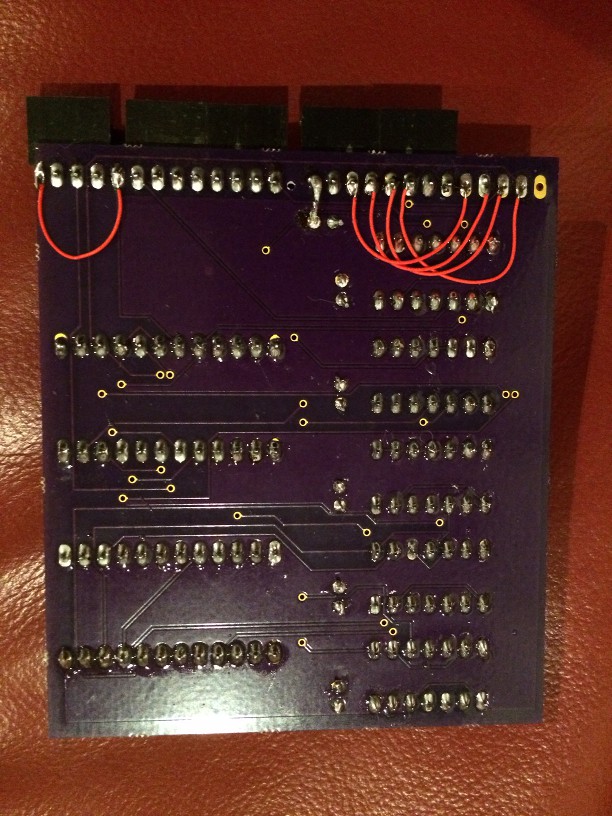

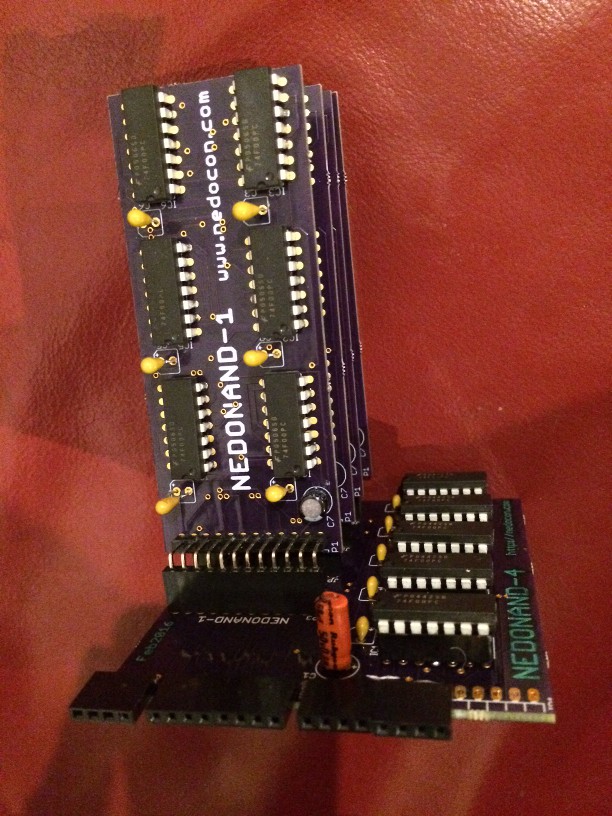

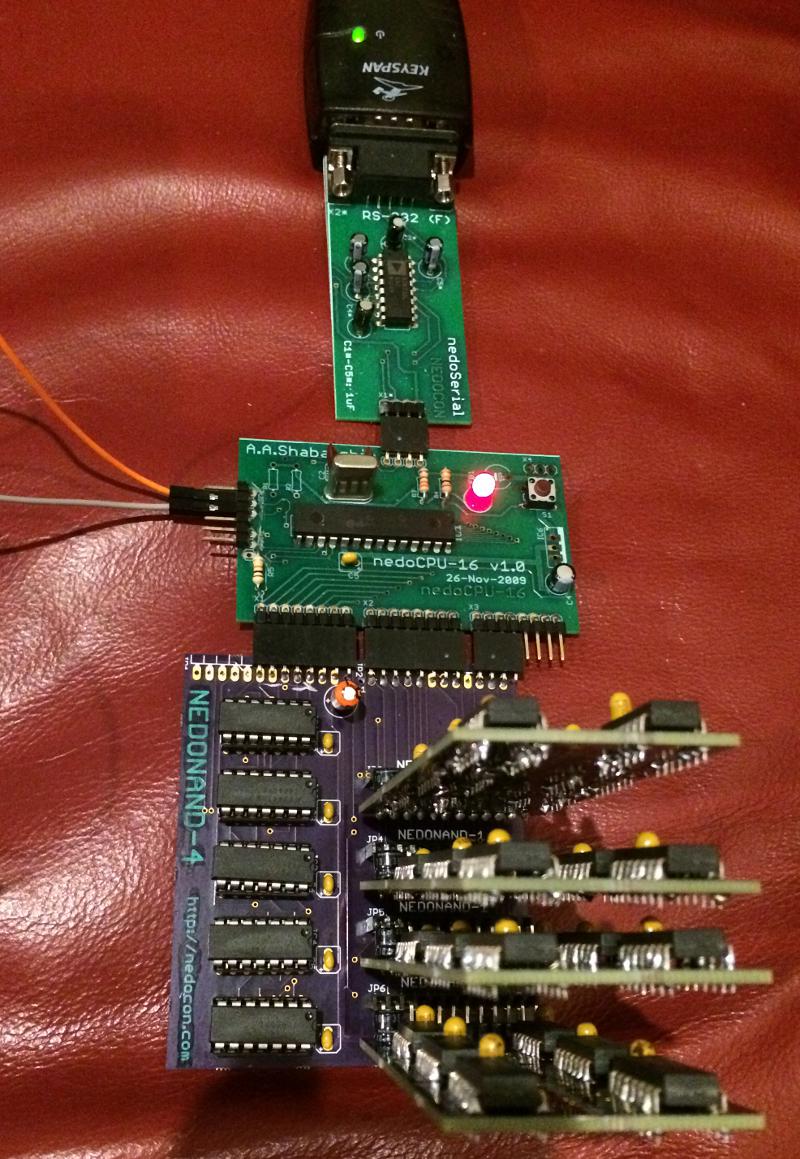

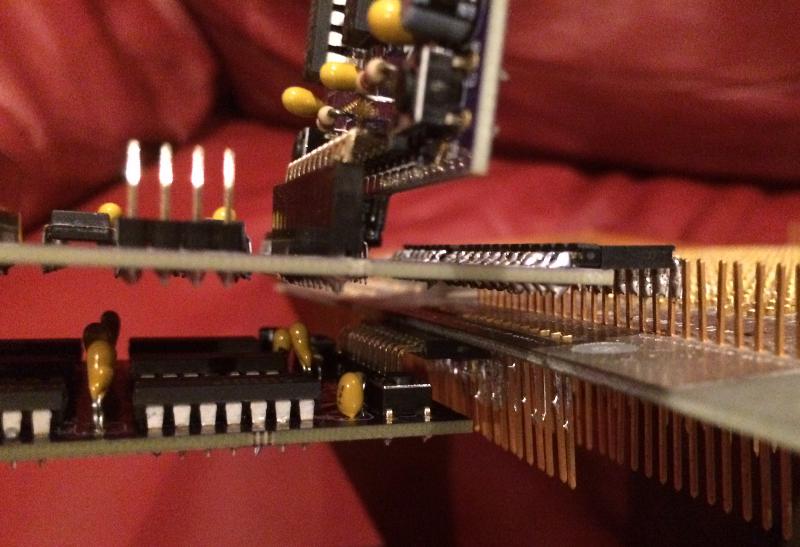

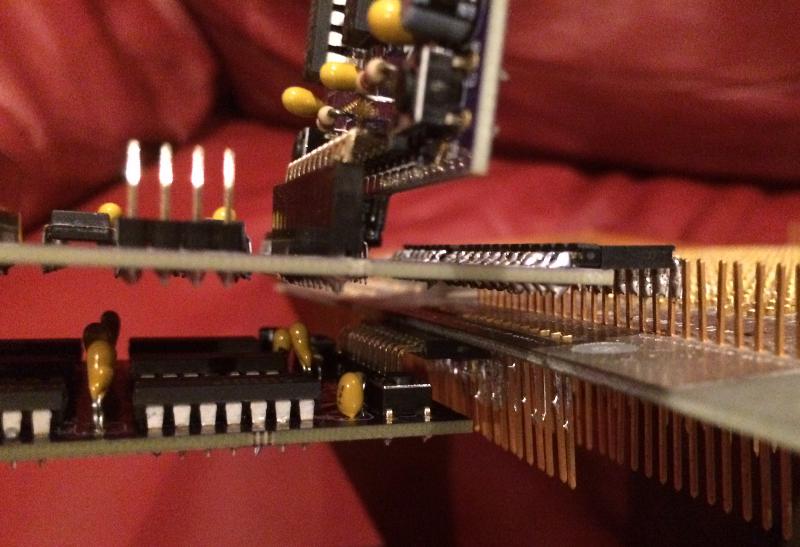

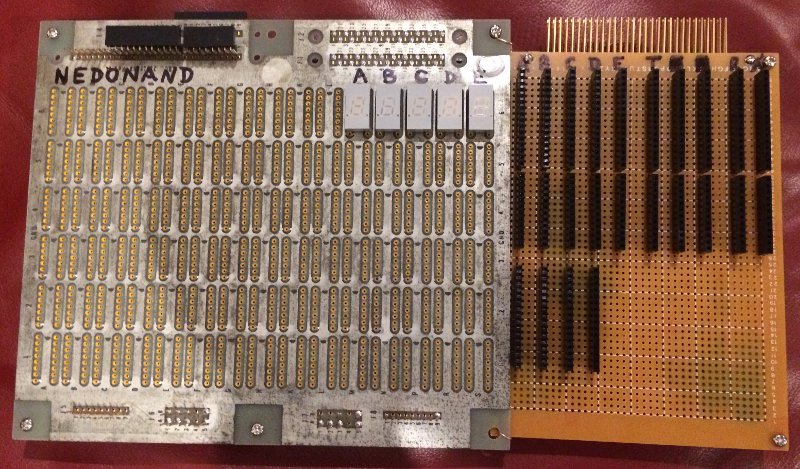

Вот так выглядел процесс тестирования:Shaos wrote:Пришли "неправильные" платки NEDONAND-4, немного подковырял как предполагалось выше:

Собрал тестовый "стэнд" для втыкания в него nedoCPU-16:

Только наверное скорость особо 20-мегагерцовым пиком не померять т.к. он только 5 миллионов команд в секунду делает (это 200 нс)...

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Попробуй еще 0xAA, 0x55 и 0xСС, 0x33 раз уж случилась такая "пьянка"...Shaos wrote:поподавал входные воздействия не подряд, а в разнобой (то 0x00, то 0xFF) и обнаружил, что в некоторых случаях 200 нс недостаточно чтобы АЛУ отработал и зафиксировал значения на выходаха...

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Вобщем написал на сях программку анализирующую лог файл с терминала с 200нс первым отступом и с 400нс первым отступом - в пером случае (200нс) иногда не успевало первый раз, во втором (400нс) - успевало всегда, вот исходник:

Результат работы программки по анализу лога с 4096 записями при первом отступе 200нс:

Как видим не успевает только сложение (ADD) и только самый первый сэмпл [0], напомню, что эта версия АЛУ всегда делает сложение при коде операции 1XX). В большинстве случаев (если не во всех) это неготовность самого старшего бита результата (четвёртого) и/или флагов C/V. Радует, что к моменту 400нс оно всё успевает - надо ещё будет на оциллографе заснять эти задержки, чтобы понять реальный предел (хотелось бы меньше 300нс)...

P.S. Все логи и сырцы лежат на гитхабе: https://github.com/shaos/nedonand/tree/master/tester

Результат работы программки по анализу лога с 4096 записями при первом отступе 200нс:

Code: Select all

ADD 0EC[0] 3F a=-2 b=0 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 0ED[0] 3F a=-2 b=0 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 0EE[0] 3F a=-2 b=0 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 0EF[0] 3F a=-2 b=0 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 16C[0] 00 a=6 b=1 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 16D[0] 00 a=6 b=1 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 16E[0] 00 a=6 b=1 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 16F[0] 02 a=6 b=1 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 1EC[0] 20 a=-2 b=1 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD 1ED[0] 20 a=-2 b=1 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD 1EE[0] 20 a=-2 b=1 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD 1EF[0] 20 a=-2 b=1 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD 24C[0] 3E a=4 b=2 c=1 -> d=7 (15) c=0 (0) v=0 (1)

ADD 24D[0] 3E a=4 b=2 c=1 -> d=7 (15) c=0 (0) v=0 (1)

ADD 24E[0] 3E a=4 b=2 c=1 -> d=7 (15) c=0 (0) v=0 (1)

ADD 24F[0] 3E a=4 b=2 c=1 -> d=7 (15) c=0 (0) v=0 (1)

ADD 2CC[0] 1F a=-4 b=2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 2CD[0] 1F a=-4 b=2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 2CE[0] 1F a=-4 b=2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 2CF[0] 1F a=-4 b=2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 2DC[0] 03 a=-3 b=2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 2DD[0] 03 a=-3 b=2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 2DE[0] 03 a=-3 b=2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 2DF[0] 03 a=-3 b=2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 34C[0] 02 a=4 b=3 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 34D[0] 02 a=4 b=3 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 34E[0] 02 a=4 b=3 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 34F[0] 02 a=4 b=3 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 3CC[0] 20 a=-4 b=3 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD 3CD[0] 22 a=-4 b=3 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 3CE[0] 22 a=-4 b=3 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 3CF[0] 22 a=-4 b=3 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 3D4[0] 03 a=-3 b=3 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 3D5[0] 03 a=-3 b=3 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 3D6[0] 03 a=-3 b=3 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 3D7[0] 03 a=-3 b=3 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 3DC[0] 07 a=-3 b=3 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 3DD[0] 07 a=-3 b=3 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 3DE[0] 07 a=-3 b=3 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 3DF[0] 07 a=-3 b=3 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 485[0] 32 a=-8 b=4 c=0 -> d=-4 (12) c=0 (0) v=0 (1)

ADD 48C[0] 36 a=-8 b=4 c=1 -> d=-3 (13) c=0 (0) v=0 (1)

ADD 48D[0] 36 a=-8 b=4 c=1 -> d=-3 (13) c=0 (0) v=0 (1)

ADD 494[0] 36 a=-7 b=4 c=0 -> d=-3 (13) c=0 (0) v=0 (1)

ADD 49F[0] 3A a=-7 b=4 c=1 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 4A4[0] 3A a=-6 b=4 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 4A5[0] 3A a=-6 b=4 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 4A6[0] 3A a=-6 b=4 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 4A7[0] 3A a=-6 b=4 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 4AC[0] 3D a=-6 b=4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD 4AD[0] 3D a=-6 b=4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD 4AE[0] 3D a=-6 b=4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD 4AF[0] 3D a=-6 b=4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD 4B4[0] 3E a=-5 b=4 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 4B5[0] 3E a=-5 b=4 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 4B6[0] 3E a=-5 b=4 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 52C[0] 00 a=2 b=5 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 52D[0] 00 a=2 b=5 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 52E[0] 00 a=2 b=5 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 52F[0] 00 a=2 b=5 c=1 -> d=8 (0) c=0 (0) v=1 (0)

ADD 584[0] 36 a=-8 b=5 c=0 -> d=-3 (13) c=0 (0) v=0 (1)

ADD 585[0] 36 a=-8 b=5 c=0 -> d=-3 (13) c=0 (0) v=0 (1)

ADD 58F[0] 3A a=-8 b=5 c=1 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 597[0] 3A a=-7 b=5 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 59D[0] 3E a=-7 b=5 c=1 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 59E[0] 3E a=-7 b=5 c=1 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 59F[0] 3E a=-7 b=5 c=1 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 5A4[0] 3E a=-6 b=5 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 5A5[0] 3E a=-6 b=5 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 5A6[0] 3E a=-6 b=5 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 5A7[0] 3E a=-6 b=5 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 5AC[0] 22 a=-6 b=5 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 5AD[0] 22 a=-6 b=5 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 5AE[0] 22 a=-6 b=5 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 5AF[0] 22 a=-6 b=5 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 60C[0] 3C a=0 b=6 c=1 -> d=7 (15) c=0 (0) v=0 (0)

ADD 60D[0] 3C a=0 b=6 c=1 -> d=7 (15) c=0 (0) v=0 (0)

ADD 60E[0] 3C a=0 b=6 c=1 -> d=7 (15) c=0 (0) v=0 (0)

ADD 60F[0] 3C a=0 b=6 c=1 -> d=7 (15) c=0 (0) v=0 (0)

ADD 68C[0] 1F a=-8 b=6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 68D[0] 1F a=-8 b=6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 68E[0] 1F a=-8 b=6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 68F[0] 1F a=-8 b=6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD 69C[0] 03 a=-7 b=6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 69D[0] 03 a=-7 b=6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 69E[0] 03 a=-7 b=6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 69F[0] 03 a=-7 b=6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD 70C[0] 02 a=0 b=7 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 70D[0] 02 a=0 b=7 c=1 -> d=8 (0) c=0 (0) v=1 (1)

ADD 78C[0] 22 a=-8 b=7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 78D[0] 22 a=-8 b=7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 78E[0] 22 a=-8 b=7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 78F[0] 22 a=-8 b=7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 794[0] 03 a=-7 b=7 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 795[0] 03 a=-7 b=7 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 796[0] 03 a=-7 b=7 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 797[0] 03 a=-7 b=7 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD 79C[0] 07 a=-7 b=7 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 79D[0] 07 a=-7 b=7 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 79E[0] 07 a=-7 b=7 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 79F[0] 07 a=-7 b=7 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD 864[0] 3A a=6 b=-8 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 865[0] 3A a=6 b=-8 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD 86C[0] 3F a=6 b=-8 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 86D[0] 3F a=6 b=-8 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 86E[0] 3F a=6 b=-8 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 86F[0] 3F a=6 b=-8 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD 874[0] 3E a=7 b=-8 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 875[0] 3E a=7 b=-8 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 964[0] 3E a=6 b=-7 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 965[0] 3E a=6 b=-7 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 966[0] 3E a=6 b=-7 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 967[0] 3E a=6 b=-7 c=0 -> d=-1 (15) c=0 (0) v=0 (1)

ADD 96C[0] 22 a=6 b=-7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 96D[0] 22 a=6 b=-7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 96E[0] 22 a=6 b=-7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 96F[0] 22 a=6 b=-7 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD 9EC[0] 03 a=-2 b=-7 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD 9ED[0] 03 a=-2 b=-7 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD 9EE[0] 03 a=-2 b=-7 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD 9EF[0] 03 a=-2 b=-7 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD A4C[0] 1F a=4 b=-6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD A4D[0] 1F a=4 b=-6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD A4E[0] 1F a=4 b=-6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD A4F[0] 1F a=4 b=-6 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD A5C[0] 03 a=5 b=-6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD A5D[0] 03 a=5 b=-6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD A5E[0] 03 a=5 b=-6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD A5F[0] 03 a=5 b=-6 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD ACC[0] 3D a=-4 b=-6 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD ACD[0] 3D a=-4 b=-6 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD ACE[0] 3D a=-4 b=-6 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD ACF[0] 3D a=-4 b=-6 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD B4C[0] 20 a=4 b=-5 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD B4D[0] 22 a=4 b=-5 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD B4E[0] 20 a=4 b=-5 c=1 -> d=0 (8) c=1 (0) v=0 (0)

ADD B4F[0] 22 a=4 b=-5 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD B54[0] 03 a=5 b=-5 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD B55[0] 03 a=5 b=-5 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD B56[0] 03 a=5 b=-5 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD B57[0] 03 a=5 b=-5 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD B5C[0] 07 a=5 b=-5 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD B5D[0] 07 a=5 b=-5 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD B5E[0] 07 a=5 b=-5 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD B5F[0] 07 a=5 b=-5 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD BCC[0] 03 a=-4 b=-5 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD BCD[0] 03 a=-4 b=-5 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD BCE[0] 03 a=-4 b=-5 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD BCF[0] 23 a=-4 b=-5 c=1 -> d=-8 (8) c=1 (1) v=0 (1)

ADD C04[0] 33 a=0 b=-4 c=0 -> d=-4 (12) c=0 (1) v=0 (1)

ADD C05[0] 33 a=0 b=-4 c=0 -> d=-4 (12) c=0 (1) v=0 (1)

ADD C06[0] 33 a=0 b=-4 c=0 -> d=-4 (12) c=0 (1) v=0 (1)

ADD C07[0] 33 a=0 b=-4 c=0 -> d=-4 (12) c=0 (1) v=0 (1)

ADD C0C[0] 37 a=0 b=-4 c=1 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C0D[0] 37 a=0 b=-4 c=1 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C0E[0] 36 a=0 b=-4 c=1 -> d=-3 (13) c=0 (0) v=0 (1)

ADD C0F[0] 37 a=0 b=-4 c=1 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C14[0] 37 a=1 b=-4 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C15[0] 37 a=1 b=-4 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C16[0] 37 a=1 b=-4 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C17[0] 37 a=1 b=-4 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD C1C[0] 3B a=1 b=-4 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C1D[0] 3B a=1 b=-4 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C1E[0] 3B a=1 b=-4 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C1F[0] 3B a=1 b=-4 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C24[0] 3B a=2 b=-4 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C25[0] 3B a=2 b=-4 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C26[0] 3B a=2 b=-4 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C27[0] 3B a=2 b=-4 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD C2C[0] 3D a=2 b=-4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD C2D[0] 3D a=2 b=-4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD C2E[0] 3D a=2 b=-4 c=1 -> d=-1 (15) c=0 (1) v=0 (0)

ADD C2F[0] 3F a=2 b=-4 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD C34[0] 3F a=3 b=-4 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD C35[0] 3F a=3 b=-4 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD C36[0] 3F a=3 b=-4 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD C37[0] 3F a=3 b=-4 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D04[0] 37 a=0 b=-3 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD D05[0] 37 a=0 b=-3 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD D06[0] 37 a=0 b=-3 c=0 -> d=-3 (13) c=0 (1) v=0 (1)

ADD D07[0] 36 a=0 b=-3 c=0 -> d=-3 (13) c=0 (0) v=0 (1)

ADD D0C[0] 3B a=0 b=-3 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D0D[0] 3B a=0 b=-3 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D0E[0] 3B a=0 b=-3 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D0F[0] 3B a=0 b=-3 c=1 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D14[0] 3B a=1 b=-3 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D15[0] 3B a=1 b=-3 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D16[0] 3B a=1 b=-3 c=0 -> d=-2 (14) c=0 (1) v=0 (1)

ADD D17[0] 3A a=1 b=-3 c=0 -> d=-2 (14) c=0 (0) v=0 (1)

ADD D1C[0] 3F a=1 b=-3 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D1D[0] 3F a=1 b=-3 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D1E[0] 3F a=1 b=-3 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D1F[0] 3F a=1 b=-3 c=1 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D24[0] 3F a=2 b=-3 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D25[0] 3F a=2 b=-3 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D26[0] 3F a=2 b=-3 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D27[0] 3F a=2 b=-3 c=0 -> d=-1 (15) c=0 (1) v=0 (1)

ADD D2C[0] 23 a=2 b=-3 c=1 -> d=0 (8) c=1 (1) v=0 (1)

ADD D2D[0] 22 a=2 b=-3 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD D2E[0] 22 a=2 b=-3 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD D2F[0] 22 a=2 b=-3 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD DAC[0] 03 a=-6 b=-3 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD DAD[0] 03 a=-6 b=-3 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD DAE[0] 03 a=-6 b=-3 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD DAF[0] 03 a=-6 b=-3 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD E0C[0] 1F a=0 b=-2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD E0D[0] 1F a=0 b=-2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD E0E[0] 1F a=0 b=-2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD E0F[0] 1F a=0 b=-2 c=1 -> d=-1 (7) c=0 (1) v=0 (1)

ADD E1C[0] 03 a=1 b=-2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD E1D[0] 03 a=1 b=-2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD E1E[0] 03 a=1 b=-2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD E1F[0] 03 a=1 b=-2 c=1 -> d=0 (0) c=1 (1) v=0 (1)

ADD E8C[0] 3D a=-8 b=-2 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD E8D[0] 3D a=-8 b=-2 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD E8E[0] 3D a=-8 b=-2 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD E8F[0] 3D a=-8 b=-2 c=1 -> d=-9 (15) c=1 (1) v=1 (0)

ADD F0C[0] 22 a=0 b=-1 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD F0D[0] 22 a=0 b=-1 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD F0E[0] 22 a=0 b=-1 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD F0F[0] 22 a=0 b=-1 c=1 -> d=0 (8) c=1 (0) v=0 (1)

ADD F14[0] 03 a=1 b=-1 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD F15[0] 03 a=1 b=-1 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD F16[0] 03 a=1 b=-1 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD F17[0] 03 a=1 b=-1 c=0 -> d=0 (0) c=1 (1) v=0 (1)

ADD F1C[0] 07 a=1 b=-1 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD F1D[0] 07 a=1 b=-1 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD F1E[0] 07 a=1 b=-1 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD F1F[0] 07 a=1 b=-1 c=1 -> d=1 (1) c=1 (1) v=0 (1)

ADD F8C[0] 03 a=-8 b=-1 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD F8D[0] 03 a=-8 b=-1 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD F8E[0] 03 a=-8 b=-1 c=1 -> d=-8 (0) c=1 (1) v=0 (1)

ADD F8F[0] 23 a=-8 b=-1 c=1 -> d=-8 (8) c=1 (1) v=0 (1)

P.S. Все логи и сырцы лежат на гитхабе: https://github.com/shaos/nedonand/tree/master/tester

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

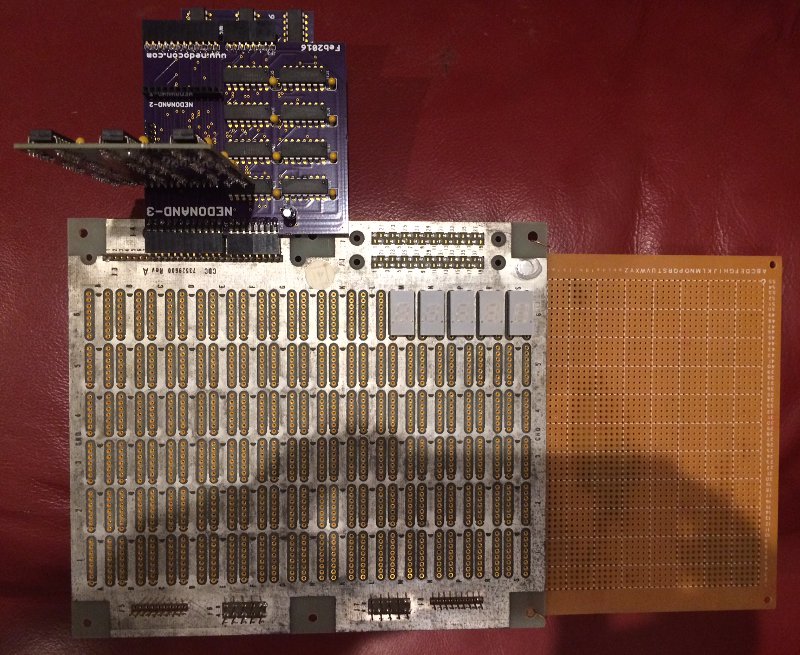

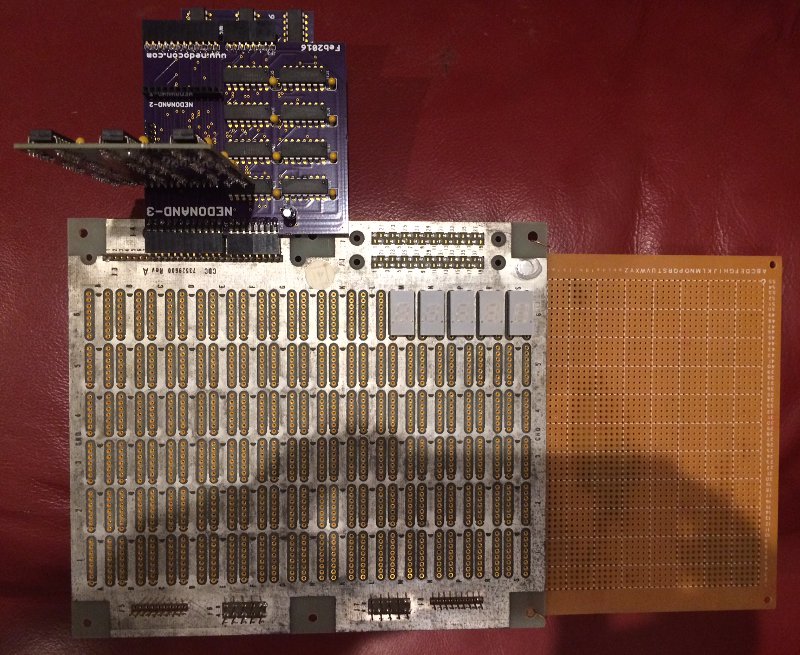

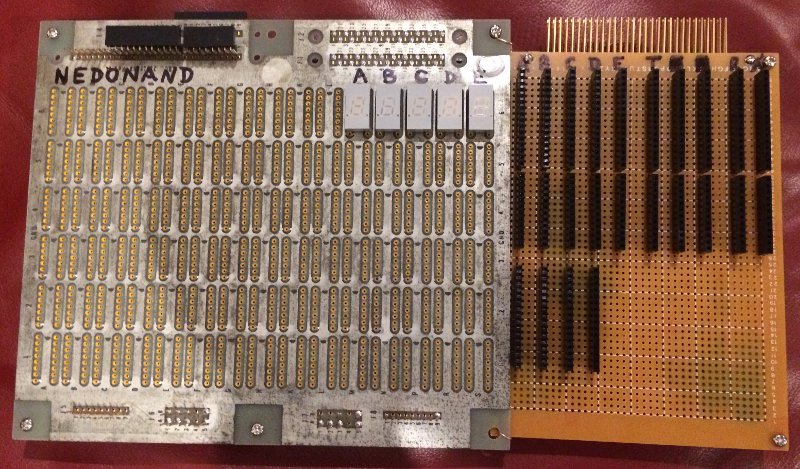

Вобщем решил собирать NEDONAND в виде гибрида - в качестве центральной будет wire-wrap платка поменьше (но с посадочными местами точно под DIP14), к которой приделана макетка куда будут припаяны разъёмы для втыкания вспомогательных платок (таких разъёмов с wire-wrap ногами не выпускают):

Пару разъёмов получилось припаять к самой плате:

Прикинул, что для реализации первой ступени конвейера (и демы "HELLO") мне понадобиться 17 микросхем 74F00 и некоторое количество NEDONAND-платок...

Пару разъёмов получилось припаять к самой плате:

Прикинул, что для реализации первой ступени конвейера (и демы "HELLO") мне понадобиться 17 микросхем 74F00 и некоторое количество NEDONAND-платок...

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Припаял разъёмы для регистров A,B,C,D,E,T, двух мультиплексоров 8x2:1 и ещё 2 регистров R и A' (аргументы ALU) и чуть ниже начал припаивать разъёмы покороче для мультиплексоров 8:1 пока они не закончились. Кроме того прикрутил 60-ногий разъёмчик (справа вверху) на котором будут встречаться припаянные и прикрученные проводки:

Также поставил платку на ножки:

Также поставил платку на ножки:

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Что-то как-то проволоками "на соплях" две платы скрутил...

В "раю для радиолюбителей" не нашлось пары винтов М3 с гайками и шайбочками?

Ну пусть хоть дюймовые, если в "раю" нет М3...

В "раю для радиолюбителей" не нашлось пары винтов М3 с гайками и шайбочками?

Ну пусть хоть дюймовые, если в "раю" нет М3...

iLavr

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Да у них дырки не совпадают, а новые сверлить - неохотаLavr wrote:Что-то как-то проволоками "на соплях" две платы скрутил...

В "раю для радиолюбителей" не нашлось пары винтов М3 с гайками и шайбочками?

Ну пусть хоть дюймовые, если в "раю" нет М3...

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Самодельный процессор nedoRISC-0 (NEDONAND)

Для этого должна быть возможность при копировании регистров выдавать на их вход не только выходы регистра T (временный регистр, используемый при копировании регистров), но и выход АЛУ (который в обычном случае идёт только на вход аккумулятора, причём минуя всё это кольцо через T). Другой вопрос, что если после операции АЛУ идёт не копирование в регистр, а другая операция АЛУ, использующая аккумулятор в качестве аргумента? Например два сдвига подряд - RRC A, RRC A или что-то типа этого. В этом случае при копировании аргументов для второй RRC должен браться не регистр A, а выход АЛУ...Shaos wrote:Не нравятся мне эти дырки между операциями ALU и копированием аккумулятора куда-то. В-принципе, проц может распознать, что следом за командой, требующей ALU, идёт копирование из аккумулятора, и в результате проц может изменить поведение этой команды копирования, чтобы копировать НЕ аккумулятор, а результат работы ALU ! Причём результат ALU надо записать одновременно в 2 регистра - в регистра аккумулятора и в регистр куда аккумулятор скопировали - по идее должно срастись...Shaos wrote:Вот пример инкремента регистровой пары DE:8 циклов, причём только 2 из них используют вторую ступень конвейера, а в остальные 6 (NOP-ы могут быть заменены на другие более полезные команды, не задевающие аккумулятор) АЛУ может быть задействовано для чего-нибудь ещё...Code: Select all

A=E ; no ALU A=A+1 ; used ALU (2nd stage of pipeline) NOP ; no ALU (required because A is not yet ready) E=A ; no ALU A=0 ; no ALU ADC D ; used ALU (2nd stage of pipeline) NOP ; no ALU (required because A is not yet ready) D=A ; no ALU