Пишу только в порт данных, потом задержка 100 мс. Проверил - все ровным счетом то же самое, большинство 0xFF, байта 3 нормальных (из 10ти).newold86 wrote: Повторюсь:

ISA-8 SD-контроллер (SPI) на CPLD

Moderator: Shaos

-

Tronix

- Doomed

- Posts: 662

- Joined: 18 Nov 2013 02:38

- Location: Москва

Re: ISA-8 SD-контроллер (SPI) на CPLD

-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

Таймер запускается все десять раз(в логе видно, клок идёт)

А вот байт не всегда защёлкивается ...хм... во время.

Т.е. Либо поздно либо рано защёлкивается, когда на шине ничего нет.

Скорее всего поздно.

А вот байт не всегда защёлкивается ...хм... во время.

Т.е. Либо поздно либо рано защёлкивается, когда на шине ничего нет.

Скорее всего поздно.

-

Tronix

- Doomed

- Posts: 662

- Joined: 18 Nov 2013 02:38

- Location: Москва

Re: ISA-8 SD-контроллер (SPI) на CPLD

Похоже на то. Менял ради интереса Data[7:0] <= Dat[7:0]; на Data[7:0] <= ~Dat[7:0]; - теперь идут в основном нули и пара-тройка инверсных "хороших" байт. То есть код то работает, но с шины защелкивается 0xFF.

Перемахнул nRD и nWR местами, теперь nWR идет на Ded. input 1 а nRD на обычный пин IO. Результата не принесло.

Тормозная CPLD

Перемахнул nRD и nWR местами, теперь nWR идет на Ded. input 1 а nRD на обычный пин IO. Результата не принесло.

Тормозная CPLD

-

newold86

- Devil

- Posts: 748

- Joined: 30 Nov 2013 11:08

- Location: WWW

Re: ISA-8 SD-контроллер (SPI) на CPLD

Думаю, что ровно наоборот - слишком быстрая. Скорее всего, запись происходит на грани появления/исчезновения какого-то сигнала.Tronix wrote:.Тормозная CPLD

Хотелось бы увидеть остальную схему - декодирование адреса и остальное, если есть что...

-

Tronix

- Doomed

- Posts: 662

- Joined: 18 Nov 2013 02:38

- Location: Москва

Re: ISA-8 SD-контроллер (SPI) на CPLD

Да там схема то... Дешифратор на 1533ИД7:

Не полная конечно дешифрация (не хватает адреса 9), но никто другой в эти порты не ломится на Поиск-2, выход ИД7 подписанный 0x3B0 идет на nCS. Остальные все сигналы (Res, nWR, nRD) сразу в ISA. Clk в OSC. Adr в A0.

PS: Не правильный код верилога на третьей странице я дал, это я игрался с делителем на 64 - не влез он. Поправлю сейчас на актуальный код прям из квартуса, только что прошивал.

Не полная конечно дешифрация (не хватает адреса 9), но никто другой в эти порты не ломится на Поиск-2, выход ИД7 подписанный 0x3B0 идет на nCS. Остальные все сигналы (Res, nWR, nRD) сразу в ISA. Clk в OSC. Adr в A0.

PS: Не правильный код верилога на третьей странице я дал, это я игрался с делителем на 64 - не влез он. Поправлю сейчас на актуальный код прям из квартуса, только что прошивал.

You do not have the required permissions to view the files attached to this post.

-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

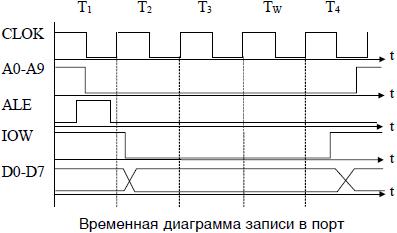

Судя по диаграммам в Гуглах, слишком рано защёлкиваем байт.

-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

попробуй вот этот кусок

Перенести из поседжа в негедж

Как то так чтоли

Code: Select all

// Запись в регистр данных возможна только если SPI не занят

if (~nCS & ~nWR & ~Adr)

begin

Data[7:0] <= Dat[7:0];

BUSY <= 1'b1;

endКак то так чтоли

Code: Select all

always @(negedge Clk) begin

if (~nCS & ~nWR & ~Adr & ~BUSY)

begin

Data[7:0] <= Dat[7:0];

BUSY <= 1'b1;

end

end-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

хотя не уверен.

если верить картинкам, надо защёлкивать на подъёме nWR

если верить картинкам, надо защёлкивать на подъёме nWR

-

Tronix

- Doomed

- Posts: 662

- Joined: 18 Nov 2013 02:38

- Location: Москва

Re: ISA-8 SD-контроллер (SPI) на CPLD

РугаетсяDimkaM wrote:Перенести из поседжа в негедж

Как то так чтоли

Error (10028): Can't resolve multiple constant drivers for net "Data[7]" at XT-sd.v(85)

и тд 13 раз.

-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

Да, я думаю должно сработать, судя по этой картинке:DimkaM wrote:попробуй вот этот кусокПеренести из поседжа в негеджCode: Select all

// Запись в регистр данных возможна только если SPI не занят if (~nCS & ~nWR & ~Adr) begin Data[7:0] <= Dat[7:0]; BUSY <= 1'b1; end

Как то так чтолиCode: Select all

always @(negedge Clk) begin if (~nCS & ~nWR & ~Adr & ~BUSY) begin Data[7:0] <= Dat[7:0]; BUSY <= 1'b1; end end

-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

у тябя так получилось:Tronix wrote: Ругается

Error (10028): Can't resolve multiple constant drivers for net "Data[7]" at XT-sd.v(85)

и тд 13 раз.

Code: Select all

module MX2_CPLD(

// Системные

input Clk, // Входная частота 14.31818 МГц

input Res, // Входной сигнал сброса, активный уровень лог.0

input nRD, // Вход строба чтения

input nWR, // Вход строба записи

input nCS, // Вход выбора контроллера

input Adr, // Вход адреса данные/управление

inout [7:0]Dat, // Шина данных

// SPI

output nSEL, // Выходной сигнал выбора карты

output reg SCK, // Выход тактовой частоты SPI

input MISO, // Вход данных SPI

output MOSI, // Выход данных SPI

output nRED, // Выход управления красным светодиодом

input nINS // Вход датчика вставления карты

);

// Внутренние регистры

reg [4:0]Pre; // Делитель частоты

reg [2:0]Ctrl; // Регистр управления

reg [7:0]Data; // Регистр данных

reg [2:0]Bits; // Счетчик сдвигаемых бит

reg RMISO; // Защелка сигнала MISO

reg BUSY; // SPI занят передачей

// Комбинаторика

assign nSEL = ~Ctrl[0]; // Выбор карты

assign nRED = ~Ctrl[2]; // Красная лампочка

assign MOSI = Data[7]; // Выход MOSI SPI

assign Dat[7:0] = (~nCS & ~nRD) ?

(Adr) ? {~nINS,BUSY,3'h0,Ctrl[2:0]} : Data[7:0]

: 8'hZZ;

// Синхронная логика

always @(posedge Clk) begin

// Делитель частоты

Pre[4:0] <= Pre[4:0] + 5'h1;

// Запись в управление может происходить асинхронно

if (~nCS & ~nWR & Adr) Ctrl[2:0] <= Dat[2:0];

// Сигнал сброса имеет приоритет вне зависимости от выбранной скорости

if (Res)

begin

// Сброс действует на эти регистры

Ctrl[2:0] <= 3'h0;

Bits[2:0] <= 3'h0;

BUSY <= 1'b0;

SCK <= 1'b0;

end else begin

// Состояние SPI

if (BUSY)

begin

// Делитель частоты

if (((Pre[4] & Pre[3] & Pre[2] & Pre[1]) | Ctrl[1]) & Pre[0])

begin

// SPI работает

if (SCK)

begin

// Сбрасываем такт

SCK <= 1'b0;

// Спад, поэтому сдвигаем

Data[7:0] <= {Data[6:0],RMISO};

// Считаем биты

Bits[2:0] <= Bits[2:0] + 3'h1;

// Это был 7й бит?

if (Bits[2] & Bits[1] & Bits[0]) BUSY <= 1'b0;

end else begin

// Устанавливаем такт

SCK <= 1'b1;

// Это фронт, поэтому сэмплируем вход

RMISO <= MISO;

end

end

end else begin

// Обнуляем счетчик бит

Bits[2:0] <= 3'h0;

// Запись в регистр данных возможна только если SPI не занят

end

end

end

always @(negedge Clk) begin

if (~nCS & ~nWR & ~Adr & ~BUSY)

begin

Data[7:0] <= Dat[7:0];

BUSY <= 1'b1;

end

end

// Конец

endmodule-

Tronix

- Doomed

- Posts: 662

- Joined: 18 Nov 2013 02:38

- Location: Москва

-

DimkaM

- Maniac

- Posts: 261

- Joined: 22 Jun 2005 04:35

- Location: МО Россия

Re: ISA-8 SD-контроллер (SPI) на CPLD

можешь проект приложить?

-

newold86

- Devil

- Posts: 748

- Joined: 30 Nov 2013 11:08

- Location: WWW

Re: ISA-8 SD-контроллер (SPI) на CPLD

Вроде понятна проблема - запись происходит по быстрому сигналу, асинхронному по отношению к cs и wr, поэтому часто записывается информация с шины данных, еще не содержащая правильных данных (из-за мультиплексирования адреса/данных). Изменение полярности clk ситуацию не поменяет - нужно в корне менять подход к записи.

-

Tronix

- Doomed

- Posts: 662

- Joined: 18 Nov 2013 02:38

- Location: Москва

Re: ISA-8 SD-контроллер (SPI) на CPLD

Вот онDimkaM wrote:можешь проект приложить?

You do not have the required permissions to view the files attached to this post.