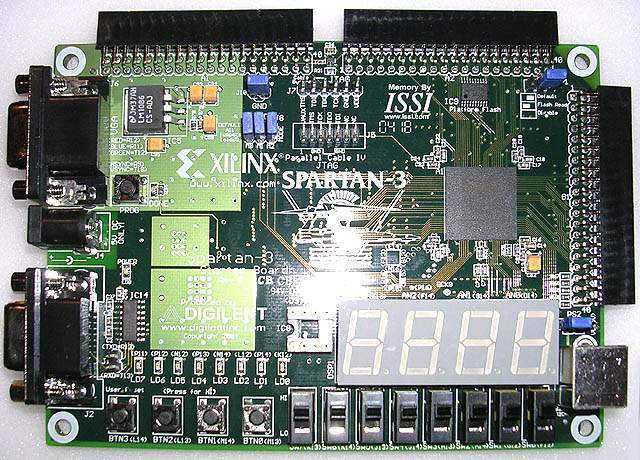

Конечно же это будет 3niti alpha

На котором можно написать эмулятор системы команд Тунгуски...

Внутри троичный сигнал будет состоять из двух двоичных:

00 - O (zero)

10 - N (negative)

01 - P (positive)

11 - X (exception or fatal error)

Если в качестве исходных схем использовать схемы для тримулятора, то там четвёртое значение - это Z (disconnected).

Я думаю, что сначала я всё таки сделаю первый вариант - непосредственно на языке схем Xilinx. Второй же вариант подразумевает наличие некоего конвертера из схем тримулятора в VHDL (что вполне возможно сделать, но требует некоторого времени).

UPDATE: Последняя версия троичной VHDL-либы с примерами всегда будет тут:

https://gitlab.com/ternary/ternary/-/tree/master/vhdl