Как бы эти команды не входят в минималистический набор, без них вполне можно обойтись. Предлагаю их реализацию отложить до версии 0.2 железа.Lavr wrote: PS. И кстати говоря (см. выше), а каково мнение джентльменов по поводу

команд IN, OUT?

4-bit Processor

Moderator: Lavr

-

VituZz

- God

- Posts: 1343

- Joined: 13 Nov 2010 04:06

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Согласен - как показывает опыт 6502 и всяких РК-86 со Специалистами - без портов жить можноVituZz wrote:Как бы эти команды не входят в минималистический набор, без них вполне можно обойтись. Предлагаю их реализацию отложить до версии 0.2 железа.Lavr wrote: PS. И кстати говоря (см. выше), а каково мнение джентльменов по поводу

команд IN, OUT?

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

У меня есть только очень небольшое соображение contra: мне кажется, еслиShaos wrote:Согласен - как показывает опыт 6502 и всяких РК-86 со Специалистами - без портов жить можноVituZz wrote:Как бы эти команды не входят в минималистический набор, без них вполне можно обойтись. Предлагаю их реализацию отложить до версии 0.2 железа.Lavr wrote: PS. И кстати говоря (см. выше), а каково мнение джентльменов по поводу

команд IN, OUT?

предполагается большая память, не доступная вся непосредственно, а только

постранично, удобнее, когда регистр страниц доступен по IN, OUT,

тогда память получается непрерывной, не так ли?

Но практически IN, OUT действительно можно впихнуть в последний

момент - это всего лишь дополнительные стробы на чтение-запись.

Хотя в прототипе они просто уже реализованы.

Насчёт префикса - мне думается, что F более удобный префикс, чем E, т.к.

однозначно отлавливается совпадением единиц.

Уточним - префикс действует только на одну команду?

NOP я предпочитаю, как 00Н (90Н у х86 для меня было просто плевком в душу).

Да так оно и логичнее "забить" NOP-ом ненужное в ПЗУ можно только нулями,

нежели единицами.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

VituZz

- God

- Posts: 1343

- Joined: 13 Nov 2010 04:06

А как вам вот это: http://www.wasm.ru/forum/viewtopic.php?id=8642?

Если баян (как вариант - боян , пинать не более одного раза.

, пинать не более одного раза.

Если баян (как вариант - боян

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Shaos трактует боян по-местному...VituZz wrote:А как вам вот это: http://www.wasm.ru/forum/viewtopic.php?id=8642?

Если баян (как вариант - боян, пинать не более одного раза.

Я лично приветствую все рассуждения в привязке к схемам, а то абстрактно

можно нарассуждать много, но это прерогатива математиков ИМХО.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Что-то это мне вдруг напомнило!!!Shaos wrote:Я посмотрел систему команд японской поделки - разумно: 15 4-битных команд плюс ещё 16 возможных после "префикса" E - всего выходит 29. Если завести второй префикс, то команд уже будет 14+16+16=46.

Code: Select all

4004 instruction set consists of 46 instructions:

Data moving instructions.

Arithmetic - add, subtract, increment, decrement.

Logic - rotate.

Control transfer - conditional (limited to current ROM), unconditional, call subroutine and return from subroutine.

Input/Output instructions.

Other - carry flag operations, decimal adjust, etc.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Как и обещал, разместил некоторые из известных систем команд 4-битных

самодельных ЦПУ здесь:

viewtopic.php?p=90363#90363

самодельных ЦПУ здесь:

viewtopic.php?p=90363#90363

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Джентльмены, ну что-то надо решать со стеком.

Обзор систем команд показывает, что PUSH и POP зело непопулярны, кстати,

и в i4004 их тоже нет.

Поэтому вопросы такие - как аппаратно выполнить стек?

Как реализуем RET?

Может у кого есть схемотехнический пример?

Пока со всеми командами (кроме переходов) можно уложиться в 4 такта

при однофазной синхронизации.

Впрочем и переходы можно уложить в них, если вы согласны с моделью

памяти смещение-сегмент (отдельный регистр - щёлкать сегментами по 256).

У меня что-то красивых решений в схемотехнике стека пока не придумалось.

Пиковские Skip if Zero и Skip if Not Zero реализовать очень легко.

Это всего лишь за 4 такта увеличить программный счетчик PCL(ow).

Безусловный JMР по идее должен быть длинным, как и CALL. Обычно

их выполняют в два цикла.

Но если JMР аппаратно реализован, то условные JMР - по идее то же самое,

только с учётом флагов.

А вот CALL... он по сути JMР только надо успеть защелкнуть текущие PCL(ow)

и PCH(igh) изменяя указатель стека.

В принципе - склоняюсь к мысли VituZz-а - стек в отдельном пространстве

памяти со своим регистром-счетчиком стека, тогда и PUSH, POP сделать легче.

Отдельный корпус ОЗУ - сугубо под стек... вполне разрешимо...

Обзор систем команд показывает, что PUSH и POP зело непопулярны, кстати,

и в i4004 их тоже нет.

Поэтому вопросы такие - как аппаратно выполнить стек?

Как реализуем RET?

Может у кого есть схемотехнический пример?

Пока со всеми командами (кроме переходов) можно уложиться в 4 такта

при однофазной синхронизации.

Впрочем и переходы можно уложить в них, если вы согласны с моделью

памяти смещение-сегмент (отдельный регистр - щёлкать сегментами по 256).

У меня что-то красивых решений в схемотехнике стека пока не придумалось.

Пиковские Skip if Zero и Skip if Not Zero реализовать очень легко.

Это всего лишь за 4 такта увеличить программный счетчик PCL(ow).

Безусловный JMР по идее должен быть длинным, как и CALL. Обычно

их выполняют в два цикла.

Но если JMР аппаратно реализован, то условные JMР - по идее то же самое,

только с учётом флагов.

А вот CALL... он по сути JMР только надо успеть защелкнуть текущие PCL(ow)

и PCH(igh) изменяя указатель стека.

В принципе - склоняюсь к мысли VituZz-а - стек в отдельном пространстве

памяти со своим регистром-счетчиком стека, тогда и PUSH, POP сделать легче.

Отдельный корпус ОЗУ - сугубо под стек... вполне разрешимо...

-

VituZz

- God

- Posts: 1343

- Joined: 13 Nov 2010 04:06

В книжке Щелкунова, Дианова "Микропроцессорные средства и системы" со страницы 21 есть некоторые соображения по набору регистров и системам команд. Я, как новичок в деле процессоростроения (и даже процессороэмуляции), несколько систематизировал свои знания. Если в двух словах, то стройная адресация и система команд возможны лишь начиная с 16-ти разрядов, более простые системы - результат компромиссов. Для 4-х разрядов это будут очень жестокие компромиссы. Поэтому, если компромиссов не избежать, я всё же склоняюсь к максимальной простоте нашего 4-разрядного детёныша динозавра. Если мы разрабатываем его в эмуляторе, то давайте сразу ограничимся 16-ю командами и минимальным набором регистров. Сделав работоспособную модель, можно будет её развивать дальше.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Работоспособную модель я уже сделал год назад зимой. Можешь взять её здесь,VituZz wrote: Если мы разрабатываем его в эмуляторе, то давайте сразу ограничимся 16-ю командами и минимальным набором регистров. Сделав работоспособную модель, можно будет её развивать дальше.

viewtopic.php?t=9213

если есть желание, и - погонять. А можешь и доработать - она не совсем

закончена, но позволяет посмотреть реализацию узлов и команд.

Я как раз и хотел плясать не от нуля, а от "живой" модели, чтобы что-то

пробовать, приделывать и т.д.

К сожалению, у меня модель зело тормозит на ноуте 360 МГц, так что сейчас

переношу именно её в "Протеус" (У меня в модели и ПЗУ микрокоманд были на

диодных матрицах)

Я тоже делаю процессор в первый раз, и навыки у меня - только от указанной

модели, на схему которой я ссылаюсь. Но она не с потолка взята, по моему

мнению, среди всего, что я рассмотрел, она довольно оптимальная, и имеет

все возможности расширения, как в развитый 4-бит, так и в 8-бит.

Впрочем, я своего мнения не навязываю, а наоборот, готов к любому

конструктивному диалогу.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Аппаратный интерфейс

Джентльмены, у кого-нибуть есть образец чисто аппаратной реализации какого-либо

популярного последовательного интерфейса: RS-232, SPI, FSK или чего-то

подобного?

Мне кажется недостойным атавизмом загружать память программ тумблерами

и кнопками в тот момент, когда наш процессор еще не способен загрузить

что-либо сам ввиду отсутствия программы.

популярного последовательного интерфейса: RS-232, SPI, FSK или чего-то

подобного?

Мне кажется недостойным атавизмом загружать память программ тумблерами

и кнопками в тот момент, когда наш процессор еще не способен загрузить

что-либо сам ввиду отсутствия программы.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

Реализация стека

Здесь приведена схема уже проверенного на макете узла программного счётчика

и программной памяти 4-битного ЦПУ.

Видно, что без особых проблем мы сможем сделать шину команд-данных 16-разрядной.

Поскольку в прототипе стек никак не реализован, а возврат выполнен как

рестарт по фиксированному адресу, образца схемотехники стека я не имею.

Как мне кажется, аппаратный стек должен быть выполнен по такому-же принципу:

счетчик адреса стека + ОЗУ стека.

Если не использовать PUSH и POP, как в PIC, то счетчик адреса стека будет

работать только на инкремент и декремент, сохраняя в своём ОЗУ только

значения PCH(igh)-сегмента адреса и PCL(ow)-программного счётчика, который

на момент выполнения CALL, после выборки КОП CALL, уже априори содержит

адрес следующего КОП - а это и есть адрес возврата, который надо сохранить

в ОЗУ стека, и сдвинуть счетчик адреса стека на единицу.

Если у кого есть другие мысли о схемотехнике стека - готов выслушать.

и программной памяти 4-битного ЦПУ.

Видно, что без особых проблем мы сможем сделать шину команд-данных 16-разрядной.

Поскольку в прототипе стек никак не реализован, а возврат выполнен как

рестарт по фиксированному адресу, образца схемотехники стека я не имею.

Как мне кажется, аппаратный стек должен быть выполнен по такому-же принципу:

счетчик адреса стека + ОЗУ стека.

Если не использовать PUSH и POP, как в PIC, то счетчик адреса стека будет

работать только на инкремент и декремент, сохраняя в своём ОЗУ только

значения PCH(igh)-сегмента адреса и PCL(ow)-программного счётчика, который

на момент выполнения CALL, после выборки КОП CALL, уже априори содержит

адрес следующего КОП - а это и есть адрес возврата, который надо сохранить

в ОЗУ стека, и сдвинуть счетчик адреса стека на единицу.

Если у кого есть другие мысли о схемотехнике стека - готов выслушать.

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

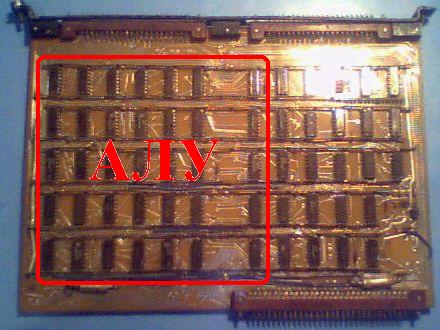

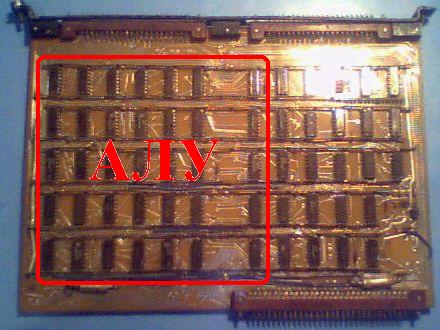

Кстати - приведу живой, зримый и убеждающий пример, почему я склонился к

4-битной конструкции. 8-битное АЛУ на NAND, в том виде, как оно уже разработано,

займёт на макетке примерно столько места, сколько выделено на приведенном

здесь рисунке.

Для всего ЦПУ УЖЕ остаётся очень мало места! Поэтому я и решил пойти на 4-битный

компромисс. Конечно, решение не окончательное, но габариты нас поджимают.

PS. Можно, конечно, свернуть это в 2 корпуса 74181 (К155ИП3), но тогда зачем

весь этот огород городился? - Не спортивно...

- Не спортивно...

4-битной конструкции. 8-битное АЛУ на NAND, в том виде, как оно уже разработано,

займёт на макетке примерно столько места, сколько выделено на приведенном

здесь рисунке.

Для всего ЦПУ УЖЕ остаётся очень мало места! Поэтому я и решил пойти на 4-битный

компромисс. Конечно, решение не окончательное, но габариты нас поджимают.

PS. Можно, конечно, свернуть это в 2 корпуса 74181 (К155ИП3), но тогда зачем

весь этот огород городился?

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Аппаратный интерфейс

SPILavr wrote:Джентльмены, у кого-нибуть есть образец чисто аппаратной реализации какого-либо

популярного последовательного интерфейса: RS-232, SPI, FSK или чего-то

подобного?