Мы часто в раных топиках обсуждаем разделение адресного пространства i8080

на разные страницы на основе битов слова состояния STATUS.

И я всегда начинаю метаться по форуму в поисках этих картинок.

Пусть лучше будут здесь в одном месте, чтобы можно было обсуждать предметно...

Временная диаграмма выполнения обобщенного машинного цикла микропроцессора

i8080 приведена на рисунке:

Увеличить

Заметим, что оба сигнала ПМ и ВД изображены здесь активными условно.

ADDR - ША [0—15] - выходные сигналы тины адресов для адресации

памяти или портов ввода — вывода;

DATA - ШД [0—7] — входные или выходные сигналы двунаправленной шины данных

для обмена данными с памятью или портами ввода - вывода, а также для вывода

из микропроцессора информации о его состоянии;

F1, F2 - С1, С2 — входные периодические сигналы для тактирования микропроцессора;

SYNC - С — выходной сигнал синхронизации, вырабатываемый в начале каждого

машинного цикла и указывающий, что, но шине данных передается информация

о состоянии микропроцессора;

RES - СБР — входной сигнал установки микропроцессора в начальное состояние,

обеспечивающее выполнение программы с команды, содержащейся в ячейке памяти

с адресом 0000Н;

DBIN - ПМ — выходной сигнал, инициирующий выдачу данных периферийными модулями

на шину данных;

WRITE - ВД — выходной сигнал, сопровождающий выдачу микропроцессором информации

на шину данных для записи в периферийные модули;

READY - ГТ — входной сигнал от модулей памяти или портов ввода — вывода,

указывающий на их готовность к обмену данными с микропроцессором;

WAIT - ОЖ — выходной сигнал при ожидании микропроцессором готовности периферийных

модулей;

HOLD - ЗХ — входной сигнал, инициирующий перевод шин адресов и данных микропроцессора

в высокоимпедансное состояние;

HLDA - ПЗХ — выходной сигнал, подтверждающий перевод шин адресов

и данных микропроцессора в высокоимпедансное состояние;

INTE - РПР — выходной сигнал разрешения прерывания выполнения текущей программы;

INT - ЗПР — входной сигнал запроса прерывания.

В каждом такте любого машинного цикла микропроцессор выполняет определенные действия:

T1 — устанавливает код адреса периферийного модуля на шине адресов.

Т1/Т2 — выводит информацию о своем состоянии (STATUS) по шине данных,

Т2 — проверяет состояние сигналов на входа READY и HOLD,

Т3 — реализует обмен одним байтом информации с памятью или портами,

Т4/Т5 — выполняет внутренние межрегистровые передачи и обработку данных

в соответствии с командой.

Подробнее с этой информацией можно ознакомиться по следующим адресам:

http://retro.h1.ru/MK80/CPU/M80CPUi.php

http://www.danbigras.ru/MK80/CPU/M80CPUi.html

В более сложных микро-ЭВМ используют дополнительные сигналы управления, выдаваемые

микропроцессором на шину данных в тактах Т1/Т2 в виде 8-разрядного кода — байта (слова)

состояния, который по сигналу синхронизации SYNC - С запоминается (фиксируется) во

внешнем регистре и определяет действия микропроцессора в остальных тактах текущего

машинного цикла. Использование байта (слова) состояния позволяет однозначно определить,

с какой группой периферийных модулей происходит обмен данными в текущем машинном

цикле. Наличие единицы в отдельных разрядах слова состояния - STATUS является признаком

выполнения микропроцессором в текущем машинном цикле следующих действий:

ШД[0] (ППР) — обслуживание запроса прерывания;

ШД[1] (3В) — запись в память или вывод данных в порт;

ШД[2] (СТК) — обращение к области памяти, используемой в качестве стека;

ШД[3] (ОСТ) — останов микропроцессора по команде HLT,

ШД[4] (ВЫВ) — вывод данных в порт,

ШД[5] (M1) — чтение кода операции команды,

ШД[6] (ВВ) -- ввод данных из порта,

ШД[7] (ЧТП) — чтение данных из памяти.

Слово состояния - STATUS обычно обабатывается системным контроллером (К580ВК28/38)

для формирования сигналов обращения к памяти, устройствам ввода/вывода и к контроллеру

прерываний: MEMRD, MEMWR, IORD, IOWR, INTA.

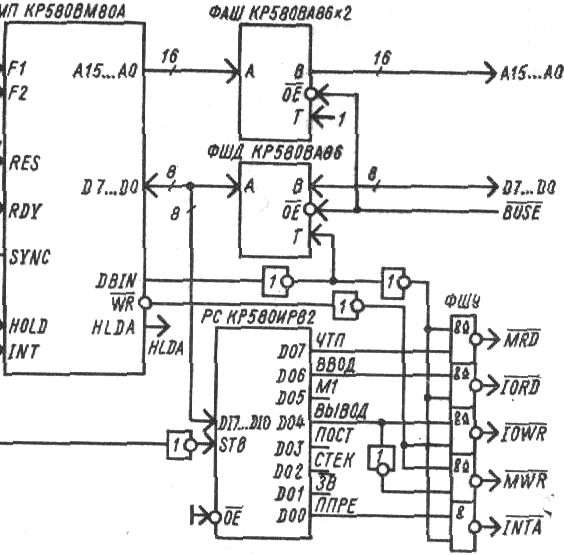

Но можно сформировать эти же сигналы и более простой схемой:

Здесь сигнал СТС(STB) (от ГТИ) - это укороченный по длительности сигнал SYNC - С, пропущенный

через генератор К580ГФ24(8224) и соответствующий середине длительности STATUS.

Отметим, что сигналы MEMRD, MEMWR, IORD, IOWR формируются вентилями с открытым коллектором,

чтобы не вступать в конфликт с одноименными сигналами контроллера ПДП.

--------------------------------------

Что-то, мне кажется, эта схема выше не очень правильная в плане формирования INTA...

Вот эта - более верная, поскольку INTA - это DBIN (RD), но перенаправленный

к источнику команды прерывания...

То есть, стробом INTA процессор считывает от 1 до 3 байт, от устройства прерывания,

как делал бы это из памяти, но стробом DBIN...

А там выше они INTA из STB сделали, что меня несколько смущает...

Более конкретная, правильная схема из независимого источника:

Источник: Артюхов и др. Проектирование микропроцессорной электронно-

вычислительной аппаратуры. Справочник. - Киев, 1988. с.46.