там внутри принципиальная схема процессора, описание команд блоков и тд.

как подключать скорее всего надо искать ОСТ на процессор.

Оглавления ТО

Moderator: Shaos

Вот меня этот AR тоже обеспокоил, т.к. в 1801ВМ1 - его нет, а у меня 1801ВМ1,Shaos wrote:А вот интересно - зачем они в ВМ2 воткнули этот AR? Его небыло в ВМ1 (и вроде как нет в ВМ3). Его небыло в LSI-11 (и соответственно в Q-bus). Более того - его нету и в ГОСТе на МПИ! Тогда НАФИГА этот лишний сигнал подтверждения в процессоре, который как бы реализует именно МПИ (Q-bus)?Shaos wrote:AR - адрес принят (в LSI-11 нету) - участвует в циклах обмена с шиной (проц не будет выдавать DIN/DOUT пока не получит этот сигнал от периферии)

...

P.P.S. Сигнал AR по видимому можно получить на инверсном выходе RS-триггера, взводимого от SYNC и сбрасываемого по RPLY, также ещё потребуется некоторая логика т.к. SYNC и RPLY могут быть нулевыми одновременно и это значит что схема уже не будет содержать просто проц и несколько просто родных памятей...

В БК-шке сигнал AR - это, по сути, синхронно задержанный на несколько тактов CLC сигнал SYNC.Шахнов wrote:Микросхема КМ1801ВМ2 наряду с синхронной адресной частью обмена по системной магистрали имеет возможность асинхронной работы при передаче адреса. Это обеспечивается с помощью входного сигнала AR «Адрес принят» (Address Received). После выдачи адреса на системную магистраль ОМП ожидает появления сигнала AR. Низкий уровень входного сигнала AR свидетельствует о том, что пассивное устройство приняло адрес и ОМП может продолжать цикл обмена по системной магистрали.

Вот поэтому мне очень хотелось глянуть типовую схему включения ЦПУ 1801ВМ2.КМ1801ВМ2 Справочник - А.Кислый wrote:AR – адрес принят устройством. Устанавливается устройством в ответ на сигнал SYNC. Используется для асинхронного обмена по магистрали. В случае использования синхронного обмена и для совместимости с шиной QBUS (МПИ) выход SYNC необходимо соединить со входом AR через буферный усилитель. Активный уровень – низкий.

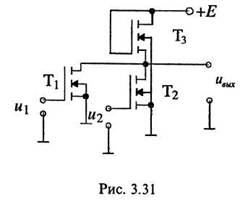

Я что-то одну вещь никак не пойму: почему на УГО ЦПУ на шинах адреса-данныхShaos wrote:Стандартное отображение процессора на схемах:

Вот за подобные фокусы я и не люблю "расово верные" отечественные камни...КМ1801ВМ2 Справочник - А.Кислый wrote:AD00 – AD15 – 16 выводов сигналов адреса и данных, которые передаются по магистрали. У МП совмещённая шина адреса и данных, при адресном обмене сначала на шине выставляется адрес, а затем выставляются данные, если производится запись, или выводы AD00-AD15 переключаются в режим входов для чтения данных с магистрали. Активный уровень – низкий, т.е. электрический ноль соответствует логической единице.

Слушай чего - а какой тип выходных каскадов у этих 1801ВМхх?Случайность wrote:по ОСТу между выходом ТМ2 и ногой процессора REPLY должен включаться логический элемент с ОК но вместо этого экономят микросхемы и ставят резистор.

Не - ты понимаешь, на шины и в обратную сторону из схемы работают открытым коллектором...VituZz wrote:Резисторов куча может быть при любом типе выходов. Просто чтобы наверняка зафиксировать уровни при чтении.

Спасибо - кое что подправил... значит всё-таки ACLO - активен по спаду?Случайность wrote:Вот официальное УГО для К1801ВМ2

глянул схемку БК. Да так и есть резисторы на месте. точнее резисторые матрицы. Но я не вижу в них ничего плохого. Это всего лишь особенность процессора, как особенность 580ВМ80 три напряжения питания. Но ведь были умельцы которые запитывали от одного. Не в Радио ли схемка была как это сделать.Получается несколько неприятная вещь - этот процессор надо обвесить практически

36-ю резисторами по выводам?

А что - в схемах БК-0010 или УК-НЦ - это так и есть?

А без резисторов - что совсем не заработает? На низкой частоте если...Случайность wrote:глянул схемку БК. Да так и есть резисторы на месте. точнее резисторые матрицы.Получается ... этот процессор надо обвесить практически

36-ю резисторами по выводам?

А что - в схемах БК-0010 или УК-НЦ - это так и есть?

А вот теперь пару слов от том, что в этом плохого, и что я, собствено, и предполагал...Случайность wrote:глянул схемку БК. Да так и есть резисторы на месте. точнее резисторые матрицы. Но я не вижу в них ничего плохого. Это всего лишь особенность процессора, как особенность 580ВМ80 три напряжения питания.Lavr wrote:этот процессор надо обвесить практически

36-ю резисторами по выводам