Shaos wrote:В прошлом 2012 году у меня возник интерес к PDP-11 (в основном на почве интереса к

КМ1801ВМ2 и

КМ1801ВМ3).

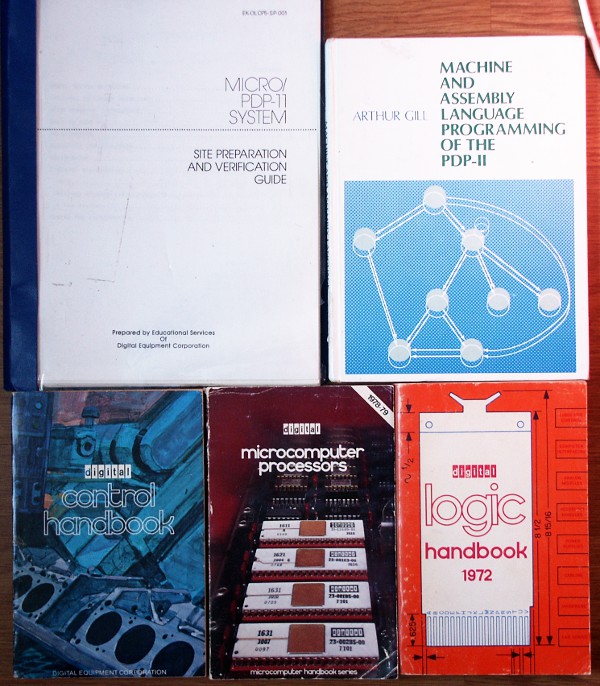

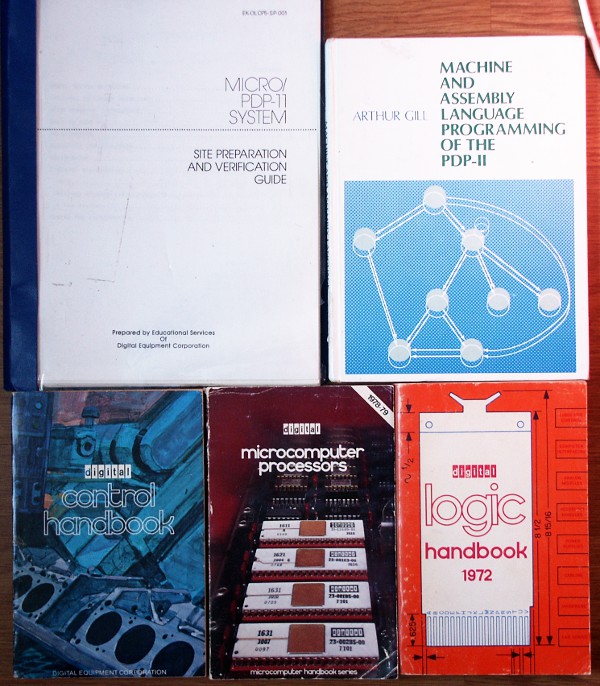

Интерес вылился в покупку вот таких книжек (некоторые из них

PDP-8 тоже задевают):

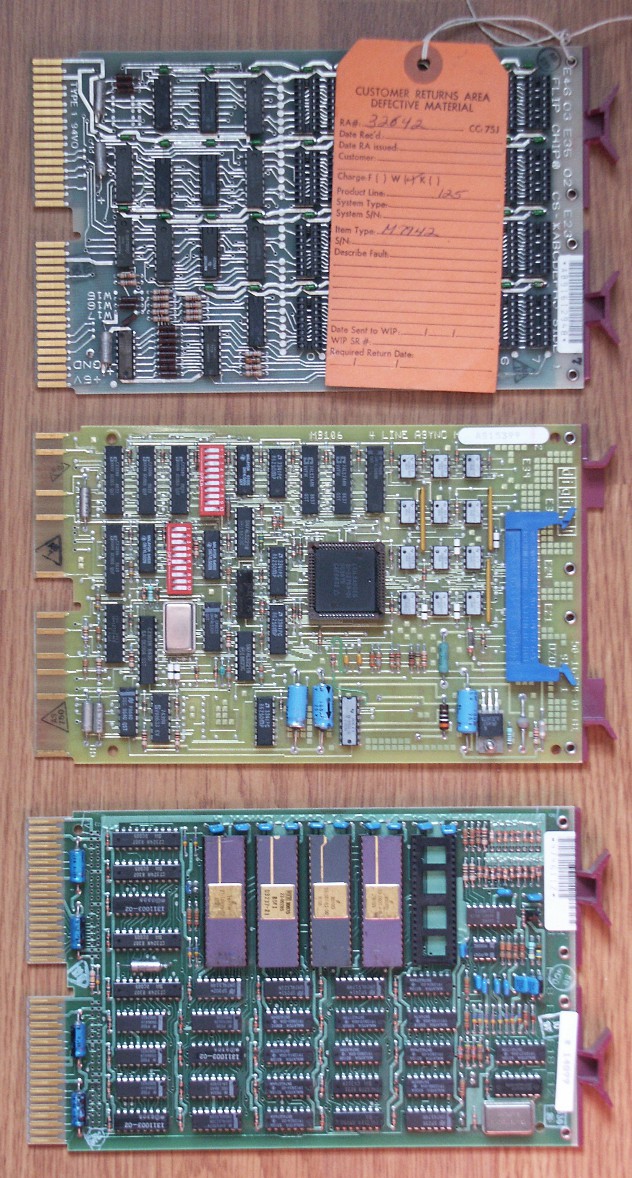

В нижнем ряду первая и последняя книжки в основном про старые флип-чипы, на которых PDP-8 построена и до, а вот средняя - как раз то что нужно - про LSI-11 и в частности про ту плату, которая у меня есть (M7270) - с описанием контактов, джамперов, диаграммами и т.д. Эта книжка говорит, что в Q-bus циклы работы с памятью устроены так:

- по фронту SYNC внешний девайс должен защёлкнуть адрес с мультиплексированной шины и ждать DIN или DOUT;

- по фронту DIN внешний девайс выдаёт логическую единицу в RPLY, выдаёт на шину данных нужное слово убираемое после спада DIN вместе с обнулением RPLY;

- по фронту DOUT внешний девайс выдаёт логическую единицу в RPLY, читает слово (либо байт если WTST="1" - старший при A0=0 или младший при A0=1), ждёт сброcа DOUT и далее сбрасывает RPLY.

При адресации слов сигнал адреса A0 игнорируется - он учитывается только при записи отдельных байтов (если WTST="1").

Похожий "handshake" есть для работы с DMA, для прерываний IRQ и даже по включению - с блоком питания

P.S. Диаграммы в книжке вводят в заблуждение, т.к. из текста похоже, что все сигналы управления шиной инверсные (активный ноль), а на диаграмме всё нарисовано наоборот - т.е. там где на картинке изображено срабатывание по фронту на самом деле будет срабатывание по спаду...

P.P.S. Вот PDF-ка официальной книжки про UNIBUS и Q-Bus (LSI-11 bus):

http://bitsavers.informatik.uni-stuttga ... ok1979.pdf

Тут на 132 странице есть замечание, что на диаграммах показано внутреннее (для процессора и для периферии) состояние сигнала, который по шине идёт в инверсном виде...