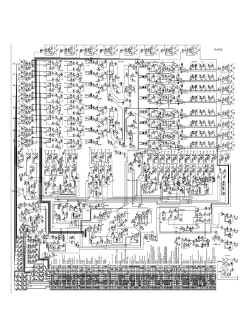

А где-то попадалась мне схема 6502 на транзисторах - в ней явно10 Сен 2006 15:51 lvd wrote:Ну так в 6502 тоже нет микрокода - все операции заданы даже не в масочной матрице - просто связями элементов.

видна была матрица...

Moderator: Lavr

А где-то попадалась мне схема 6502 на транзисторах - в ней явно10 Сен 2006 15:51 lvd wrote:Ну так в 6502 тоже нет микрокода - все операции заданы даже не в масочной матрице - просто связями элементов.

Действительно так и есть:Lavr wrote:А где-то попадалась мне схема 6502 на транзисторах - в ней явноНу так в 6502 тоже нет микрокода - все операции заданы даже не в масочной матрице - просто связями элементов.

видна была матрица...

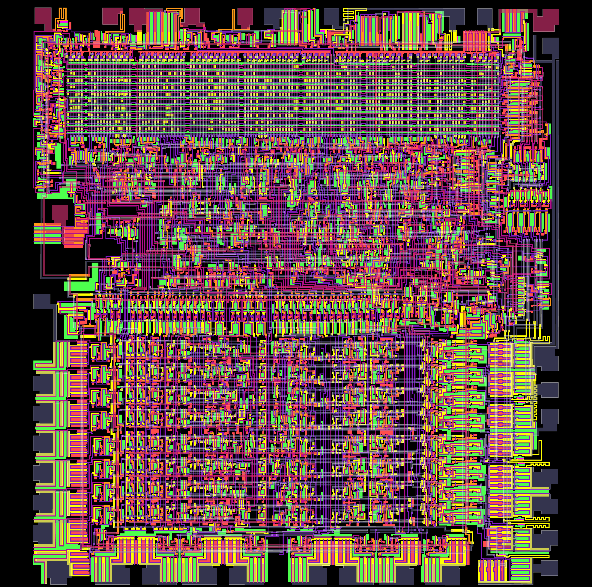

Интересно, что и на кристалле 6502 матрица отчётливо видна:Lavr wrote:А где-то попадалась мне схема 6502 на транзисторах - в ней явно видна была матрица...

Что-то ты как-то поздно проснулся. А вот такое:Shaos wrote:А какое отношение это имеет к TV80?

P.S. Откусил всё что касается матрицы в 6502 и перенёс в отдельный топик...

10 Сен 2006 15:51 lvd wrote:Ну так в 6502 тоже нет микрокода - все операции заданы даже не в масочной матрице - просто связями элементов. И разводили его вообще руками на бумаге.Ronin wrote:нет микрокода ? и CISC ? ну Фаджин и маньяк

HardWareMan wrote:PPS Чел на Эмураши разбирает кристал для низкоуровневой симуляции ядра 6502, который присутствует в процессоре NES в несколько усеченном виде. Фишка в том, что чел все объясняет открыто, а не тарит как у Visual6502.

Так ты не смотрел что-ли?Lavr wrote:Ну а коли показывал, и сам смотрел - масочная матрица в 6502 или просто связи элементов?

Софтваред или хардкоред процессор 6502?

org wrote:Декодер инструкций (PLA)

Расположение на чипе :

Для удобства я перевернул картинку цветной схемы набок :

Транзисторную схему рисовать не буду, потому что тут и так всё понятно.

На вход декодера поступает регистр инструкции (IR), в котором содержится код текущей инструкции (при этом бит0 и бит1 заведены на одну линию) + его инвертированный вариант (/IR), а также текущий такт (T0-T5).

Дополнительный вход BranchReady идёт с логики RDY.

Как происходит декодирование ?

Если хотя бы одна линия пересекается с диффузией, то заряд стекает на землю и линия "не срабатывает".

Поэтому логика каждого входа (присоединенного к диффузии) такая:

Если НЕ(ВХОД_1) И НЕ(ВХОД_2) И НЕ(ВХОД_N) -> линия срабатывает.

Ну и дополнительно для перехода линия срабатывает только в том случае, если BranchReady = 1.

Я смотрел, только смотрим мы все одно и то же, а вот выводы делаем разные...HardWareMan wrote:Так ты не смотрел что-ли?

HardWareMan wrote:Just for fun наверное.Lavr wrote:PS. Немного не понял я затею мужика по ссылке. Зачем ему по-новой делать

реверс 6502? Ведь его схема на MOSFET-ах известна, да и на логических

вентилях - я видел...