Правильно подглядывали. И система команд на порядок лучше, и шина данных в два раза шире. Вот только не надо было передирать один-в-один. Совмещённая шина адреса/данных убивает нафиг всю производительность. Тут интел оказался молодцом. Надо было сделать проц с той же архитектурой, но с раздельной шиной. Программы работали бы не хуже, а вот производительность поднялась бы на порядок.Lavr wrote:Всё же на этом пути они больше подглядывали к PDP..

КР1801ВМ1

Moderator: Shaos

-

b2m

- Devil

- Posts: 948

- Joined: 26 May 2003 06:57

Страничка эмулятора наших компьютеров

http://bashkiria-2m.narod.ru/

http://bashkiria-2m.narod.ru/

-

vinxru

- Retired

- Posts: 587

- Joined: 27 Mar 2013 04:55

- Location: 62.192.229.16

-

b2m

- Devil

- Posts: 948

- Joined: 26 May 2003 06:57

Но уже в 80286 отказались от этого, что позволило поднять производительность при тех же тактовых частотах.vinxru wrote:А в 8086 шины данных и адреса уже объединены.

Страничка эмулятора наших компьютеров

http://bashkiria-2m.narod.ru/

http://bashkiria-2m.narod.ru/

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Нет, изюминки в PDP есть!.. Но ввод/вывод у неё мне представляется несколько надуманнымb2m wrote:Правильно подглядывали. И система команд на порядок лучше, и шина данных в два раза шире.Lavr wrote:Всё же на этом пути они больше подглядывали к PDP..

Вот только не надо было передирать один-в-один.

и тяжеловатым...

iLavr

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Да это у них была проблема DIP-40 при разработке 8086...b2m wrote:Но уже в 80286 отказались от этого, что позволило поднять производительность при тех же тактовых частотах.vinxru wrote:А в 8086 шины данных и адреса уже объединены.

А как перешли на другие корпуса, от "мультиплексии" тут же и отказлись.

iLavr

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Я вот думаю, что если уж мы взялись драть у Интел - надо было делать сразу лучше Интел...b2m wrote:Совмещённая шина адреса/данных убивает нафиг всю производительность. Тут интел оказался молодцом.

То есть не плодить К580ВМ80, так, что он и сейчас не кончается...

А быстрее сделать улучшенный - 580ВМ1...

Хотя.. после времени - это лишь ретро-мечты...

iLavr

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Я подумал, что для процессора 1801ВМ1 тестовую схему с имитацией NOP также адаптировать можно:Lavr wrote:Ты имеешь в виду вот этот момент?Случайность wrote:Насчет проверки ВМ1 по типу ВМ80, увы она практически невозможна. Из за того что его регистры находятся в линейном адресном пространстве...1801ВМx wrote:Микропроцессор имеет некоторые рудименты микро-ЭВМ К1801ВЕ1, в частности, программируемый таймер (177706-177712) и регистры межпроцессорной связи (177700-177704)

Смотреть

Поскольку в верхних адресах у него предполагаются порты, да и в принципе - верхние 8КБайт его

адресного пространства отдают под порты, то логично доработать схему тестирования узлом

сброса процессора по адресу 0E000H = 1110.0000.0000.0000b на инверсной шине 0001.1111.1111.1111b.

То есть, достаточно сделать сброс по трём старшим нулям на шине адреса.

После чего тест продолжится с нулевого адреса.

Элементы ИЛИ - DD7.3, DD7.4 отслеживают нули в разрядах А13-А15. Инвертор DD1.4 делает этот сигнал

активным логической "1".

После чего вентиль DD5.4 по этому сигналу при ACLO="1" открытым коллектором разряжает конденсатор С2,

чем и осуществляет сброс.

В остальном принцип работы схемы такой-же, как описано здесь. Значок "*" на схеме возле названий сигналов

означает "буферированный" или "умощненный".

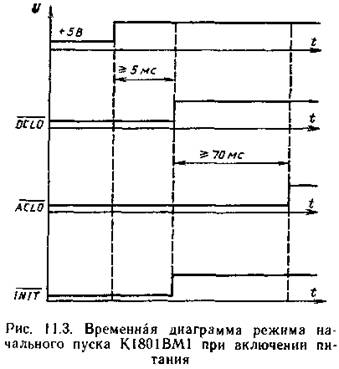

Я добавил диод VD2 в цепь сброса, поскольку при подробном рассмотрении оказалось, что последовательность

подачи сигналов ACLO и DCLO в схеме из МПСС отличается от приведенной в справочнике.

---------------

ACLO и DCLO должны быть в "0" одновременно, а ACLO - должен перейти в "1" позже DCLO.

Несколько также беспокоит разрядка С2 открытым коллектором DD5.4. Но надеюсь, что процесс достаточно кратковремнный,

и выходной транзистор DD5.4 не пробьёт.

Если будут какие-либо замечания по существу - учту непременно, хотя, согласно имеющимся справочным данным, я и

постарался, по возможности, всё предусмотреть.

iLavr

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Вот эта полоска на процессорах в керамике меня озадачивала всегда...

Но, похоже, что с этим вопросом - я разобрался! Спасибо документации!

КМ1801ВМ2 wrote:На торце процессора имеется технологическая площадка-вывод подложки. Нормальное напряжение на ней около -2В, замеренное прибором со входным сопротивлением 1МОм. Для получения максимального быстродействия (более 2млн оп/с) может потребоваться подключить между обшим проводом и этой плошадкой керамический конденсатор 47н.

Некоторые процессоры имеют заниженное значение отрицательного смещения на подложке (менее 1.5 В), что приводит к перегреву процессора на тактовых частотах выше 50%-75% от максимальной. Подключение конденсатора мeжду подложкой и общим проводом увеличивает смещение на подложке на 15-20%.

iLavr

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

-

Shaos

- Admin

- Posts: 25035

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re:

Вот тут вроде есть 2-процессорный вариант подключения ВМ1 с программируемой логикой:Shaos wrote:28 апр 2013 17:04

P.S. Материалы про 1801 процы (включая схемы БК-шек):

http://vak.ru/doku.php/proj/bk-fpga

http://vak.ru/doku.php/proj/bk/1801vm1

http://vak.ru/doku.php/proj/bk/1801vm-series

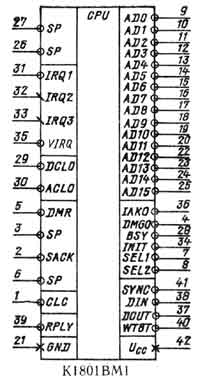

Судя по описанному там, некоторые выводы К1801ВМ1, обозванные на картинке "SP" имеют вполне конкретное назначение:

27 - это PA0

26 - это PA1

которые обозначают адрес процессора в системе (отсюда следует, что процессоров не может быть больше четырёх)

3 - это DMGI (вход одобрения захвата шины от предыдущего процессора - в LSI-11 используется тот же механизм)

6 - автор пишет, что назначение неизвестно (соединить с +5), однако я могу предположить, что это IAKI (по аналогии с DMGI это также вход одобрения от предыдущего проца, но прерывания - как в LSI-11).

http://zx-pk.ru/threads/21192-eksperimentalnye-protsessornye-moduli-2kh1801vm1-i-1801vm2.html

P.S. ВМ2 схемка там тоже есть, правда однопроцессорная...

P.P.S. и ВМ3 схемка тоже есть, правда автор указывает на странные глюки у него, решаемые навешиванием конденсаториков на все AD...

-

Shaos

- Admin

- Posts: 25035

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: КР1801ВМ1

Вот детальное техническое описание 1801ВМ1 (причём прошлогоднее) по итогам реверсинжыниринга:

https://github.com/1801BM1/cpu11/raw/master/vm1/doc/1801vm1.pdf

Там детально описано поведение многопроцессорной конфигурации и даже примеры кода есть

Также задокументированы рудименты от 1801ВЕ1, причём один из таких ранее недокументированных рудиментов - таймер - даже полноценно функционирует в 1801ВМ1Г (и частично функционирует в других буквах - этот таймер даже попал в одно описание БК как фича именно БК) и нога номер 6 (я там чуть выше пытался гадать что оно есть) используется именно для него:

https://github.com/1801BM1/cpu11/raw/master/vm1/doc/1801vm1.pdf

Там детально описано поведение многопроцессорной конфигурации и даже примеры кода есть

Также задокументированы рудименты от 1801ВЕ1, причём один из таких ранее недокументированных рудиментов - таймер - даже полноценно функционирует в 1801ВМ1Г (и частично функционирует в других буквах - этот таймер даже попал в одно описание БК как фича именно БК) и нога номер 6 (я там чуть выше пытался гадать что оно есть) используется именно для него:

You do not have the required permissions to view the files attached to this post.

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: КР1801ВМ1

Про таймер в ВМ1 всегда писали, что он есть. Только пользоваться не рекомендовали из-за рудиментарностиShaos wrote:один из таких ранее недокументированных рудиментов - таймер - даже полноценно функционирует в 1801ВМ1Г (и частично функционирует в других буквах ...

и недокументированности официально.

iLavr

-

bk-m

- Writer

- Posts: 19

- Joined: 03 Jun 2013 11:22

- Location: Минск

Re:

-Lavr wrote: Я подумал, что для процессора 1801ВМ1 тестовую схему с имитацией NOP также адаптировать можно:

Смотреть

Поскольку в верхних адресах у него предполагаются порты, да и в принципе - верхние 8КБайт его

адресного пространства отдают под порты, то логично доработать схему тестирования узлом

сброса процессора по адресу 0E000H = 1110.0000.0000.0000b на инверсной шине 0001.1111.1111.1111b.

То есть, достаточно сделать сброс по трём старшим нулям на шине адреса.

После чего тест продолжится с нулевого адреса.

Элементы ИЛИ - DD7.3, DD7.4 отслеживают нули в разрядах А13-А15. Инвертор DD1.4 делает этот сигнал

активным логической "1".

После чего вентиль DD5.4 по этому сигналу при ACLO="1" открытым коллектором разряжает конденсатор С2,

чем и осуществляет сброс.

В остальном принцип работы схемы такой-же, как описано здесь. Значок "*" на схеме возле названий сигналов

означает "буферированный" или "умощненный".

Я добавил диод VD2 в цепь сброса, поскольку при подробном рассмотрении оказалось, что последовательность

подачи сигналов ACLO и DCLO в схеме из МПСС отличается от приведенной в справочнике.

---------------

ACLO и DCLO должны быть в "0" одновременно, а ACLO - должен перейти в "1" позже DCLO.

Несколько также беспокоит разрядка С2 открытым коллектором DD5.4. Но надеюсь, что процесс достаточно кратковремнный,

и выходной транзистор DD5.4 не пробьёт.

Если будут какие-либо замечания по существу - учту непременно, хотя, согласно имеющимся справочным данным, я и постарался, по возможности, всё предусмотреть.

ВМ1 отличается от ВМ2 и в этой схеме есть некоторые противоречия:

1) если тестирование идёт не всего адресного пространства (а в виде "минус 8К") то до SEL1 и SEL2 попросту не дойдёт (тогда к ним подключены лишние элементы) - а это неправильно, цепочку с *А13*А14*А15 нужно убрать

2) SEL2 через инвертор D3.3 подкл. к выв.2 D5.4, SEL1 не нужно никуда подключать (D3.2 лишнее)

3) на выходе D5.4 поставить небольшой ограничительный резистор, напр. 330 ом

-

Итог этих изменений - циклический тест до адреса 177716

Last edited by bk-m on 05 Jul 2019 08:52, edited 2 times in total.

-

Lavr

- Supreme God

- Posts: 16989

- Joined: 21 Oct 2009 08:08

- Location: Россия

Re: Re:

Вот этот момент не понял, объясните, как SEL1 сбросит на начало теста ?bk-m wrote:2) SEL1 сбросит на начало теста (до SEL2 в этой схеме не дойдёт) - значит SEL1 не нужно никуда подключать

iLavr