Использование стандартных КМОП микросхем и КМОП транзисторов

Moderator: haqreu

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Shaos - ты не обижайся, я не придираюсь - ты просто взглянь на их характеристику -Shaos wrote:Ладно-ладно, убедил - вечерком пущу треугольный сигнал через все схемки и вырежу из осциллограммы кривые, олицетворяющие собой передаточную функцию для каждого блочка...

на ней же явно показано что я хочу увидеть - и они именно на этом делают акцент

на характеристике.

Я ж тоже моделировал эти схемы на полевиках - ну серьёзно, не всякое "составленное из

pMOS-транзистора и nMOS-транзистора" работает как CMOS-invertor.

Всё зависит от этих самых pMOS-транзистора и nMOS-транзистора - поэтому я и хочу увидеть

переходную. Я б и сам попробовал молча - но пакеты у нас с тобой разные для моделирования

в ходу.

Вот же - посмотри, я сам, в этом разделе уже наступил на эту граблю, и просто подсказал тебе,

чтобы ты не повторил похожей ситуации.

iLavr

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Чувак вот так треугольным входным сигналом тестил CMOS-инверторы в LTspice - причём с модифицированными транзисторами, чтобы порог срабатывания двигать:

http://www.youspice.com/ys/en/project/s ... verter.3sp

P.S. Там кстати на схемке видно как через директиву .include можно включать модели CMOS-ов от cmosedu

http://www.youspice.com/ys/en/project/s ... verter.3sp

P.S. Там кстати на схемке видно как через директиву .include можно включать модели CMOS-ов от cmosedu

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Использование стандартных КМОП микросхем и КМОП тран...

Пересчитал более внимательно - если входные троичные сигналы разбивать на 4 двоичных, а каждый троичный мультиплексор будет состоять из 8 транзисторов (как я и рисовал до этого - 4 выключателя, соединённых как 3 переключателя), то потребуется 3*(8+8)+12*8 = 48+96 = 144 транзистора. На самом деле если мультиплексоров намного больше чем входов, то лучше разбивать входные троичные сигналы на 6 двоичных - при этом каждый троичный мультиплексор будет состоять только из 6 транзисторов (3 выключателя), тогда потребуется 3*(8+12+4)+12*6 = 72+72 = 144 транзистора (хм, видимо такое упрощение будет работать только для очень больших схем). Потом если выкинуть шесть инверторов, введённых "для крутизны фронтов", то уже получается 132 vs 126 транзисторов. Кроме того NAND/NOR можно заменить на инверторы с модифицированными транзисторами во втором крыле - тогда количество транзисторов уменьшится ещё на 6 и станет 126 vs 120...Shaos wrote:Подсчитал с учётом последних решений партии и правительства - получилось 120 транзисторов для одного полного троичного сумматора. Троичный полный сумматор имеет 27 входных состояний и 2 троичных выхода (9 выходных состояний), а у двоичного полного сумматора 28 транзисторов, 8 входных состояний и 2 двоичных выхода (4 выходных состояния). Если умножить 27 троичных состояний на log3/log2 то получим примерно 43 двоичных состояний, что в 5.3 раза больше, чем у двоичного полного сумматора, далее умножим 5.3 на 28 транзисторов из двоичного полного сумматора и получим 148 - такое количество транзисторов понадобиться, чтобы создать аналогичную по сложности схему в двоичном варианте - в этом отношении 120 выглядит вполне неплохо. Ещё один вариант оценки - 3-тритный троичный сумматор примерно равносилен 5-битному двоичному - это 3*120=360 против 5*28=140 транзисторов - при такой оценке получается проигрышь...Shaos wrote:Сумматор А+В+С=S+Co требует около 140 транзисторов, тогда как двоичный КМОП сумматор - 28

P.S. 120 транзисторов это 60 CMOS-пар - 60 корпусов ALD1115, 30 корпусов ALD1105 или 20 корпусов CD4007 (на самом деле больше, т.к. в CD4007 два из шестри транзисторов могут быть использованы только как инвертор либо как часть NOR или NAND), напомню также, что троичный полный сумматор можно построить всего лишь на 12 микросхемах DG403 (в каждой из них 2 нормально замкнутых CMOS-ключа и 2 нормально разомкнутых CMOS-ключа, а также "встроенный" преобразователь из троичного в двоичный сигнал управления ключами).

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Попробовал включить таким образом C5_models.txt - порог NAND не сдвигается, то ли ошибка в модели, то ли в симуляторе, а вот более простая 1um модель работает как надо и в NAND, и в NOR. Хотя с 0.5 um возможно дело в том, что порог обычного инвертора, составленного из C5_models.txt, уже сдвинут влево, причём так, что NAND отрезает ровно по середине, т.е. эта модель не совсем комплиментарная...Shaos wrote:Чувак вот так треугольным входным сигналом тестил CMOS-инверторы в LTspice - причём с модифицированными транзисторами, чтобы порог срабатывания двигать:

http://www.youspice.com/ys/en/project/s ... verter.3sp

P.S. Там кстати на схемке видно как через директиву .include можно включать модели CMOS-ов от cmosedu

Кстати график зависимости выходного напряжения от выходного по ихнему называется "voltage transfer curve"

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Начинаю вывешивать: viewtopic.php?t=10888Lavr wrote:Ну а у нас - "переходная характеристика", по-моему близко по смыслу,Shaos wrote:Кстати график зависимости выходного напряжения от выходного по ихнему называется "voltage transfer curve"

если перевести дословно, пожалуй, будет "переносная".

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Вот ещё пара курв:Shaos wrote:Начинаю вывешивать: viewtopic.php?t=10888Lavr wrote:Ну а у нас - "переходная характеристика", по-моему близко по смыслу,Shaos wrote:Кстати график зависимости выходного напряжения от выходного по ихнему называется "voltage transfer curve"

если перевести дословно, пожалуй, будет "переносная".

Это соответственно NAND и NOR (синяя кривая это когда оба входа соединены вместе, а зеленоватые - это когда один из входов прицеплен к питанию в с лучае NAND или к земле в случае NOR).

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Использование стандартных КМОП микросхем и КМОП тран...

Тут ещё такая штука - в DG403 есть защита от одновременного замыканий половинок переключателя, причём как я понял и по уровню, и по времени - т.е. нормально разомкнутый ключ не замкнётся, пока не откроется нормально замкнутый, и наоборот. В нашем случае, когда на вход переключателей может подаваться +5В или -5В (для того чтобы сделать из троичного переключателя скажем троичный инвертор), это важно дабы исключить КЗ, а пока все городёжки со схемами управления выдают управляющие сигналы, которые кратковременно пересекаются по времени из-за задержек, хотя тесты на LTspice и не показывают большие токи в момент переключения...Shaos wrote: Пересчитал более внимательно - если входные троичные сигналы разбивать на 4 двоичных, а каждый троичный мультиплексор будет состоять из 8 транзисторов (как я и рисовал до этого - 4 выключателя, соединённых как 3 переключателя), то потребуется 3*(8+8)+12*8 = 48+96 = 144 транзистора. На самом деле если мультиплексоров намного больше чем входов, то лучше разбивать входные троичные сигналы на 6 двоичных - при этом каждый троичный мультиплексор будет состоять только из 6 транзисторов (3 выключателя), тогда потребуется 3*(8+12+4)+12*6 = 72+72 = 144 транзистора (хм, видимо такое упрощение будет работать только для очень больших схем). Потом если выкинуть шесть инверторов, введённых "для крутизны фронтов", то уже получается 132 vs 126 транзисторов. Кроме того NAND/NOR можно заменить на инверторы с модифицированными транзисторами во втором крыле - тогда количество транзисторов уменьшится ещё на 6 и станет 126 vs 120...

P.S. 120 транзисторов это 60 CMOS-пар - 60 корпусов ALD1115, 30 корпусов ALD1105 или 20 корпусов CD4007 (на самом деле больше, т.к. в CD4007 два из шестри транзисторов могут быть использованы только как инвертор либо как часть NOR или NAND), напомню также, что троичный полный сумматор можно построить всего лишь на 12 микросхемах DG403 (в каждой из них 2 нормально замкнутых CMOS-ключа и 2 нормально разомкнутых CMOS-ключа, а также "встроенный" преобразователь из троичного в двоичный сигнал управления ключами).

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

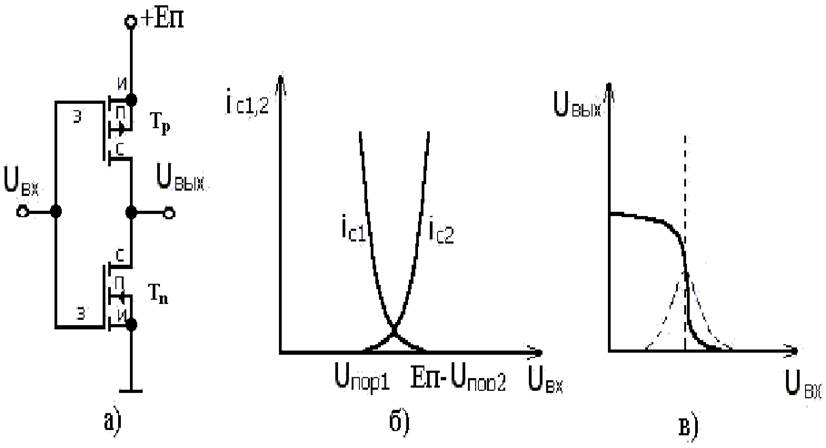

В этих наших интернетах считают, что оптимальная характеристика должна выглядеть ну хотя бы вот так:Shaos wrote:Начинаю вывешивать: viewtopic.php?t=10888

Оптимальная форма передаточной характеристики достигается при одинаковых параметрах транзисторов: у них должна быть одинаковой крутизна входных характеристик Sn = Sp (S = dIc / dUзи при Uси = const). Пороговое напряжение n-канального возбуждающего МОП с индуцированным каналом должно быть приблизительно равно (по модулю) напряжению отсечки р-канального нагрузочного МОП.

iLavr

-

Lavr

- Supreme God

- Posts: 17017

- Joined: 21 Oct 2009 08:08

- Location: Россия

Ссылки в студию на эти "все книжки"!Shaos wrote:во всех книжках написано, что оптимальная характеристика будет, если верхний транзистор примерно в 2 раза больше нижнего

Дело не в размерах, а в том, чтобы приоткрыты они были оба минимальное время.

Следовательно, дело в порогах. Как они выбраны.

iLavr

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Ну вот например:

Далее про CMOS VLSI в другом топике:

viewtopic.php?t=218&postdays=0&postorder=asc&start=18

Далее про CMOS VLSI в другом топике:

viewtopic.php?t=218&postdays=0&postorder=asc&start=18

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Re: Использование стандартных КМОП микросхем и КМОП тран...

Вот попробовал сделать схему управления таким "безопасным" (т.е. без коротких замыканий коммутируемых входов) троичным ключом на 24 транзисторах:Shaos wrote:Тут ещё такая штука - в DG403 есть защита от одновременного замыканий половинок переключателя, причём как я понял и по уровню, и по времени - т.е. нормально разомкнутый ключ не замкнётся, пока не откроется нормально замкнутый, и наоборот. В нашем случае, когда на вход переключателей может подаваться +5В или -5В (для того чтобы сделать из троичного переключателя скажем троичный инвертор), это важно дабы исключить КЗ, а пока все городёжки со схемами управления выдают управляющие сигналы, которые кратковременно пересекаются по времени из-за задержек, хотя тесты на LTspice и не показывают большие токи в момент переключения...Shaos wrote: Пересчитал более внимательно - если входные троичные сигналы разбивать на 4 двоичных, а каждый троичный мультиплексор будет состоять из 8 транзисторов (как я и рисовал до этого - 4 выключателя, соединённых как 3 переключателя), то потребуется 3*(8+8)+12*8 = 48+96 = 144 транзистора. На самом деле если мультиплексоров намного больше чем входов, то лучше разбивать входные троичные сигналы на 6 двоичных - при этом каждый троичный мультиплексор будет состоять только из 6 транзисторов (3 выключателя), тогда потребуется 3*(8+12+4)+12*6 = 72+72 = 144 транзистора (хм, видимо такое упрощение будет работать только для очень больших схем). Потом если выкинуть шесть инверторов, введённых "для крутизны фронтов", то уже получается 132 vs 126 транзисторов. Кроме того NAND/NOR можно заменить на инверторы с модифицированными транзисторами во втором крыле - тогда количество транзисторов уменьшится ещё на 6 и станет 126 vs 120...

P.S. 120 транзисторов это 60 CMOS-пар - 60 корпусов ALD1115, 30 корпусов ALD1105 или 20 корпусов CD4007 (на самом деле больше, т.к. в CD4007 два из шестри транзисторов могут быть использованы только как инвертор либо как часть NOR или NAND), напомню также, что троичный полный сумматор можно построить всего лишь на 12 микросхемах DG403 (в каждой из них 2 нормально замкнутых CMOS-ключа и 2 нормально разомкнутых CMOS-ключа, а также "встроенный" преобразователь из троичного в двоичный сигнал управления ключами).

Слева имеется 4 инвертора с разнесёнными порогами срабатывания, формирующие 2 зазора - между N и O, а также между O и P, далее с помощью двух инверторов и одного ИЛИ-НЕ формируются непосредственно сигналы управления тремя аналоговыми ключами:

Слева выходы входных инверторов, а справа - положительные сигналы управления тремя ключами (EQP,EQO,EQN).

Отрицательные (NEP,NEO,NEN) не показываю - они просто инвертированы относительно первых трёх.

P.S. Выходит, что один троичный сигнал тут превращается аж в ШЕСТЬ двоичных

-

Shaos

- Admin

- Posts: 25070

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Можно ещё придумать схему запрета срабатывания ключа O, если сигнал достаточно быстро перешёл из N в P или из P в N (в этом случае по вышеприведённой схеме будет кратковременное срабатывание ключа O) - например цепочка из инверторов будет делать задержку, после которой выход цепи управления ключом O будет отправляться непосредственно на ключ O, исключая ложное кратковременное срабатывание.