Shaos wrote:

Есть идея назвать этот автоматический подход "DDT" (DG403+DG403=Ternary) logic. Соответственно среду разработки назвать также - DDT...

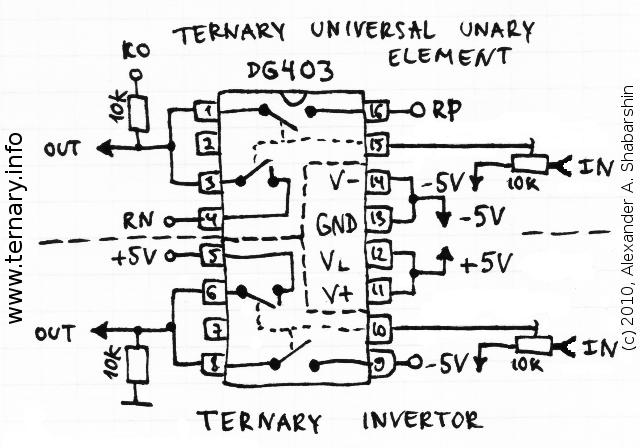

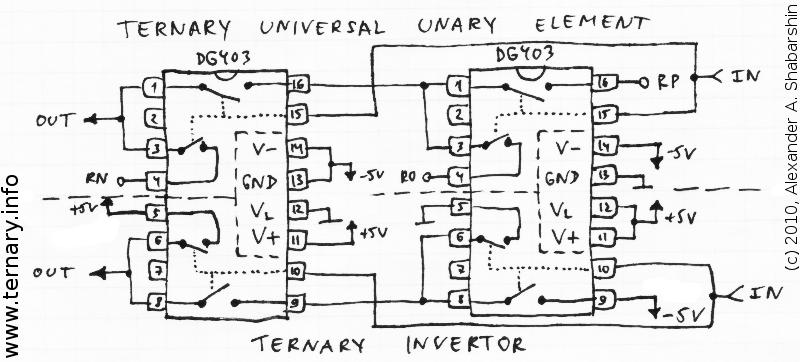

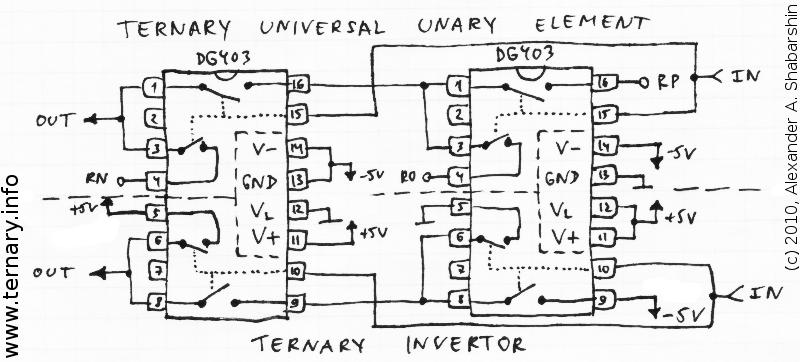

Левое подключение микросхемы DG403 назовём E12 (в случае инвертора это NEN), а правое - E21 (в случае инвертора это EQP). Соответственно имея две микросхемы DG403, подключенные подобным образом, мы получаем пару базовых элементов E12 и пару базовых элемента E21. Название обусловлено видом таблицы соответствия - XYY для E12 и XXY для E21 (где X и Y могут принимать отличные друг от друга значения N,O или P). Вот как выражаются все унарные троичные функции через базовые E12 и E21:

Code: Select all

all ternary functions of one argument:

NNN = N

NNO = SHD(x) = E21(x,N,O)

NNP = E21(x,N,P)

NON = MUX(x,N,O,N) = E12(x,N,E21(x,O,N))

NOO = BLP(x) = E12(x,N,O) // analog of reverse diode

NOP = x // or buffer MUX(x,N,O,P) = E12(x,N,E21(x,O,P))

NPN = MUX(x,N,P,N) = E12(x,N,E21(x,P,N))

NPO = MUX(x,N,P,O) = E12(x,N,E21(x,P,O))

NPP = E12(x,N,P)

ONN = NHI(x) = E12(x,O,N)

ONO = MUX(x,O,N,O) = E12(x,O,E21(x,N,O))

ONP = MUX(x,O,N,P) = E12(x,O,E21(x,N,P))

OON = E21(x,O,N)

OOO = O

OOP = BLN(x) = E21(x,O,P) // analog of forward diode

OPN = ROU(x) = MUX(x,O,P,N) = E12(x,O,E21(x,P,N))

OPO = MUX(x,O,P,O) = E12(x,O,E21(x,P,O))

OPP = SHU(x) = E12(x,O,P)

PNN = NTI(x) = E12(x,P,N)

PNO = ROD(x) = MUX(x,P,N,O) = E12(x,P,E21(x,N,O))

PNP = MUX(x,P,N,P) = E12(x,P,E21(x,N,P))

PON = NOT(x) = MUX(x,P,O,N) = E12(x,P,E21(x,O,N))

POO = E12(x,P,O)

POP = MUX(x,P,O,P) = E12(x,P,E21(x,O,P))

PPN = PTI(x) = E21(x,P,N)

PPO = PHI(x) = E21(x,P,O)

PPP = P

где MUX - универсальный троичный элемент, составленный из одной E12 и одной E21 (как видно на верхней части картинки MUX(c,n,o,p) = E12(c,n,E21(c,o,p)) ), NOT - троичное отрицание (строится из одного MUX), ROU - функция "Round-Up" (строится из одного MUX), ROD - функция "Round-Down" (строится из одного MUX). Функции NOT, ROU и ROD выделены отдельно, т.к. встречаются достаточно часто и могут быть визуально распознаны.

P.S. 12 июля выделил пару новых функций BLP (Block Positive) и BLN (Block Negative), т.к. их реализация может быть совсем простой - один диод и один резистор.

P.P.S. Из бинарных функций по видимому надо выделять MIN и MAX.