"МПИ-интерфейс" это Q-busKolAnVi wrote:Вот схема картриджа памяти для БК-шки. Эмулирует МПИ интерфейс (ГОСТ 26765.51-86)

Также немного по нему есть в книге О.Н.Лебедева "Применение микросхем памяти в электронных устройствах"

http://kolanvi.nm.ru/8.gif

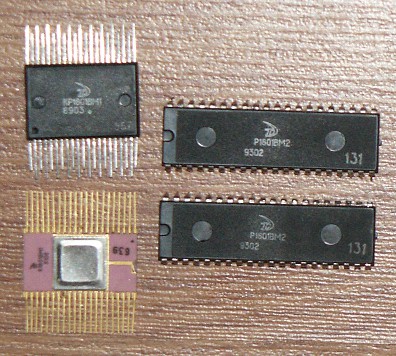

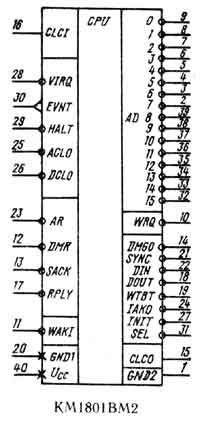

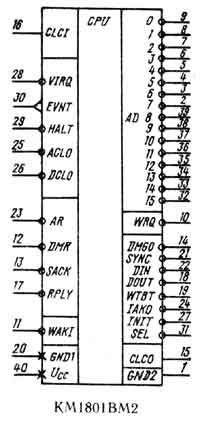

КМ1801ВМ2

Moderator: Shaos

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

KolAnVi

- Fanat

- Posts: 79

- Joined: 27 May 2011 04:25

- Location: Perm

На вики упоминается про 1Мб модули. Попытка поиска картинок привела к http://www.compsy.de/moduls/dmodul3.htm. Там есть фотки с кучей-кучей микросхем... Это к тому что 512 байтные рамины с родным для subj интерфейсом - как-то это печально все;) (КР573РУ11 - 256x16, К1809РУ1 - 1Kx16). Их лучше оставить для восстановления какого старого железа, а если и мутить новодел самодельный, то на DDR (...и ПЛИС, ага)... шутка))) на SRAM, EDO или cache, как минимум.Shaos wrote:"МПИ-интерфейс" это Q-bus

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

-

Lavr

- Supreme God

- Posts: 16986

- Joined: 21 Oct 2009 08:08

- Location: Россия

-

KolAnVi

- Fanat

- Posts: 79

- Joined: 27 May 2011 04:25

- Location: Perm

Насчет плис шутка была... точнее насчет DDR;)Случайность wrote:я вот лично и хочу только ориганальные микросхемы. плисины для меня хуже ругательства.

меня устроит полностью настоящий килобайт 1809ру1.

больше и не надо. зато никаких богомерзких плис пик и авр

По поводу оригинального набора... Для организации шины достаточно соединить двадцать один проводок от проца до микросхемы памяти... и до второй... и до третей... и так до 128-ой. Без всяких дешифраторов.

В чем тут фан? Это слишком легко. И будет работать(при исправных микросхемах).

Соединить subj с обычными 8-и битными КР573РУ (т.е. SRAM) или К565РУ5/РУ7 (-> EDO) - задачка повеселее. Если только решать ее самостоятельно, а не подглядывать в схемы от УКНЦ/ДВК/БК-0010/0011.

А вот сочинить эмулятор К1801РР1, состоящий из ATMEGA8A и двух буферов 74HCT373, умещающийся на платке размером с сам ROM - вот это я понимаю, доказать себе что-то, так доказать! ;)

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

А смысл что то доказывать? Да и для кого?

Судя по мануалу без доп дешифраторов можно соеденить только 32 1809РУ1

Но нужно понять как соеденить.

А ведь еще надо 1801РР1 7-сегментные индикаторы и клавиатуру на 16 кнопок присоеденить.

Может для знающего это легко Но я не знаю и пытаюсь разобраться и понять как это сделать

Судя по мануалу без доп дешифраторов можно соеденить только 32 1809РУ1

Но нужно понять как соеденить.

А ведь еще надо 1801РР1 7-сегментные индикаторы и клавиатуру на 16 кнопок присоеденить.

Может для знающего это легко Но я не знаю и пытаюсь разобраться и понять как это сделать

-

KolAnVi

- Fanat

- Posts: 79

- Joined: 27 May 2011 04:25

- Location: Perm

1801РР1 также подключается. Ее адрес задается при программировании. Причем если сами данные в микросхеме можно стереть, то биты адреса запрограммированные - в начальное состояние уже не вернуть.

У КР537РУ11 - 7 конфигурационных бит адреса, у 1809РУ1 - 5 бит.

Если бы бит было больше, можно было до 794 микросхем подрубить конфигурируемых.

Про перефирию - это да. Сродни подключению обычно памяти. Хотя наверняка есть ведь периферийные контроллеры. Да одназаначна. Почему не хочешь их использовать?

У КР537РУ11 - 7 конфигурационных бит адреса, у 1809РУ1 - 5 бит.

Если бы бит было больше, можно было до 794 микросхем подрубить конфигурируемых.

Про перефирию - это да. Сродни подключению обычно памяти. Хотя наверняка есть ведь периферийные контроллеры. Да одназаначна. Почему не хочешь их использовать?

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

судя по глючности РУ1 придется заказать их коробочку. Дорогие правда.

Выбор элементной базы в том что советские и керамика. тех ИС что не существует в керамике придется использовать пластик.

Думаю со всем этим разберусь потихоньку.

по поводу переферийный ИС врят ли есть что то для 7 сегментного индикатора и 16 кнопочной клавы. а если лепить из 180ВП1 что есть то выходит таже самая МС1201.хх

Выбор элементной базы в том что советские и керамика. тех ИС что не существует в керамике придется использовать пластик.

Думаю со всем этим разберусь потихоньку.

по поводу переферийный ИС врят ли есть что то для 7 сегментного индикатора и 16 кнопочной клавы. а если лепить из 180ВП1 что есть то выходит таже самая МС1201.хх

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

-

KolAnVi

- Fanat

- Posts: 79

- Joined: 27 May 2011 04:25

- Location: Perm

Понятно. Для тебя в данном проекте также важен результат на выходе - некий артобъект.Случайность wrote:Выбор элементной базы в том что советские и керамика. тех ИС что не существует в керамике придется использовать пластик.

А кого-то интересуют задачки из серии как бы так это по новому все соединить, как никто еще не соединял! )))

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

-

Случайность

- Doomed

- Posts: 493

- Joined: 05 Apr 2011 12:45

- Location: Великий Новгород

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

Стандартное отображение процессора на схемах:

Наименование большинства сигналов дословно повторяет сигналы Q-bus из PDP-11 (который LSI-11):

VIRQ - по видимому запрос прерывания (в PDP-11 их несколько с разными приоритетами);

EVNT - прерывание от внешнего события (в PDP-11 это прерывание с частотой сети 50 Гц или 60 Гц);

HALT - ввод процессора в состояние HALT (запуск специальной программы отладки);

ACLO - "AC low" (в LSI-11 этому сигналу соответствует BPOK) - участвует в процессе включения;

DCLO - "DC low" (в LSI-11 этому сигналу соответствует BDCOK) - участвует в процессе включения;

AR - адрес принят (в LSI-11 нету) - участвует в циклах обмена с шиной (проц не будет выдавать DIN/DOUT пока не получит этот сигнал от периферии);

DMR - вход запроса режима DMA от девайса, который потом будет ждать DMGO;

SACK - вход подтверждения режима DMA от девайса в ответ на DMGO;

RPLY - ответ памяти на DIN или DOUT;

WAKI - разрешения обмена с окном (в LSI-11 нету);

AD0...AD15 - мультиплексированная шина данных и адреса;

WRQ - запрос обмена с окном (в LSI-11 нету);

DMGO - выход одобрения DMA от процессора (в ответ на DMR);

SYNC - сигнализирует, что на мультиплексированной шине можно взять адрес;

DIN - выход управления означающий цикл чтения;

DOUT - выход управления означающий цикл записи;

WTBT - сигнализирует о записи отдельного байта (кроме того находится в 0 при выдаче адреса);

IAKO - выход подтверждения прерывания (в ответ на IRQ);

INIT - выход для инициализации периферии;

SEL - запрос стартового адреса (в LSI-11 нету);

CLCI и CLCO - вход и выход тактирования (в LSI-11 такого нету).

P.S. Вот описание всех процессоров 1801: http://vak.ru/doku.php/proj/bk/1801vm-series

P.P.S. Ещё интересная инфа про старт ВМ1 и ВМ2:

Наименование большинства сигналов дословно повторяет сигналы Q-bus из PDP-11 (который LSI-11):

VIRQ - по видимому запрос прерывания (в PDP-11 их несколько с разными приоритетами);

EVNT - прерывание от внешнего события (в PDP-11 это прерывание с частотой сети 50 Гц или 60 Гц);

HALT - ввод процессора в состояние HALT (запуск специальной программы отладки);

ACLO - "AC low" (в LSI-11 этому сигналу соответствует BPOK) - участвует в процессе включения;

DCLO - "DC low" (в LSI-11 этому сигналу соответствует BDCOK) - участвует в процессе включения;

AR - адрес принят (в LSI-11 нету) - участвует в циклах обмена с шиной (проц не будет выдавать DIN/DOUT пока не получит этот сигнал от периферии);

DMR - вход запроса режима DMA от девайса, который потом будет ждать DMGO;

SACK - вход подтверждения режима DMA от девайса в ответ на DMGO;

RPLY - ответ памяти на DIN или DOUT;

WAKI - разрешения обмена с окном (в LSI-11 нету);

AD0...AD15 - мультиплексированная шина данных и адреса;

WRQ - запрос обмена с окном (в LSI-11 нету);

DMGO - выход одобрения DMA от процессора (в ответ на DMR);

SYNC - сигнализирует, что на мультиплексированной шине можно взять адрес;

DIN - выход управления означающий цикл чтения;

DOUT - выход управления означающий цикл записи;

WTBT - сигнализирует о записи отдельного байта (кроме того находится в 0 при выдаче адреса);

IAKO - выход подтверждения прерывания (в ответ на IRQ);

INIT - выход для инициализации периферии;

SEL - запрос стартового адреса (в LSI-11 нету);

CLCI и CLCO - вход и выход тактирования (в LSI-11 такого нету).

P.S. Вот описание всех процессоров 1801: http://vak.ru/doku.php/proj/bk/1801vm-series

P.P.S. Ещё интересная инфа про старт ВМ1 и ВМ2:

из которой я делаю вывод, что DCLO и ACLO это тоже самое, что BDCOK и BPOK в LSI-11 (обозначил это чуть выше в описании сигналов).>> >hello,the startup procedure of those processors is rather

>> >sophisticated,here here is what I have found:

>> >first it is for the k1801BM1 and BM2:

>> >*at beginning if times everything is at zero....(DCLO,ACLO are low)

>> >*when you apply power to the processor and the clock the clock starts

>> >immediatly and the processor begins to count clock states also

>> >*DCLO must be low for 5 ms at least ,during this time the processors

>> >clears the registers,that contain random data at powerup,at the end if

>> >this period internal INIT goes hight ,the processor begins to work

>> >*ACLO should be low for 70 ms

>> >*after there arre differences in the processors:

>> >*the 1801BM1 find the msb of the pc from address 177716(selected by

>> >SEL1),the lsb of

>> >the pc is filled with zeroes,this forms the starting address .Ths PSW is

>> >filled with value 340.This addres is in the I/O page,maybe it can be

>> >physically in a small rom,

>> >a register bank ,or in support circuit???

>> >*for the1801BM2 the msb of the pc from a non address register (maybe a

>> >74ls 244 programmed by a bank of switches as in the case of the

>> >T11),selected by SEL ,the lsb is filled by zeros ,this fixes the

>> >starting

>> >address in rom,the PSW is found at this addess +2

-

Shaos

- Admin

- Posts: 25031

- Joined: 08 Jan 2003 23:22

- Location: Silicon Valley

А вот интересно - зачем они в ВМ2 воткнули этот AR? Его небыло в ВМ1 (и вроде как нет в ВМ3). Его небыло в LSI-11 (и соответственно в Q-bus). Более того - его нету и в ГОСТе на МПИ! Тогда НАФИГА этот лишний сигнал подтверждения в процессоре, который как бы реализует именно МПИ (Q-bus)?Shaos wrote: AR - адрес принят (в LSI-11 нету) - участвует в циклах обмена с шиной (проц не будет выдавать DIN/DOUT пока не получит этот сигнал от периферии)

P.S.

Эта схема НЕ будет работать с ВМ2, т.к. она НЕ реализует сигнал AR (адрес принят), отсутствующий в стандарте МПИ (Q-bus). Возможно и "родные" микросхемы памяти тоже работать не будут, если они под ВМ1 заточены, а не под ВМ2. А вот на PAL/GAL думаю относительно просто будет всю эту логику реализовать...KolAnVi wrote:Вот схема картриджа памяти для БК-шки. Эмулирует МПИ интерфейс (ГОСТ 26765.51-86)

Также немного по нему есть в книге О.Н.Лебедева "Применение микросхем памяти в электронных устройствах"

http://kolanvi.nm.ru/8.gif

P.P.S. Вот тут: http://www.emuverse.ru/wiki/%D0%9A573%D0%A0%D0%A43 (К573РФ3)

есть косвенное подтверждение, что озвученные выше микросхемы памяти не содержат вывода AR:

P.P.P.S. Сигнал AR по видимому можно получить на инверсном выходе RS-триггера, взводимого от SYNC и сбрасываемого по RPLY, также ещё потребуется некоторая логика т.к. SYNC и RPLY могут быть нулевыми одновременно и это значит что схема уже не будет содержать просто проц и несколько просто родных памятей...Назначение выводов К573РФ3 1 — вход сигнала чтения; 2 — выход сигнала ответа; 3 — вход сигнала синхронизации; 4, 5, 6, 7, 8, 9, 10, 11 — вход (выход) 4, 5, 6, 7, 8, 9, 10, 11 разрядов адреса-данных; 12 — общий; 13, 14, 15, 16 — вход (выход) 3, 2, 1, 0 разрядов адреса-данных; 17, 18, 19, 20 — вход (выход) 12, 13, 14, 15 разрядов адреса-данных; 21 — напряжение питания (Uп2, Upr); 22 — сигнал запись-считывание; 23 — сигнал выбора микросхем; 24 — напряжение питания (Uп1)

.....

Микросхема совместима по разводке выводов и сигналам с микросхемами КР537РУ11, К1809РУ1, К1809РЕ1, К1801РЕ1, К1801РЕ2, КР588РЕ1, что делает возможным создание универсальных модулей ЗУ на основе стандартного параллельного магистрального интерфейса с объединенной шиной адреса и данных.